Fターム[5F043AA13]の内容

ウェットエッチング (11,167) | 被エッチング体 (2,299) | 半導体基板以外の半導体層 (313) | 単層構造 (281) | 3−5族 (163)

Fターム[5F043AA13]の下位に属するFターム

Ga−As系 (23)

In−P系 (15)

その他のIII−V族 (111)

Fターム[5F043AA13]に分類される特許

1 - 14 / 14

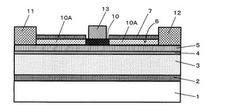

半導体装置及びその製造方法、電源装置

【課題】チャネル領域の低抵抗化を図りながら、ノーマリオフを実現する。

【解決手段】半導体装置を、キャリア走行層3及びキャリア供給層5を含む窒化物半導体積層構造と、窒化物半導体積層構造の上方に設けられ、活性化領域10と不活性領域10Aとを有するp型窒化物半導体層6と、p型窒化物半導体層の不活性領域上に設けられたn型窒化物半導体層7と、p型窒化物半導体層の活性化領域の上方に設けられたゲート電極13とを備えるものとする。

(もっと読む)

窒化物半導体装置

【課題】ウェットエッチングの際に所定の位置で確実にエッチストップすることができる構造を提供する。

【解決手段】電流狭窄層(窒化物半導体層3)と接しており、かつ電流狭窄層(窒化物半導体層3)よりも基板1側に位置する窒化物半導体層2に遷移金属を導入する。窒化物半導体層2がn型導電型の場合は正孔を捕獲する準位を形成する遷移金属(Ti)、またp型導電型の場合は電子を捕獲する準位を形成する遷移金属(Cu)を導入する。この構成に対して、PECエッチングを行うと、電流狭窄層(窒化物半導体層3)と窒化物半導体層2の界面近傍で確実なエッチストップが得られ、デバイス特性の安定化が可能である。

(もっと読む)

II−VI族またはIII−V族化合物系半導体発光素子用エピタキシャルウエハ、および、その製造方法

【課題】光取り出し効率を向上できるとともにクラックの低減ができる発光素子用エピタキシャルウエハの製造方法を提供する。

【解決手段】発光素子用エピタキシャルウエハの製造方法は、II-VI族またはIII-V族化合物系半導体からなる複数の半導体層がエピタキシャル成長され積層されたエピタキシャル層を含む発光素子用エピタキシャルウエハの製造方法であって、エピタキシャル成長されたウルツ鉱結晶体のC軸方向に沿って積層され複数の半導体層を形成するエピタキシャル工程と、複数の半導体層の最上部に形成された半導体層の表面を−C面とする工程と、−C面に複数の多角形凹凸からなる隆起面を形成する隆起工程と、隆起面における複数の多角形凹凸の各々の差し渡しより小なる差し渡しを各々が有しかつ隣接する複数の突起を、隆起面に形成する粗面化工程と、を含み、隆起工程において、複数の多角形凹凸を、ウルツ鉱結晶体のm面に垂直な方向以外に伸長する複数の稜線を有するように形成する工程を含む。

(もっと読む)

発光デバイスおよびその製造方法

【課題】発光光の取り出し効率を高めることが可能な発光デバイスおよびその製造方法を提供する。

【解決手段】一導電型半導体層と逆導電型半導体層とが積層されてなる、前記一導電型半導体層と前記逆導電型半導体層との境界を含む発光部分を有する発光構造体と、前記発光構造体の上面と接合した電流拡散層と、前記電流拡散層の上側面に被着された電極層とを有し、前記電極層は、前記境界の周縁線よりも外側領域に配置されていることを特徴とする発光デバイスを提供する。

(もっと読む)

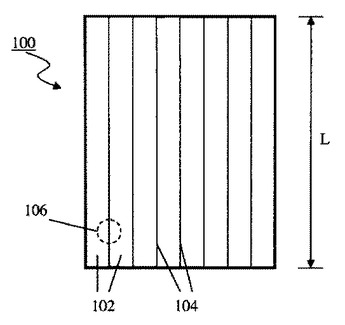

半導体薄膜の製造方法及び半導体装置の製造方法

【課題】半導体薄膜を基板上に形成した後剥離する方法において、剥離のためのエッチング液の浸透速度が高く、エッチング速度の均一性を高め、短時間で良好な半導体薄膜を得ることができるようにする。

【解決手段】半導体薄膜(20)が基板(11)上にあるときに、複数の半導体薄膜(20)を互いに連結して支持するための連結支持体(90)を設ける。連結支持体(90)は、シート状部分(91)と、シート状部分(91)と半導体薄膜(20)との間に空隙を設けるためのスペーサ部(92)とを備えており、この隙間(20)が、基板(11)の面に平行な方向にエッチング液を通過させる。

(もっと読む)

半導体光素子の製造方法

【課題】除去可能な突起物を把握でき、半導体層の表面から突出する突起物を適切に除去することができる半導体光素子の製造方法を提供する。

【解決手段】この半導体光素子の製造方法では、表面処理工程において、エッチングによってキャップ層5の表面から除去される突起物は、キャップ層5の表面に形成されたレジスト層22の厚さよりも高い突起物A1,C2に限定される。したがって、形成するレジスト層22の厚さに基づいて、除去可能な突起物の高さを予め把握できるので、過不足のないエッチングによって、キャップ層5の表面から突出する突起物を適切に除去できる。レジスト層22の厚さを変えながらステップS11〜S17を繰り返すことにより、ウエハの不必要なエッチングを防止しつつ、突起物をより完全に除去できる。

(もっと読む)

III−V族半導体基板からのバルク金属汚染の除去方法

【課題】III−V族半導体基板からバルク金属汚染を除去するための単一工程の方法を提供する。

【解決手段】該方法は、金属汚染したIII−V族半導体基板を、体積比x:y H2SO4:H2O2(xは3〜9、yは1)を有する硫酸および過酸化物の混合物の中に浸漬することを含む。本発明の実施形態に係る方法を用いてIII−V族半導体基板を処理した後、バルク金属汚染は、基板からほぼ完全に除去できるとともに、処理後の基板の表面粗さは、2μm×2μmの表面グリッドに関して0.5nmRMS未満とすることができる。本発明は、半導体デバイスを製造する更なる処理ステップを実施する前に、本発明の実施形態に係るバルク金属汚染を除去する方法を用いて、半導体デバイスを製造するための方法を提供する。

(もっと読む)

窒化物半導体ウェハ及び薄膜半導体装置の製造方法

【課題】非透明な基板上に形成した窒化物化合物半導体層を化学的なエッチング処理によって基板から剥(はく)離させることにより、基板を再利用することができるようにする。

【解決手段】基板と、該基板上に形成されたIII-V 族の窒化物化合物半導体層と、前記基板と窒化物化合物半導体層との間に形成されたAlx Ga1-x As層(x≧0.6)とを有する。

(もっと読む)

窒化物系半導体素子の製造方法

【課題】窒化物系半導体基板などの窒素面と電極とのコンタクト抵抗を低減することが可能な窒化物系半導体素子の製造方法を提供する。

【解決手段】この窒化物系半導体レーザ素子の製造方法は、ウルツ鉱構造を有するn型GaN基板1の裏面(窒素面)をRIE法によりエッチングする工程と、その後、エッチングされたn型GaN基板1の裏面(窒素面)上に、n側電極8を形成する工程とを備えている。

(もっと読む)

流体メニスカスを使う湿式処理装置および方法

対象物の表面の少なくとも一部を処理するための流体メニスカスを利用する湿式処理装置および方法である。対象物の表面の1つが処理された後に、対象物の他の側面または表面が同様に処理されうる。いくつかの例を挙げれば、この処理はコーティング、エッチング、めっきでありうる。この装置と方法の用途は、半導体処理産業、特にウェハおよび基板の処理にある。この方法と装置は、電子構成部品の多数の表面の処理をも可能にする。 (もっと読む)

エッチングプロセスと堆積プロセスを用いて改善された薄膜太陽電池相互接続部を製造する方法

本発明は、太陽光発電モジュールにおいて相互接続部を形成する方法を提供する。一態様によれば、本発明の方法は、従来の集積回路製造に行われたものと同様の処理ステップを含む。例えば、前記方法は、マスキングとエッチングをして、セルの間にアイソレーション溝を形成するステップと、追加エッチングして、セルの間に相互接続部を形成するために使用し得る溝に隣接した導電性段差を形成するステップとを含むのがよい。他の態様によれば、導電性段差を形成するための方法は、例えば、モジュールの上にミラーを位置決めして、フォトレジストを基板の下からある角度で一回以上露光し、エッチングして、導電性段差を露光することにより、自己整合させることができる。他の態様によれば、プロセスは、モジュールにおいてグリッド線を形成して、構造における電流輸送を改善する段差を含むことができる。  (もっと読む)

(もっと読む)

発光素子及びその製造方法

【課題】 光取り出し効率の向上が図られ、新規な構成を有する発光素子を提供する。

【解決手段】 発光素子は、第1の導電型を有する下側半導体層と、下側半導体層の上に形成された発光層と、発光層の上に形成され、第1の導電型と反対の第2の導電型を有する上側半導体層と、下側半導体層に電気的に接続される下側電極と、上側半導体層に電気的に接続される上側電極とを有し、上側電極は、上側半導体層の上に形成され、上側半導体層の表面を、各々が上側電極で取り囲まれる複数の区画に分割するような網目形状を有し、さらに、区画の少なくとも1つの内部に、底面が少なくとも前記下側半導体層の上面まで達し、開口の縁が上側電極から離れた窪みを少なくとも1つ有する。

(もっと読む)

半導体装置の製造方法

【課題】 リッジ形状部を有する半導体装置の製造において、ドライエッチングに引き続くウェットエッチングを安定して制御して、リッジ形状とリッジ高さを制御する。

【解決手段】 ドライエッチングの反応生成物9を酸化して除去することにより、それに続くウェットエッチングの安定性を向上させて、リッジ形状およびリッジ幅の制御性を向上させることができる。また、ウェットエッチングを必要最小限にとどめることにより、ウェットエッチングによりサイドエッチングを最小限にとどめてリッジ幅を厳密に制御することができる。よって、レーザ光の水平放射角のばらつきが少ない半導体レーザ装置を得ることができる。また、ウェットエッチングは、エッチングストップ層5を利用して停止させることにより、リッジ高さを厳密に制御することができる。

(もっと読む)

電解質に対する半導体構造の局部的な電気化学的ポテンシャルの改変による光電気化学(PEC)的エッチングの制御

選択性が高い光誘導性のエッチングを達成するために、電解質に対する半導体構造の局部的電気化学的ポテンシャルを戦略的に改変することを含む、III−窒化物半導体構造を製造するための方法。上記方法は、電気的抵抗層または半導体構造の中の電子のフローを妨げる層の適切な配置によって、および/またはPECエッチングの間に、半導体構造の特定の層と接触するカソードを配置することによって、半導体構造または半導体デバイスの電気的ポテンシャルを局部的に制御し、水平方向および/または垂直方向の光電気化学(PEC)的エッチング速度を局部的に制御する。  (もっと読む)

(もっと読む)

1 - 14 / 14

[ Back to top ]