Fターム[5F044AA02]の内容

ボンディング (23,044) | ワイヤによるペレット電極との接続構造 (951) | 配線基板との接続 (306)

Fターム[5F044AA02]の下位に属するFターム

基板配線にメッキしているもの (25)

基板配線にボンディングチップがあるもの (12)

基板配線の配置、形状に関するもの (52)

Fターム[5F044AA02]に分類される特許

21 - 40 / 217

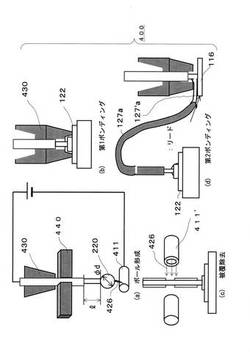

ワイヤボンディング方法、回路装置及び回路装置パッケイジ方法

【課題】マルチチップモジュール構造を有する回路装置の低背化、機能向上、小型化、システム化が可能なワイヤボンディング方法、回路装置及び回路装置パッケイジ方法を提供する。

【解決手段】絶縁膜被覆ワイヤを用いたボンディング方法は、絶縁膜被覆ワイヤの自由端である始端に対して、ボール220を形成するステップ(a)と、この形成されたボールを用いて第1ボンディングを行うステップ(b)と、絶縁膜被覆ワイヤの第1ボンディングを行った部分の被覆の除去を行うとともに絶縁膜被覆ワイヤの終端に対する第2ボンディングを行う部分の被覆の除去を行うステップ(c)と、第2ボンディングを行うステップ(d)とを備える。本発明の回路装置はこのような絶縁膜被覆ワイヤを用いたボンディング方法を利用して作製されたものである。第2ボンディングについても、ボールの形成および被覆の除去を行ってもよい。

(もっと読む)

複合ボンドワイヤ用の方法及びシステム

【課題】集積回路用のボンドワイヤを提示する。

【解決手段】集積回路内で使用する複合ボンドワイヤ110を生産するため、導電材料を溶解し、100ミクロン未満の粒度の粒子材料と混合して混合物を生成する。この混合物を用いて複合ボンドワイヤ110を作製する。内部コア、及びこの内部コアより高い導電率を有する外層を有する複合ワイヤも提供される。この外層は、交流信号を搬送するための動作周波数における表皮深度よりも厚く設計する。

(もっと読む)

半導体チップ、半導体装置、及び半導体チップの製造方法

【課題】2次電池パックの保護回路を更に小型化すること。

【解決手段】本発明に係る半導体チップは、双方向スイッチを構成する2個のパワートランジスタと、抵抗素子とを備える。2個のパワートランジスタのドレイン同士は接続されている。抵抗素子の一端は、2個のパワートランジスタのうち一方のソース電極と電気的に接続され、その他端は、第1外部パッドと電気的に接続されている。それら2個のパワートランジスタと抵抗素子とは、同一の半導体チップ上に形成されている。

(もっと読む)

半導体チップおよび半導体装置

【課題】半導体チップを実装する際のコスト低減、パッケージ基板の小型化、および配線パターンの最適化を実現できる半導体チップを提供することである。

【解決手段】本発明にかかる半導体チップ10は、半導体チップ10に設けられると共に、少なくとも一つの電極パッド6を備える電極パッド群1と、半導体チップ10に設けられる少なくとも一つの電極パッドであって、電極パッド6から出力される信号と同じ信号を出力可能である電極パッド7を備える電極パッド群2と、を備える。そして第1の電極パッド群の一の電極パッドおよび第2の電極パッド群の一の電極パッドうち、当該信号が供給される他の半導体チップの他の電極パッドと距離が近い方の電極パッドが、他の半導体チップの当該他の電極パッドと接続される。

(もっと読む)

パワーデバイス

【課題】ポリイミド膜上に設けた電極パッドに導体バンプなしにAlワイヤを確実に接合でき、ポリイミド膜からの電極パッドの剥離や電極パッドとAlワイヤとの接合不良を防止できるパワーデバイスを提供する。

【解決手段】絶縁基板1上に設けられた半導体素子(2,3,6)と、絶縁基板1上に形成され、半導体素子(2,3,6)を覆う軟質ポリイミド膜11と、軟質ポリイミド膜11上に形成された電極パッド9と、電極パッド9にワイヤボンディングにより一端が接合されたAlワイヤ12とを備える。

(もっと読む)

半導体集積回路装置

【課題】クロストークノイズの抑制及びEMCを強化し、且つ、クロストークノイズの抑制等に用いるスペースを縮小して小型化を可能とする半導体集積回路装置を得られるようにする。

【解決手段】半導体集積回路装置は、実装基板10の上に保持され、半導体集積回路を含む半導体チップ11と、実装基板10の上に形成され、半導体集積回路が処理する信号を伝送する第1の配線1と、半導体集積回路と第1の配線6とを接続する第1のボンディングワイヤ6と、実装基板10の上に形成された複数の第2の配線2と、半導体集積回路と複数の第2の配線2のうちのいずれかとをそれぞれ接続する複数の第2のボンディングワイヤ8とを備えている。第2のボンディングワイヤ8は、第1のボンディングワイヤ6の上方で且つ該第1のボンディングワイヤ6と間隔をおくように互いに交差して形成されている。

(もっと読む)

プラズマ点火装置、プラズマ点火方法、およびプラズマ発生装置

【課題】監視したり人手を要したりすることなく、容易にかつ確実にプラズマを点火した

り再点火したりすることが可能なプラズマ点火技術を提供する。

【解決手段】所定の高周波信号HSを発生しプラズマ発生させるための負荷電極114に

供給する高周波電源装置101、高周波電源装置側と負荷電極側とのインピーダンスを整

合させる整合装置105、高周波信号HSの進行波および反射波を検出する進行波・反射

波検出装置102、所定の高電圧HVを発生する高電圧発生装置103、反射波の進行波

に対する比率が第1のしきい値より大きい場合に高電圧HVを高周波信号HSに重畳する

制御装置100を備える。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】半導体装置の小型化に対応できる半導体装置を提供する。

【解決手段】一面から他面に貫通して設けられた開口部12と、一端が露出された配線19とを有する基板17と、基板17の一面に搭載され、開口部12から露出するように配置された同電位の2以上の電極パッド5を含む電極パッド群15を有する半導体チップ16と、同電位の2以上の電極パッド5を接続するとともに、基板17に配置された1つの配線19の一端と接続する接続部材7とを備える半導体装置10とする。

(もっと読む)

半導体装置

【課題】チップサイズの縮小化や多ビット化に対応した半導体装置を提供する。

【解決手段】第1及び第2チップパッド列4A,4Bの端部よりも外側に位置する第3チップパッド列4Cが、第1チップパッド列4Aと第2チップパッド列4Bとの間の中心線の延長線上に並んで配置されている。これにより、第3チップパッド列4Cを構成するチップパッド4は、第1及び第2チップパッド列4A,4Bを構成するチップパッド4よりも、第1又は第2ボンディングパッド列6A,6Bを構成するボンディングパッド6に対するY方向の距離を大きく確保することができる。したがって、これらチップパッド4とボンディングパッド6との間を接続するボンディングワイヤー7のY方向に対する角度を緩和することが可能である。

(もっと読む)

Alめっき鋼線を用いたワイヤボンディング構造

【課題】振動・衝撃に強く、高強度化されたワイヤボンディング構造を提供する。

【解決手段】鋼芯線の周囲を溶融Alめっき層で被覆した、外径0.08〜0.6mm、長手方向に垂直な断面に占める鋼芯線の面積率が15〜98%であるAlめっき鋼線5によって、電子回路基板1上の導電体4表面同士を接続してなるワイヤボンディング構造。前記導電体表面は、例えばAl、Al合金またはNiである。Alめっき鋼線と導電体表面は例えば超音波接合されている。溶融Alめっき層は、Si:0〜12質量%、残部Alおよび不純物からなるものとすることができる。

(もっと読む)

半導体装置およびその製造方法

【課題】半導体装置の生産性を向上させる。

【解決手段】複数の第1電極11、第2電極12が設けられたプリント基板10と、プリント基板10上に搭載され、上面の外周に沿った第1列L1をなす複数の第1接続パッド21及び第1列L1と平行かつ第1列L1よりも内側に離間した第2列L2をなす複数の第2接続パッド22が設けられた半導体チップ20と、第1電極11、第2電極12と第1接続パッド21、第2接続パッド22とを接続する第1ボンディングワイヤ31、第2ボンディングワイヤ32とを備え、半導体チップ20の電源電圧端子、システムリセット端子は、第1接続パッド21のいずれかが用いられ、複数の第2接続パッド22と接続される第2ボンディングワイヤ32は、複数の第1接続パッド21と接続される第1ボンディングワイヤ31よりも上方に設けられている。

(もっと読む)

センサデバイスの製造方法及びセンサデバイス

【課題】本発明は、湿気の多い外気によるセンサの金属電極の腐食を防止し、かつセンサの樹脂封止によるセンサの反りの発生を防止してセンサ特性への影響を低減するセンサデバイスの製造方法及びセンサデバイスを提供する。

【解決手段】センサデバイスの製造方法は、固定部、前記固定部の内側に位置する可動部、前記固定部と前記可動部を接続する可撓部、及び複数の金属電極を有するセンサを基板上に配置し、前記センサの複数の金属電極及び前記基板の複数の端子をボンディングワイヤにより電気的に接続し、前記複数の金属電極と前記複数の端子の間にある前記ボンディングワイヤの一部が露出するように、前記センサの複数の金属電極の前記ボンディングワイヤと接続された部位を樹脂により覆う。

(もっと読む)

電子装置の製造方法および電子装置

【課題】異物による電子装置の性能の低下を防止するとともに、位置認識マークを正確に認識することのできる電子装置の製造方法を提供する。

【解決手段】配線5を基板2の表面に形成する配線形成工程と、基板2の表面上で電極3と位置認識マーク4を形成する部分を除いて保護膜6を形成する保護膜形成工程と、基板2の表面上で電極3を形成すると共に、位置認識マーク4を電極3及び配線5から離間した位置に形成する電極及びマーク形成工程と、電極3にボンディングワイヤー9を接合させるボンディング工程と、配線5、電極3及び位置認識マーク4を形成した基板2を封止部材10で封止する封止工程とを備える。

(もっと読む)

半導体チップ及び半導体装置

【課題】半導体チップの小型化を妨げず、集積度を低下させずに、Alワイヤによるボンディングが可能な半導体チップ及び半導体装置を提供する。

【解決手段】プリント基板10と、プリント基板10上に搭載され、上面の外周に沿った第1の列L1をなす複数の第1の接続パッド21、及び、第1の列L1と平行かつ第1の列L1よりも内側に離間した第2の列L2をなす複数の第2の接続パッド22が設けられた半導体チップ20と、プリント基板10と半導体チップ20とを接続する第1のボンディングワイヤ31、第2のボンディングワイヤ32とを備える半導体装置1である。第1の列L1をなす第1の接続パッド21と第2の列L2をなす第2の接続パッド22との間には回路素子23、24が設けられている。

(もっと読む)

半導体装置及びその製造方法

【課題】半導体装置におけるワイヤ接続不良の抑制化を図る。

【解決手段】主面3aの外周部に並んで配置された複数のボンディングリード3hを有するパッケージ基板3と、パッケージ基板3の主面3aのボンディングリード列の内側に搭載された半導体チップ1と、半導体チップ1のパッド1cと基板のボンディングリード3hとを接続するワイヤ4と、半導体チップ1及び複数のワイヤ4を樹脂封止する封止体と、パッケージ基板3の裏面に設けられた複数の半田バンプとを有している。さらに、ワイヤ4のループの頂点4bがワイヤ接続部4aより外側に配置されていることにより、ボンディングリード3hと半導体チップ1のパッド1cとの接続においてワイヤ長を長くすることができ、その結果、ワイヤ4のループ形状の安定化を図ってワイヤ接続不良の抑制化を図る。

(もっと読む)

ICモジュール及びこれを使用したICカード

【課題】ボンディングワイヤを完全に被覆したICモジュール及びこれを使用したICカードを提供する。

【解決手段】非導電性の基板の一方の面に金属の薄板による独立した外部端子が接着剤を介して複数形成され、他方の面に接着剤を介してICチップが搭載され、前記ICチップの接続端子と前記基板を貫通する孔から表出した前記外部端子の裏側の金属面がボンディングワイヤで接続され、前記ICチップが搭載された側の前記基板上に、前記ICチップと前記ボンディングワイヤを内包するように封止樹脂が形成されたICモジュールにおいて、前記ICチップの表出面から前記ボンディングワイヤの上端までの距離が、前記ICチップの表出面から前記封止樹脂の上端までの距離の1/2以下としたICモジュール及びこれを使用したICカードを提供する。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】 注入された樹脂によるワイヤ流れやワイヤショートを防止可能な半導体装置の製造方法を提供する。

【解決手段】本発明の半導体装置の製造方法では、半導体チップ109を配線基板100上に搭載し、配線基板100と半導体チップ109とを、第1のワイヤ群120と、前記第1のワイヤ群よりもワイヤ長が短い第2のワイヤ群118とを張設して接続し、第1のワイヤ群120から第2のワイヤ群118に向けて封止樹脂307を注入して半導体チップ109、第1のワイヤ群120、第2のワイヤ群118を覆う封止体401を形成する。

(もっと読む)

半導体装置の製造方法

【課題】パッシベーション膜に形成された開口部から露出するボンディングパッドの表面に導電性部材を接続する半導体装置において、パッシベーション膜に発生するクラックを抑制することができる技術を提供する。

【解決手段】電極層ELの一端とパッドPADの一端との間の平面的な距離(L2)を、電極層ELの一端と開口部OPの一端との間の平面的な距離(L1)よりも大きくする。これにより、ワイヤWの接続位置が電極層ELの端部側にずれる場合であっても、電極層ELの一端とパッドPADの一端との間の平面的な距離(L2)が大きくなっているため、電極層ELの段差部にワイヤWが接続することに起因した応力がパッドPADの端部にまで伝わることを抑制できる。

(もっと読む)

電子機器の製造方法

【課題】ワイヤーの断線を防止することができる高信頼性の電子機器の製造方法を提供する。

【解決手段】実装基板2に封止樹脂4を注入するための封止樹脂注入口9を設ける。この封止樹脂注入口9からワイヤー3方向へ向けて封止樹脂4を注入する。徐々に封止樹脂4の注入作業を続けると、封止樹脂4内に気泡8が発生する。しかしながら、封止樹脂4の注入作業を継続すると、前記気泡8は封止樹脂4の注入方向への流動に伴い前記ワイヤー3上部に押し出され、封止樹脂4がワイヤー3を覆う状態なった時にはワイヤーの上方に移動する。このような状態になれば、熱膨張による部材の伸縮によってワイヤーにダメージを与えることがなくなる。また、上記の状態であれば、ワイヤー3上部に押し出された気泡8をワイヤー3に触れることなく除去することもできる。

(もっと読む)

布製半導体素子のパッケージ及びその製造方法

【課題】着用した際の異物感を最小限に抑えると共に、生産性が向上した布製半導体素子のパッケージ、その布製半導体素子のパッケージの製造方法を提供する。

【解決手段】布製半導体素子のパッケージは、織布と、前記織布上に導電材をパターニングして形成された第1リード部と、を有する布製印刷回路基板と、前記布製印刷回路基板のリード部に接続された電極部を有する半導体素子と、前記布製印刷回路基板と、前記半導体素子とを密封する成形部(molding)と、を含む。前記第1リード部は、前記第1リード部の端部において別の布製半導体素子と電気的に接続された導電性繊維によって前記織布とともに縫合されることにより、あるいは、前記第1リード部は、前記第1リード部の端部において別の布製半導体素子と電気的に接続された布製印刷回路基板の第2リード部と前記織布と共に縫合されることにより、前記別の布製半導体素子と電気的に接続されている。

(もっと読む)

21 - 40 / 217

[ Back to top ]