Fターム[5F044AA02]の内容

ボンディング (23,044) | ワイヤによるペレット電極との接続構造 (951) | 配線基板との接続 (306)

Fターム[5F044AA02]の下位に属するFターム

基板配線にメッキしているもの (25)

基板配線にボンディングチップがあるもの (12)

基板配線の配置、形状に関するもの (52)

Fターム[5F044AA02]に分類される特許

161 - 180 / 217

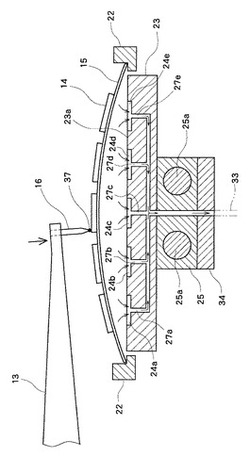

ワイヤボンディング装置における湾曲回路基板の固定方法及びプログラム

【課題】ワイヤボンディング装置における湾曲回路基板の固定方法であって、簡便な方法によって湾曲した回路基板を吸着ステージに効果的に固定する。

【解決手段】回路基板15を吸着する吸着ステージ23の基板吸着面23aに真空吸着キャビティ24a〜24eを設ける。真空装置によって真空吸着キャビティ24a〜24eの空気を排気しながら、ボンディングアーム13の先端に取り付けられたキャピラリ16で回路基板15を押し下げる。回路基板15に少なくとも1つの真空吸着キャビティ24a〜24eの上面をシールさせることによって他の真空吸着キャビティの上面を連鎖的にシールさせる。全ての真空吸着キャビティ24a〜24eの上面を回路基板15でシールして回路基板15を吸着ステージ23に吸着させる。

(もっと読む)

半導体装置およびその製造方法

【課題】高機能化する半導体素子上の電極数に対応する電極数を回路基板に確保しながらも小型化された半導体装置およびその製造方法を提供する。

【解決手段】半導体素子4と、前記半導体素子4を搭載した回路基板1と、前記半導体素子4の上面に形成された複数の電極6と前記半導体素子4の複数の電極6に対応して前記回路基板1の素子搭載部1aの周囲に形成された複数の電極3とを電気的に接続した金属細線7とを有した半導体装置において、前記回路基板1の複数の電極3上に、前記素子搭載部の中央から外周に向かう方向に沿って次第に高くなるように導電性突起物10を形成している。金属細線7間の高低差が拡大し、金属細線7どうしの接触の可能性が小さくなるため、回路基板1の電極面積を低減し、小型化を図りながら、半導体装置の安定した生産が可能となる。

(もっと読む)

電子装置

【課題】素子チップの主表面の可動部を覆うように素子チップにキャップを取り付け、素子チップとボンディングワイヤとを電気的に接続してなるセンサ装置において、キャップとなるウェハに抜き領域を形成したり、キャップに貫通電極を形成することなく、ワイヤと素子チップとを電気的に接続できるようにする。

【解決手段】素子チップ10の主表面10aの可動部11を覆うように、キャップ20を取り付け、素子チップ10の主表面10aの側部に位置する側面10bに、素子チップ10に電気的に接続された側面電極13を設け、この側面電極13にボンディングワイヤ30を接続する。

(もっと読む)

積層コンデンサ及び積層コンデンサの実装構造

【課題】サージ耐電圧を高めることができ、それによって静電気放電に際しての破壊等が生じ難い、信頼性に優れた積層コンデンサを提供する。

【解決手段】セラミック積層体2内に、セラミック層を介して第1,第2の内部電極3,4が重なるように配置されており、セラミック積層体2の外表面に、第1の内部電極に電気的に接続されている第1の外部電極5と第2の内部電極に電気的に接続されている第2の外部電極6と、第3の外部電極7A、7Bとが形成されており、第1の内部電極3と、第2の内部電極4とに異なる電位が接続されるように構成されており、第3の外部電極が、第1,第2の内部電極のいずれにも電気的に接続されておらず、かつ第1,第2の外部電極5,6間に位置する電極部分を有するようにセラミック積層体2の外表面に形成されており、第3の外部電極からサージ電流が逃がされるように構成されている、積層コンデンサ。

(もっと読む)

半導体装置又はセンサ装置

【課題】プリント基板上に突合わせはんだ付けされたパッケージ1内に設けられた半導体装置又はセンサ装置を改良して、突き合わせはんだ付けされたパッケージ内において、温度変化によって限定された、半導体装置又はセンサ装置の曲げ応力を減少させる。

【解決手段】少なくとも幾つかの接続面2が全面的にはんだ付けされておらず、これらの全面的にはんだ付けされていない接続面2が、第1の面領域7内で導体路5の区分に堅固にはんだ付けされていて、第2の面領域10内でプリント基板に緩く結合されており、堅固にはんだ付けされた面領域7が、プリント基板に緩く結合された面領域10よりも、接触しようとする半導体構造体又はセンサ構造の近くに位置している。

(もっと読む)

半導体装置およびワイヤボンディング最適化方法

【課題】パッケージに対するチップの実装位置ずれが生じた場合に、ボンディングワイヤ間のショートを回避するワイヤボンディング最適化方法および半導体装置を提供する。

【解決手段】半導体チップ1のパッド2とパッケージ基板のボンディングポイントBPとを接続するワイヤボンディングにおいて、半導体チップ辺上のいずれかのパッドに対してボンディングポイントが複数個設定されるように、複数個のボンディングポイントのインスタンス名、座標、接続情報および半導体チップのパッド座標をワイヤボンディング装置に入力する第1の工程S1と、半導体チップのパッケージ基板に対する位置ずれ量を検出する第2の工程S2と、検出した位置ずれ量に基づいて、複数のボンディングポイントの中から最適ボンディングポイントを検出する第3の工程S3と、最適ボンディングポイントのインスタンス情報をワイヤボンディング装置に伝達する第4の工程S4とを有する。

(もっと読む)

配線基板、それを用いた半導体装置、およびその製造方法

【課題】半導体チップをワイヤボンドする配線基板の接続箇所でのショートを防止する。

【解決手段】複数の配線パターン8が表面に形成されたFPC5などの配線基板において、配線パターン8のランド9の部分を覆う絶縁性のカバーレイ12が設けられたことを特徴とする。ランド9どうしのショートが起こらない構造である。半導体チップ3をワイヤボンドする際には、ワイヤ13の接続部にてカバーレイを貫通して接続を行なえばよいので、接続対象でないランド9やそれに続く配線部11とショートすることがない。

(もっと読む)

回路基板及び半導体装置

【課題】回路基板に形成されたボンディングパッドにボンディングワイヤーを容易かつ確実に接合できるようにする。

【解決手段】半導体チップ12と、半導体チップ12が搭載される回路基板11とを含み、回路基板11は、回路基板11の端面に開口し、当該回路基板11を貫通して形成される貫通孔113を有し、回路基板11は、各貫通孔13を塞ぐようにボンディングパッド111が形成されてなる半導体装置1において、ボンディングパッド111の表面の貫通孔113が形成されている部分に第1のソルダーレジスト1171を施すようにする。また回路基板11に、半導体チップ12が搭載される領域を囲んで第1のソルダーレジスト1171に連続する環状の第2のソルダーレジスト1172を施すようにする。

(もっと読む)

半導体装置及びその製造方法

【課題】解読、偽造、捏造等が困難な安全性の高い識別情報を付与した半導体装置及びその製造方法を提供すること。

【解決手段】半導体素子5と配線基板のリード2とを電気的に接続する複数のボンディングワイヤ3を用いて、半導体装置1に識別情報を付与する。各ボンディングワイヤ3は、所定の複数の形態のうちのいずれかの形態を有すると共に識別情報を構成する識別要素の1つである。識別情報は、ボンディングワイヤ3の複数の形態の所定の配列ないし組み合わせにより形成される。

(もっと読む)

半導体装置

【課題】1つのチップで複数種類のパッケージに容易に組み立て可能にする。また、ボンディングの際、配線の修正を必要とせず、拡散工程の工数を増やすことなく対応する。

【解決手段】2つのパッドで1つのI/Oバッファを共有し、パッケージによりボンディングするパッドを使い分ける。すなわち、本発明の半導体装置は、第1の辺と第2の辺とが角部(コーナー)を形成する矩形のチップ(10)上において、前記第1の辺に沿って設けられた複数のパッド(1)のうち前記角部の近傍に設けられた第1のパッド(1−1)と、前記第2の辺に沿って設けられた複数のパッド(2)のうち前記角部の近傍に設けられた第2のパッド(2−1)と、前記第1のパッド(1−1)及び前記第2のパッド(2−1)の両方に接続された1つのバッファ(3−1)とを具備する。

(もっと読む)

半導体チップ搭載基板

【課題】半導体チップ搭載基板で、ワイヤーボンディング接続するときの金属ワイヤーの長さに制限をなくし、基板製造コストの上昇を防止する手段を提供する。

【解決手段】ボンディングワイヤー15により基板11上電極13とチップ12上電極14とを接続する過程で、基板上電極とチップ上電極の中間位置にて金属ワイヤーの一部がワイヤー固定手段16を介して基板に接する構造を形成する。これにより金属ワイヤーの形状が安定し長い金属ワイヤーが使えるため、離れた位置にある細密ではない形状の基板電極と接続が可能になり、基板製造コストが削減される。

(もっと読む)

半導体装置、インタポーザチップ、および半導体装置の製造方法

【課題】ボンディングワイヤ同士が接触し難い半導体装置を提供する。

【解決手段】この半導体装置では、配線基板1の表面にメモリチップ2〜5を積層し、メモリチップ5の表面にマイコンチップ6とインタポーザチップ7を配置し、マイコンチップ6のパッド16,17とインタポーザチップ7の略円弧状に配置されたパッド18,19とをボンディングワイヤW2,W3によって接続する。したがって、封止用液体樹脂の注入圧力をワイヤW2によって弱めることができるので、ワイヤW3の変形によるワイヤW3同士の接触を防止できる。

(もっと読む)

半導体装置の製造方法

【課題】狭ピッチの半導体チップを多層配線基板に搭載し、封止した半導体装置について、ワイヤボンディング工程時のワイヤボンダ装置を容易に特定する。

【解決手段】まず、多層配線基板を用意した後、半導体チップを多層配線基板上にダイボンディングする(工程S1)。次いで、ワイヤボンダ装置によって、半導体チップ上の電極パッド(第1電極)と多層配線基板上の金属配線(第2電極)とをワイヤボンディングする(工程S4)。このワイヤボンディング工程において、ワイヤボンダ装置に備え付けられたレーザマーカ機構によって、ワイヤボンディングされた多層配線基板にワイヤボンディング情報をレーザ刻印する。次いで、半導体チップを覆うように多層配線基板上にレジンからなる封止体を形成する(工程S5)。

(もっと読む)

電子装置

【課題】2つの部材を複数本のボンディングワイヤにより接続するとともに、これら複数本のボンディングワイヤをゲル部材により封止してなる電子装置において、ダミーのボンディングワイヤを用いることなく、ゲル部材によるボンディングワイヤのダメージを抑制する。

【解決手段】パワーICチップ70と回路基板20とを接続する第1のワイヤ51と第2のワイヤ52とにおいて、第1のワイヤ51におけるゲート用のパッド70aとの接続部および第1の回路基板20のパッド21との接続部を結ぶ線L1と、第2のワイヤ52におけるソース用のパッド70bとの接続部および第1の回路基板20のパッド21との接続部を結ぶ線L2とが交差した位置関係にある。

(もっと読む)

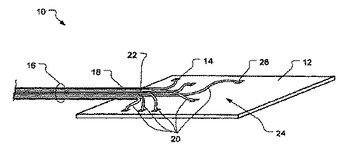

回路インターフェースのための電気的マイクロフィラメント

超小型電子回路のための電気的相互接続のためのデバイス及び方法が開示される。電気的相互接続の1つの方法(90)は、少なくとも2つのマイクロフィラメントがそれらの長さに沿って延びる導電性部分を含む、マイクロフィラメントの束を形成するステップ(92)を含む。方法はまた、マイクロフィラメントを超小型電子回路の基板の対応するボンドパッドに接合して、導電性部分とそれに対応するボンドパッドとの間に電気的接続を形成するステップ(94)を含むことができる。1つの超小型電子回路(10)は、対応するボンドパッド(14)に接合されて、対応するボンドパッドとマイクロフィラメントの導電性部分との間に電気的接続を形成するマイクロフィラメント(18)の束(16)を含むことができる。  (もっと読む)

(もっと読む)

ワイヤボンディング装置用キャピラリ

【課題】複数のパッド層及びLow−Kパッケージ,即ち金属酸化物のレイヤー層の厚さが非常に薄く,低い抵抗値を示すパッケージなどのワイヤボンディング工程に効果的に適用できる,ワイヤボンディング装置用キャピラリを提供する。

【解決手段】ストレート部100と,キャピラリの先端から第1段差103まで延接された8〜12゜の第1テーパーを有し,キャピラリの先端から第1段差103までの第1高さが0.1〜0.5mmであるテーパー状の第1ボトルネック部101と,第1ボトルネック部101の第1段差103からストレート部100に接する第2段差103’まで延接された10〜15゜の第2テーパーを有し,キャピラリの先端から第2段差103’までの第2高さが1.5〜5.0mmであるテーパー状の第2ボトルネック部102とを含んでいる。

(もっと読む)

半導体装置

【課題】パッケージ外形サイズの大型化を招くことなく、従来に比べて製造コストの低減を図ることのできる半導体装置を提供する。

【解決手段】基板1には、半導体チップ3の電極パッド4と同一ピッチで基板インナーリード2が配置されている。電極パッド4と基板インナーリード2とは、ワイヤ5で接続されている。基板インナーリード2と、電極パッド4には、夫々ボンディングボール7bが形成され、基板インナーリード2上のボンディングボール7bは、その径が基板インナーリード2の線幅より広い。

(もっと読む)

半導体装置設計支援装置、半導体装置設計支援方法、その方法をコンピュータにより実行可能なプログラム、及び、そのプログラムを記録した記録媒体

【課題】 基板の端子と基板上に配置されるチップの端子とが電気的配線により接続される半導体装置の設計の支援に適合する半導体装置設計支援装置等を提案する。

【解決手段】 SiP設計支援装置1は、基板及びチップの少なくとも一方の接続されるべき端子に対して処理を行う端子処理部5と端子処理部5による処理後の端子位置に基づいて再配線を行う自動再配線処理部7を備え、端子処理部5は選択された交換対象の端子に対して所定の条件を満たす交換先の端子を決定する端子交換先決定処理部9と交換対象の端子の位置と交換先の端子の位置を交換する端子位置変更手段11とを有する。

(もっと読む)

半導体装置の製造方法

【課題】 可撓性フィルムからなるベース基板1上の全域に絶縁膜を配置した場合、ベース基板1に反り、歪み等の変形が生じる。

【解決手段】 可撓性フィルムからなるベース基板1の一表面に配線導体(バンプ接続用電極パッド2、配線3、ワイヤ接続用電極パッド4、メッキ用配線5)が配置され、前記可撓性フィルムの表面上に接着材12を介在して半導体チップ10が搭載される半導体装置であって、前記配線導体上に絶縁膜9を複数個に分割して配置する。

(もっと読む)

ディスプレイ装置

【課題】製造における工数と原価の上昇を抑え、接続工程の簡素化が可能な実装構造を備えるディスプレイ装置を提供する。

【解決手段】表示パネル11および駆動回路基板10と、表示パネル11と駆動回路基板10との間を電気的に接続するテープキャリアパッケージ(TCP)17とを備え、TCP17が半導体素子1の主面にある出力電極6とワイヤボンディングにより接続された出力端子15と、半導体素子1の入力電極7とインナーリードボンディングにより接続された入力端子16とを備る構成とする。

(もっと読む)

161 - 180 / 217

[ Back to top ]