Fターム[5F044AA18]の内容

ボンディング (23,044) | ワイヤによるペレット電極との接続構造 (951) | 同一のパッド電極に複数本のワイヤ接続 (51)

Fターム[5F044AA18]に分類される特許

1 - 20 / 51

パワー半導体モジュール

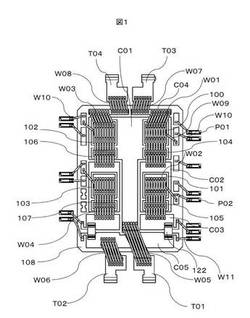

【課題】単一のパワー半導体モジュールに例えば12アームを搭載可能にコンパクトに実装するとともに、直流端子と交流端子のそれぞれの端子をモジュール端面にそれぞれ配置し、また、電力回路のインダクタンスを低く保つこと。

【解決手段】1枚の絶縁基板108上に2組の上アーム(100,104と102,106)を絶縁基板上の上寄り左右に配置し、2組の下アーム(101,105と103,107)を絶縁基板上の下寄り左右に配置して、絶縁基板上の配線パターンとして、2組の上アームを第1の配線パターンC01上に実装し、2組の下アームは第1の配線パターンの下に配置した第2、第3の配線パターンC02,C02上にそれぞれ実装して、第2、第3の配線パターンの間に第1の配線パターンC01を延長し、その延長した端部に正極端子T01からの配線を接続し、さらに、絶縁基板108を1モジュール中に3枚並置して実装して12in1モジュールの構成とすること。

(もっと読む)

半導体装置

【課題】信頼性の低下を抑制し得る半導体装置を提供する。

【解決手段】半導体装置2は、表面に表面電極44が形成されている半導体素子40と、表面電極44上に接合される導電板材50と、を有している。導電板材50は、表面電極44と対向する底面102と、底面102と反対側であって、大電流用ワイヤ60がボンディングされる領域を有する上面104とを備える。上面104の面積は底面102の面積より大きい。

(もっと読む)

半導体装置

【課題】隣接する2つのトランジスタ同士が接続された構成を有し、省スペースと電流集中による信頼性の低下の抑制とを両立させた半導体装置を実現できるようにする。

【解決手段】半導体装置は、第1のトランジスタ101と接続された第1のバス111、第2のトランジスタ102と接続された第2のバス112と、第1のバス111と第2のバス112との間に形成され、第1のバス111と第2のバス112とを接続するバス間配線121とを備えている。バス間配線121は、第1のバス111における第2のバス112と対向する辺の一部及び第2のバス112における第1のバス111と対向する辺の一部と接続されている。第1のコンタクトパッド131は、第1のバス111の一部と接続され、第2のコンタクトパッド132は、第2のバス112の一部と接続されている。

(もっと読む)

半導体装置及びその製造方法

【課題】 半導体チップの電極パッドを厚膜化あるいは大面積化することなく、電極パッドの溶断を防止し、電流パッドの許容電流値を高める。

【解決手段】 半導体チップ20の少なくとも1つの電極パッド21s、21dにおいて、単一の電極パッド21上に、第1ワイヤ41が複数箇所45でボンディングされる。さらに、第1ワイヤ41に沿って、第1ワイヤ上41に、第2ワイヤ42が複数箇所46でボンディングされる。一部の実施形態において、第2ワイヤ42のボンディングに先立って、電極パッド21上の第1ワイヤ41の頂部形状を加工してもよい。

(もっと読む)

半導体パッケージ

【課題】ボンディングワイヤのループインダクタンスを低減した半導体パッケージを提供する。

【解決手段】所定の方向に交互に配置された信号用パッドおよび補助パッドのそれぞれが複数設けられた半導体装置と、信号用ボンドフィンガー、電源電圧用ボンドフィンガーおよび接地電位用ボンドフィンガーのそれぞれが複数設けられたパッケージ基板と、を有する。複数の信号用パッドのそれぞれが複数の信号用ボンドフィンガーのそれぞれと第1のワイヤを介して接続され、複数の電源電圧用ボンドフィンガーおよび複数の接地電位用ボンドフィンガーのそれぞれが複数の補助パッドのそれぞれと第2のワイヤを介して接続されている。第1のワイヤが、電源電圧用ボンドフィンガーに接続された第2のワイヤと接地電位用ボンドフィンガーに接続された第2のワイヤとの間に配置されている。

(もっと読む)

ワイヤボンドの接合構造及び接合方法

【課題】接合機との干渉を防止し、半導体モジュールの小型化を図ること。

【解決手段】ワイヤボンドの接合構造は、バスバ11,13を多段構造に構成し、バスバ11,13にワイヤ15,16を接合する。詳しくは、上段バスバ13及びそれを支持する上段支持部14を含む上段バスバ部材6が、下段バスバ11及びそれを支持する下段支持部12を含む下段バスバ部材5と別体に構成される。下段バスバ11と下段ワイヤ15とが接合され、上段バスバ部材6が下段バスバ部材5に固定され、その後に、上段バスバ13と上段ワイヤ16とが接合される。下段バスバ部材5の上面であって、下段バスバ11と下段ワイヤ15との接合部15aの近傍を除く領域に、上段バスバ部材6が固定される。

(もっと読む)

半導体集積回路装置

【課題】クロストークノイズの抑制及びEMCを強化し、且つ、クロストークノイズの抑制等に用いるスペースを縮小して小型化を可能とする半導体集積回路装置を得られるようにする。

【解決手段】半導体集積回路装置は、実装基板10の上に保持され、半導体集積回路を含む半導体チップ11と、実装基板10の上に形成され、半導体集積回路が処理する信号を伝送する第1の配線1と、半導体集積回路と第1の配線6とを接続する第1のボンディングワイヤ6と、実装基板10の上に形成された複数の第2の配線2と、半導体集積回路と複数の第2の配線2のうちのいずれかとをそれぞれ接続する複数の第2のボンディングワイヤ8とを備えている。第2のボンディングワイヤ8は、第1のボンディングワイヤ6の上方で且つ該第1のボンディングワイヤ6と間隔をおくように互いに交差して形成されている。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】半導体装置の小型化に対応できる半導体装置を提供する。

【解決手段】一面から他面に貫通して設けられた開口部12と、一端が露出された配線19とを有する基板17と、基板17の一面に搭載され、開口部12から露出するように配置された同電位の2以上の電極パッド5を含む電極パッド群15を有する半導体チップ16と、同電位の2以上の電極パッド5を接続するとともに、基板17に配置された1つの配線19の一端と接続する接続部材7とを備える半導体装置10とする。

(もっと読む)

半導体パッケージ

【課題】現実的な実装方法で寄生インダクタンスを低減する手段を提供する。

【解決手段】半導体パッケージ1表層には、ワイヤボンディングの接続点である該半導体パッケージ表層上で突出する複数の櫛歯状グラウンドパッド31を有するグラウンドパッドを設ける。櫛歯状グラウンドパッドの間には、電源パッド25を配置する。

1つの櫛歯状グラウンドパッド31には長短二本のグラウンドワイヤが配される。また、1つの電源パッド25には長短二本の電源ワイヤが配される。

長いグラウンドワイヤ12−2と長い電源ワイヤ11−2、短い電源ワイヤ11−1と短いグラウンドワイヤ12−1を平行かつ近接するように配置することで寄生インダクタンスを低減する。

(もっと読む)

低インダクタンス化された結合素子が接合されたマイクロ電子アセンブリ

マイクロ電子アセンブリ100は、第1の面において露出するチップコンタクト112を有する半導体チップ110、1110と、チップ110、1110の面128、129と並置される基板130、1130とを含む。導電性結合素子144が第1のチップコンタクト112を基板の第1の基板コンタクト132、1132と電気的に接続することができ、第2の導電性結合素子146が第1のチップコンタクト112、132を第2の基板コンタクトと電気的に接続することができる。第1の結合素子144は第1のチップコンタクト112、212Aに冶金学的に接合される第1の端部244A、344Aと、第1の基板コンタクトに冶金学的に接合される第2の端部244B、344Bとを有することができる。第2の結合素子の第1の端部246A、346Aは第1の結合素子212Aに冶金学的に接合することができる。第2の結合素子は、第1のチップコンタクト112、212A、1212又は基板コンタクト132、1132と接触する場合も、接触しない場合もある。第3の結合素子948を、基板コンタクト又はチップコンタクトに接合される第1の結合素子及び第2の結合素子の端部に接合することができる。一実施形態では、結合素子740は、第1のコンタクト732Aにおいて接合される第1の端部742及び第2の端部746と、第2のコンタクト712Aに接合される中央部744とを有する、ループ状接続を有することができる。 (もっと読む)

半導体装置およびそれを備えた電子回路

【課題】同一のボンディングパッドに対して異なる金属のボンディングワイヤーを用いて信頼性の高い配線を行う。

【解決手段】窒化物半導体ヘテロ接合型電界効果トランジスタにおけるソース電極8,ドレイン電極9,ソースパッド8'およびドレインパッド9'をTi,Al,MoおよびAuを順次積層して形成し、ソースパッド8'およびドレインパッド9'の一部をエッチングによって開口して、Al露出部を形成している。したがって、ソースパッド8'またはドレインパッド9'におけるAu露出部に対しては、Auボンディングワイヤーを用いたワイヤーボンディングを行う一方、上記Al露出部に対しては、Alボンディングワイヤーを用いたワイヤーボンディングを行うことによって、優れた密着性とエレクトロマイグレーション耐性を得ることができる。

(もっと読む)

電力変換装置

【課題】電力変換装置においてスイッチング素子のオンオフ動作によって発生するコモンモードノイズを低減できるようにする。

【解決手段】上アーム側スイッチング素子(130)が搭載され、搭載された上アーム側スイッチング素子(130)の一方のドレイン(131)が接する上アーム側パターン配線(40)と、下アーム側スイッチング素子(140)のみが1つ搭載され、搭載された下アーム側スイッチング素子(140)の一方のソース(142)が接する複数の下アーム側パターン配線(50)とを設ける。また、各上アーム側スイッチング素子(130)のもう一方のソース(132)と複数の下アーム側パターン配線(50)とを上アーム側ワイヤ配線(70)で1対1に接続する。そして、下アーム側パターン配線(50)と電力出力端子(20)とを出力端子側ワイヤ配線(80)で1対1に接続する。

(もっと読む)

電力用半導体装置および電力用半導体装置の製造方法

【課題】 信頼性が高く、損失低減と短絡時の耐量向上を両立させた電力用半導体装置を得ることを目的とする。

【解決手段】 絶縁性の基板1と、絶縁性の基板1の主面1fに形成された複数の配線2と、複数の配線2のうちの第1の配線2aに接合された半導体素子3と、半導体素子3の第1の配線2aとの接合面と反対側になるソース電極3fの一部と、複数の配線2のうちの第2の配線2bとを電気的に接続するワイヤ4と、を備え、ソース電極3fには、複数の金属塊5が分散して接合され、複数の金属塊5のそれぞれは、ソース電極3fとの接合面以外が絶縁物7で覆われている。

(もっと読む)

半導体装置及びその製造方法並びにワイヤボンディング装置及びその動作方法

【課題】ワイヤの低インダクタンス化、半導体チップへのダメージ軽減、接合部の強固な接合、及び半導体パッケージの小型化を同時に実現することで、高信頼性及び小型化を両立した半導体装置及びその製造方法を提供する。

【解決手段】ボールを介して半導体チップ5のチップ電極にワイヤを接合する1回目のボンディングステップと、ボールを介してリード端子にワイヤを接合する2回目のボンディングステップと、ボールを介して半導体チップ5のチップ電極にワイヤを接合する3回目のボンディングステップと、リード端子にワイヤを接合する4回目のボンディングステップと、ワイヤを切断するステップとを備える。

(もっと読む)

半導体装置及びその製造方法

【課題】第1の電極端子と第2の電極端子間の配線におけるオン抵抗を低減する、半導体装置及び半導体装置の製造方法を提供する。

【解決手段】半導体装置100は、第1の電極端子と、第2の電極端子と、前記第1及び第2の電極端子を接続する少なくとも2本のワイヤー14とを有する。少なくとも2本のワイヤー14は、ワイヤー14が延びる方向に沿って導電性接着剤15を用いて互いに電気的に接続されている。第1の電極端子は、例えば外部引き出し電極20の端子である。また、第2の電極端子は、例えばMOSFETのソース電極22の端子である。

(もっと読む)

半導体装置及びその製造方法

【課題】複数のワイヤがボンディングされた半導体素子を備える半導体装置であって、十分な接合信頼性を実現することができるとともに、放熱性が良好な半導体装置及びその製造方法を提供することを目的とする。

【解決手段】

半導体層上に設けられた電極上に、ボールボンディングされた第1のワイヤを有し、該第1のワイヤは、前記電極上に接合されたボール部と、該ボール部から延伸して折り返された折り返し部とを有し、該折り返し部に延伸する部分と該折り返し部から延伸する部分とが前記ボール部上で接触し、前記ボール部の上で前記第1のワイヤにボンディングされた第2のワイヤを有し、前記ボール部の周縁部上において、前記第1のワイヤの折り返し部または前記第2のワイヤと前記ボール部との間に空隙を有することを特徴とする半導体装置に関する。

(もっと読む)

パッケージされた集積回路装置及びその動作方法とこれを有するメモリ保存装置及び電子システム

【課題】減少した信号スキューを提供するマルチチップ・パッケージされた集積回路装置及びその動作方法を提供する。

【解決手段】本発明のパッケージされた集積回路装置は、導電性パッドを上に含む基板と、基板上に複数のチップを含むチップスタックと、1次導電性ラインと、2次導電性ラインと、を備える。1次導電性ラインは、基板上の導電性パッドと、チップスタックの複数のチップのうちの一つの上に設けられた導電性パッドとを電気的に連結する。2次導電性ラインは、チップスタック内の複数のチップのうちの一つの上に設けられた導電性パッドを、その上側にある複数のチップのうちの一つ、及び下側にある複数のチップのうちの一つの上に設けられた対応する導電性パッドに電気的に連結する。

(もっと読む)

ボンディングパッドを有する半導体装置及びその形成方法

【課題】信頼性の高い集積回路を提供する。

【解決手段】集積回路20は、基板26を覆うパッシベーション層18及び前記基板26を覆うボンディングパッド200を備え、該ボンディングパッド200は、第1ボンディングワイヤを当該集積回路20に接続するための第1ワイヤボンディング領域202と第2ボンディングワイヤを当該集積回路に接続するための第2ワイヤボンディング領域204とを含み、前記第1ワイヤボンディング領域202の少なくとも非周辺部分が前記パッシベーションの上に位置し、前記ボンディングパッド200の下方にあるパッシベーション層が複数の開口を有し、前記基板26は配線領域を有し、該配線領域の少なくとも一部は前記パッシベーションの上に位置する前記ボンディングパッド200の一部の下に存在し、かつ前記配線領域の部分が前記複数の開口を介して前記ボンディングパッド200に結合する。

(もっと読む)

半導体装置

【課題】配線基板上に実装された半導体チップと配線基板上のワイヤボンドパッドとを接続するボンディングワイヤが半導体チップに干渉することを回避しつつ、半導体チップとワイヤボンドパッドまでの距離が小さい半導体装置を提供する。

【解決手段】配線基板2上に半導体チップ1が実装され、配線基板2上のワイヤボンドパッド5と半導体チップ1上の電極パッド4とがボンディングワイヤを介して接続された半導体装置8であって、電極パッド4よりも半導体チップ1の端部に近接した位置にワイヤボンドパッドを有する中継基板10が設けられ、半導体チップ1上の電極パッド4と中継基板10上のワイヤボンドパッドとが第1のボンディングワイヤ3Aを介して接続され、中継基板10上のワイヤボンドパッドと配線基板2上のワイヤボンドパッド5とが第2のボンディングワイヤ3Bを介して接続されている。

(もっと読む)

半導体装置

【課題】高周波特性の劣化を抑え、小型化を図った半導体装置を提供する。

【解決手段】配線基板1の主面上に搭載された半導体チップ5は、第1の増幅手段PW1の入力部と電気的に接続するチップ側入力用電極6Aと、第2の増幅手段PW2の出力部と電気的に接続するチップ側出力用電極6Bを含み、配線基板1は、主面上に、基板側入力用電極2Aと基板側出力用電極2Bとを有し、第1の増幅手段PW1の出力部は第2の増幅手段PW2の入力部と電気的に接続され、チップ側入力用電極6Aと基板側入力用電極2Aは入力用ワイヤ7Aによって電気的に接続され、チップ側出力用電極6Bと基板側出力用電極2Bは、出力用ワイヤ7Bによって電気的に接続され、入力用ワイヤ7Aは半導体チップ5の平面形状を成す一対の第1の辺のうちの一つの辺を跨ぐように形成され、出力用ワイヤ7Bは一対の第2の辺のうちの一つの辺を跨ぐように形成されている。

(もっと読む)

1 - 20 / 51

[ Back to top ]