Fターム[5F044EE00]の内容

ボンディング (23,044) | ボンディングパッド電極 (1,310)

Fターム[5F044EE00]の下位に属するFターム

パッドの形状 (114)

パッドの配置 (187)

パッドの材料 (132)

パッドが多層構造になっているもの (180)

検査用パッド (75)

パッドの腐食防止、耐湿改善したもの (41)

機械的破損防止したもの (132)

パッドの剥れを防止したもの (53)

ワイヤとパッドの密着力を増強したパッド (64)

電極配線の切断防止したもの (13)

パープルプレーグを防止したもの (9)

静電破壊防止したもの (8)

浮遊容量の小さいパッド (9)

パッドによるキャパシタの形成 (3)

高集積度化したもの (45)

パッド電極の形成方法 (228)

Fターム[5F044EE00]に分類される特許

1 - 17 / 17

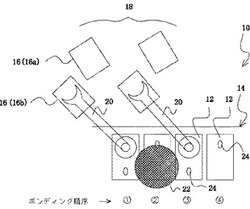

半導体装置及びそのワイヤーボンディング方法

【課題】キャピラリーとワイヤーとの干渉・接触を避けながらボンディングパッドとフィンガーが接合される半導体素子及びそのワイヤーボンディング方法を提供すること。

【解決手段】半導体素子10は、ボンディングパッド12を備えた矩形の半導体チップ14とフィンガー16を備えた矩形のリードフレームよりなる。ワイヤー20により、それぞれのボンディングパッド12とそれぞれのフィンガー16は接合される。ワイヤーは、比較的短い第1のワイヤー群20と、比較的長い第2のワイヤー群(図示せず)に振り分けられる。第1のワイヤー群20のボンディングパッド側接合点は、半導体チップ14の外縁に近い位置に、第2のワイヤー群のボンディングパッド側接合点は、半導体チップ14の外縁から離れた位置にずれている。これにより、先行形成されたワイヤーとキャピラリーの干渉を避けることができる。

(もっと読む)

導電性バンプ、ワイヤループ、およびそれらを形成する方法

【解決手段】 導電性バンプを形成する方法が提供される。この方法は、(1)ボンディングボールを形成するボンディングツールを使用して、ボンディング位置にフリーエアボールをボンディングする工程と、(2)ワイヤクランプが開いた状態で、前記ボンディングボールに接続するワイヤを繰り出しながら、前記ボンディングツールを望ましい高さまで上昇させる工程と、(3)前記ワイヤクランプを閉じる工程と、(4)前記ワイヤクランプが閉じた状態で、前記ボンディングツールを平滑化に適した高さまで下降させる工程と、(5)前記ワイヤクランプが閉じた状態で、前記ボンディングツールを使用して前記ボンディングボールの上面を平滑化させる工程と、(6)前記ワイヤクランプが閉じた状態で、前記ボンディングツールを上昇させ、前記ボンディングツールと係合するワイヤから前記ボンディングボールを分離させる工程とを含む。

(もっと読む)

半導体装置

【課題】抵抗値を調整可能な半導体装置をコンパクト化する。

【解決手段】基板接続領域と、外部配線接続領域と、基板接続領域と外部配線接続領域との間に設置される抵抗調整領域とを、1つの電極パッドに形成し、コンパクト化する。電極パッドの抵抗調整領域に対してトリミングを行うことによって、電極パッドの基板接続領域と外部配線接続領域との間の抵抗値を調整することができる。これによって、抵抗値を調整可能な半導体装置をコンパクト化することができる。

(もっと読む)

半導体装置及びその製造方法

【課題】ボンディングパッドの剥がれを防止し、かつボンディングパッド間におけるリーク電流の発生を防止することができる半導体装置及びその製造方法を提供すること。

【解決手段】HBT(ヘテロ構造バイポーラトランジスタ)が構成要素の1つとして集積された半導体装置110は、半絶縁性InP基板11上に、順次、エッチングストップ層12、コレクタコンタクト層13、コレクタ層14、傾斜コレクタ層15、セットバック層16、ベース層17が形成された構成を有し、ベース層17はInGaAsで構成された薄膜であってPを含まず、このベース層17上にSiN23が形成され、SiN23上にボンディングパッド25が形成された構成を有する。

(もっと読む)

ワイヤーボンド方法

【課題】 アイランド現象を発生させないでアルミ薄膜にアルミ線でワイヤーボンドする方法の提供。

【解決手段】 水晶基板11にアルミで成膜した薄膜にアルミ線13を超音波で接合し配線を作るワイヤーボンド方法であって、ウエッジヘッドでアルミ線13をアルミ薄膜12の上に押しつける工程と、アルミ線13とアルミ薄膜12に超音波振動を印加する工程とを含み、前記超音波振動の強度を所定値より低く、前記超音波振動の印加時間を所定値より長くする。

(もっと読む)

半導体装置とその検査方法と検査済半導体装置の製造方法

【課題】半導体基板の表面電極へのワイヤのボンディング予定領域に検査用プローブを押圧することのできる技術を提供する。

【解決手段】半導体基板10の表面にエミッタ電極20が形成されている。エミッタ電極20の上に、厚み方向に貫通しているスリット22aが設けられている保護層22が形成されている。スリット22aの間と保護層22の上に、エッチングレートが保護層22よりも高い検査用電極24が形成されている。プローブを検査用電極24の表面に押圧して検査すると、プローブの荷重によって検査用電極24の表面に起伏が形成される。保護層22のエッチングレートは検査用電極のエッチングレートよりも低いので、検査後に電極24と保護層22を除去すれば起伏跡のない平坦な表面を有するエミッタ電極20を暴露できる。エミッタ電極の平坦な表面にワイヤをボンディングできるので、ボンディングの際に素子に局所的なストレスが加わることがない。

(もっと読む)

半導体装置

【課題】 半導体装置が機能するのに必要な半導体構造を製造できる有効領域を拡大する技術を提供する。

【解決方法】 本発明の半導体装置2では、その表面に形成されるパッド12の少なくとも一部が、半導体基板4の表面の外周の内側を一巡する耐圧保持部65上に形成されている。従来技術では耐圧保持部65の内側に形成されていたパッド12の少なくとも一部を耐圧保持部65上に形成することで、耐圧保持部65の内側のパッド領域10の面積を縮小することができる。これにより、耐圧保持部65の内側で半導体装置2が機能するのに必要な半導体構造を製造できる有効領域8を拡大することができる。また、パッド12と耐圧保持部65の間に導電膜を含む積層構造20を形成することで、耐圧保持部65に局所的な電界が印加されることがない。半導体装置2の耐圧特性が悪化することを防ぐことができる。

(もっと読む)

半導体装置

【課題】電源配線を介して伝播する電源ノイズを有効に抑制することができる半導体装置を提供すること。

【解決手段】異なる複数の回路に共通のパッド電極を介して給電するように構成された半導体装置において、前記パッド電極は、デジタル回路に給電するための電源配線の一部をなす導電膜(201A)と、前記導電膜から離間して形成され、アナログ回路に給電するための電源配線の一部をなす導電膜(201B)と、前記導電膜(201A,201B)の上層に絶縁膜を介して形成され、前記導電膜(201A,201B)の夫々と層間配線手段を介して電気的に接続された導電膜(204)とから構成される。

(もっと読む)

半導体装置

【課題】ボンディング用パッドに対するプローブ針の接触時に層間絶縁膜にクラックが入った場合に、そのクラックの有無を検出できるようにし、後の組み立て時の歩留りの向上を図り、もってコストの低減化を図ること。

【解決手段】この発明は、層間絶縁膜27上に形成されたボンディング用パッド3を有する半導体装置である。ボンディング用パッド3の下の位置の層間絶縁膜25上に、層間絶縁膜27を介在してクラック検出用電極を含むクラック検出用パターン5が形成されている。クラック検出用パターン5は、層間絶縁膜27上に形成されるクラック検出用パッド6と電気的に接続されている。

(もっと読む)

半導体装置の製造方法

【課題】ボンディング等、パッドへの圧力によるクラック発生を回避する半導体集積回路装置を提供する。

【解決手段】内部回路側では半導体素子回路を構成する金属配線パターンWPが層間絶縁膜IL及びビアVIAを介して多層配線構造を実現している。このような多層配線の延長上の金属パッドPAD形成領域直下にはダミーパターン禁止領域PROHが設けられている。すなわち、ダミーパターン禁止領域PROH上に層間絶縁膜ILを介して半導体素子回路に繋がり外部との電気的接続領域を有する金属パッドPADが設けられている。PAD下周辺の所定距離d1の範囲内はすべて層間絶縁膜ILで埋められた構成となっている。金属パッドPADへのボンディング時の衝撃はダミーパターン禁止領域PROH上を埋める層間絶縁膜ILにかかる。

(もっと読む)

半導体集積回路

【課題】ボンディングオプションパッドに対する入力部の消費電流を低減しかつこのボンディングオプションパッドに接続される回路の誤動作を防止する。

【解決手段】パッド(11)に対して電源投入時にこのパッドを所定電圧に駆動する第1トランジスタを(20g)を設けるとともに、パッド電位をインバータ(20b)およびトランジスタ(20e)のハーフラッチでラッチする。

(もっと読む)

ドライエッチング用パターンマスクの方法と構造

【課題】エッチング反応向け構造を提供する。

【解決手段】該構造にはウェハー区域のエッチングからの防護用マスクおよびマスク下面の下に貼り付けられるシールリングがある。該マスクにはエッチング区域を暴露させる少なくともひとつの空気開口部がある。さらに、マスクはシールリングによりウェハーに貼り付けられる。さらに、本発明によりドライエッチング反応用マスクを形成する方法も提供される。まず、本発明にはベース材料の準備および該ベース材料両面のマスキング材料の塗布の段階が含まれる。次の段階は開口部を形成するマスキング材料のパターン付けである。引き続き、ベース材料は少なくとも1つのマスク開口部を生成する開口部とマスク孔を通じてエッチングされる。最後に、マスク材料の除去が行われる。

(もっと読む)

半導体装置およびその製造方法

【課題】検査時のプロービング又はワイヤボンディングの際に、パッドの下層の絶縁膜にクラックが発生するのを防止し、ワイヤボンディングでのパッド剥がれを防止する半導体装置およびその製造方法を提供する。

【解決手段】半導体基板101上に形成された一の絶縁膜112と、一の絶縁膜112の上に形成された一の金属パターン116と、一の絶縁膜112および一の金属パターン116の上に形成された他の絶縁膜117と、他の絶縁膜117の上に一の金属パターン116と対向して形成された他の金属パターン119と、他の金属パターン119の周囲に配置して、他の絶縁膜117中に形成された接続孔120bとを備え、接続孔120bを通じて一の金属パターン116と他の金属パターン119を直接接触させて電気的に接続する。

(もっと読む)

マイクロ電子デバイスおよびマイクロ電子支持デバイスならびに関連するアセンブリおよび方法

マイクロ電子デバイス、関連するアセンブリ、および関連する方法を提供する。例えば、本発明のある態様は、面および面内の開口を有するマイクロフィーチャワークピースを含むマイクロ電子デバイスを対象とする。デバイスは、表面を有するワークピースコンタクトをさらに含むことができる。ワークピースコンタクトの表面の少なくとも一部が、開口と、開口と表面の間に延びる通路とを通じてアクセス可能にすることができる。本発明の他の態様は、マイクロフィーチャワークピースのワークピースコンタクトに接続可能にすることができる支持コンタクトを保持する面を有する支持部材を含むマイクロ電子支持デバイスを対象とする。デバイスは、支持部材によって保持された埋込支持コンタクト手段をさらに含むことができる。埋込支持コンタクト手段は、マイクロフィーチャワークピースの第2のワークピースコンタクトに接続可能にすることができる。 (もっと読む)

半導体製造装置の装置プログラムの管理システム

【課題】 装置プログラムのファイル数が極端に多い場合でもその管理が簡単で、装置プログラムの選択にそれほど手間がかからない半導体製造装置の装置プログラムの管理システムを提供する。

【解決手段】 複数種類の製品に対してボンディング処理を実行可能なボンディング装置の装置プログラムを管理する管理システム100であって、製品の種類毎及び、ボンディング装置の号機毎にそれぞれ設定された複数種類の装置プログラムを格納するファイルサーバと、行又は列の一方に製品の種類を示し且つその他方にボンディング装置の号機を示すマトリクスの当該行と該列とが交差する各セルに、各セル毎の行要素及び列要素の組み合わせに対応する装置プログラムがファイルサーバに格納されているか否かを認識可能に表示することにより、当該装置プログラムの一覧を画面表示するモニタと、複数のセルの中から任意のセルをポインタ90で選択可能なマウスと、を有する。

(もっと読む)

半導体装置

【課題】 ゲート電極下の絶縁膜の実装時のストレスによるクラックの発生を防止できるようにした半導体装置及びその製造方法、半導体装置の設計方法を提供する。

【解決手段】 シリコン基板1に設けられたトランジスタと、このトランジスタを覆うようにシリコン基板1上に設けられた層間絶縁膜21と、層間絶縁膜21上にAlパッド31を介して設けられたバンプ電極41とを有し、バンプ電極41下方の領域のシリコン基板1には、トランジスタとしてゲート電極11の周縁部下のシリコン酸化膜が当該ゲート電極11の中央部下のシリコン酸化膜よりも厚いMOSトランジスタ10のみが設けられ、それ以外の領域のシリコン基板1には、トランジスタとしてゲート電極の中央部下からその周縁部下にかけてのシリコン酸化膜の厚さが均一なMOSトランジスタ70が設けられている。

(もっと読む)

半導体装置およびその製造方法

【課題】信頼性の高い半導体装置を提供する。また、ICテストを安定的に行いつつ、半導体装置を製造する技術を提供する。

【解決手段】プローブを用いたICテストを行った後のパッド部は第2のパッシベーション膜158で被覆されている。そのため、ICテストの後に施されるバリアメタルの除去工程において使用されるウェットエッチング用の薬液から、ICテストの実施によって部分的に薄くなったパッド部を保護することができる。したがって、パッド部を介した、ICチップ内への薬液の侵入を抑制することができる。また、半導体装置100においては、プローブを用いたICテストを行うパッド部と、金属バンプ電極162を形成するための開口部とが分離されている。そのため、ICテストによって生じたプローブ痕164の影響が金属バンプ電極162の形状に及ぶことを抑制することができる。

(もっと読む)

1 - 17 / 17

[ Back to top ]