Fターム[5F044JJ05]の内容

ボンディング (23,044) | ワイヤボンディング関連事項 (221) | 冷却に関するもの (9)

Fターム[5F044JJ05]に分類される特許

1 - 9 / 9

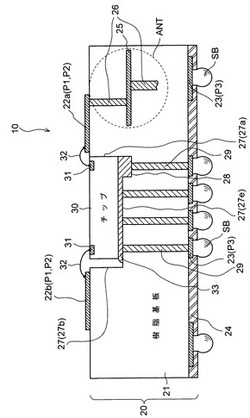

半導体装置

【課題】ミリ波帯等の高周波伝送線路に介在されるワイヤボンディング長を短くし、その部分の寄生インダクタンスの影響による信号品質の劣化を抑制するとともに、放熱性を高めること。

【解決手段】半導体装置10は、半導体素子(チップ)30が配線基板20に形成されたキャビティ27内にその底面との間に接着材料33を介在させて搭載され、チップの電極端子31がキャビティ周囲の基板上に形成された配線部分22a,22bにワイヤ32を介して接続された構造を有する。チップ30は、配線部分のうち他の配線に比べて高周波用の配線22aが形成されている領域に近い側のキャビティの側壁27aに密着して搭載され、チップ30を密着させた側のキャビティの底面27eに凹部28が設けられ、さらにこの凹部の底面から基板外部に繋がるサーマルビア29が設けられている。

(もっと読む)

電力用半導体装置および電力用半導体装置の製造方法

【課題】 信頼性が高く、損失低減と短絡時の耐量向上を両立させた電力用半導体装置を得ることを目的とする。

【解決手段】 絶縁性の基板1と、絶縁性の基板1の主面1fに形成された複数の配線2と、複数の配線2のうちの第1の配線2aに接合された半導体素子3と、半導体素子3の第1の配線2aとの接合面と反対側になるソース電極3fの一部と、複数の配線2のうちの第2の配線2bとを電気的に接続するワイヤ4と、を備え、ソース電極3fには、複数の金属塊5が分散して接合され、複数の金属塊5のそれぞれは、ソース電極3fとの接合面以外が絶縁物7で覆われている。

(もっと読む)

実装装置における冷却構造及び冷却方法

【課題】レンズ、ハーフミラー、プリズムといった光学系部材の熱膨張を防ぐことができるとともに、被接合物周囲の空気層のゆらぎを解消し、同時に、全体の厚さを薄くして小型化に貢献することができる実装装置における冷却構造及び冷却方法を提供する。

【解決手段】光学系機器10の筐体11内に形成された収納空間11Aに、光学系機器10の光路13と、冷却用エアーが供給されるエアー流路20とを共に設ける。

(もっと読む)

半導体装置

【課題】ボンディング点で局所的に熱が発生する場合に、半導体チップの表面の広い範囲に効率的に伝熱し、ボンディング点が局所的に過熱してワイヤと表面電極の接合強度が劣化する現象の発生を抑制する。

【解決手段】ワイヤ22がボンディングされている表面電極16の表面に、表面電極16よりも熱伝導率が高い材料の被覆層20が形成されている。ワイヤ22がボンディングされている表面電極16の表面に、表面電極16よりも熱伝導率が高い材料をコーティングすれば、半導体チップ14の表面の広い範囲に効率的に伝熱することができ、ボンディング点が局所的に過熱されてしまう現象の発生を防止できる。あるいは、表面電極に表面被覆層を介してワイヤをボンディングしてもよい。この場合は、表面電極の表面に、表面電極よりも熱伝導率が高い材料で、表面電極よりも厚く形成されている被覆層を形成する。

(もっと読む)

半導体素子とそれを用いた半導体装置

【課題】半導体素子の実装方法の違いによるコストアップを抑制する。

【解決手段】半導体素子10は、集積回路を有する基板11と、集積回路に対して同じ接続機能を有する電極として、基板11の同一主面11a上に、ワイヤー接続用電極1b、2b、3b及び4b及びバンプ接続用電極1a、2a、3a及び4aを備える。

(もっと読む)

電力用半導体装置

【課題】小型でかつ高い信頼性を有する電力用半導体装置を提供する。

【解決手段】モールド樹脂6から複数のリード1が突出した電力用半導体装置100が、第1ダイパッド部1bを含む第1リード1aと、第1ダイパッド部の表面に載置されたパワーチップ2と、第2ダイパッド部を含む第2リード1cと、第2ダイパッド部上に載置された制御チップ3と、パワーチップと制御チップとを接続する金を主成分とするワイヤ4と、第1リードと第2リードの端部がそれぞれ突出するように制御チップとパワーチップとを埋め込むモールド樹脂とを含み、ワイヤは、その第1端部が制御チップにボールボンディングされ、その第2端部がパワーチップにステッチボンディングされる。

(もっと読む)

パワー半導体装置

【課題】 熱集中による温度上昇が低減されたパワー半導体装置を提供する。

【解決手段】 パワー半導体素子の縦横比を1.5以上にする。これにより、周囲に対する放熱性を高めて、電流密度の高いパワー半導体素子でも効率のよい温度領域で動作させることが可能となる。さらに、ソース電極2から主電流を取り出すワイヤ61〜87の本数を14本以上とし、方向を異なる2方向に分散させる。2方向に分散したワイヤの先は、同一の配線電極42に接続される。

(もっと読む)

半導体装置

【課題】大電力用の半導体素子において、温度上昇分布をより均一にすることである。

【解決手段】電流が大きいために、上部電極層48の抵抗の場所的分布の影響を受け、上部電極層48内における複数の接続部50の平面配置条件に依存して半導体素子の温度上昇分布が定まる大電流用の半導体素子において、パターン2のようにジグザク状に接続部50を配置するのと、パターン1のように1列に接続部50を配置するとのでは、温度上昇分布が明らかに異なる。このことはシミュレーションの結果と定性的によい一致を示す。この他に、各ワイヤのそれぞれが、上部電極層48との間で複数の接続部を形成するようにしてもよい。

(もっと読む)

配線基板及び半導体装置

【課題】 半導体素子が搭載された状態で加熱しても該半導体素子が剥離することのない信頼性の高い配線基板、及び半導体装置を提供すること。

【解決手段】 矩形状のダイアタッチ領域内にサーマルビア203が複数備えられ、少なくともこのサーマルビア203の内部及び該サーマルビア203の半導体素子搭載面側の開口端縁近傍にソルダレジスト107が形成される配線基板において、上記複数のサーマルビア203が、上記矩形状のダイアタッチ領域のコーナー部以外の部分に配置されることを特徴とする配線基板202による。

(もっと読む)

1 - 9 / 9

[ Back to top ]