Fターム[5F044KK02]の内容

ボンディング (23,044) | フェイスダウンボンディング用配線基板 (5,003) | 基板 (2,939) | 樹脂基板 (931)

Fターム[5F044KK02]の下位に属するFターム

フレキシブル基板 (427)

Fターム[5F044KK02]に分類される特許

41 - 60 / 504

配線基板およびその製造方法

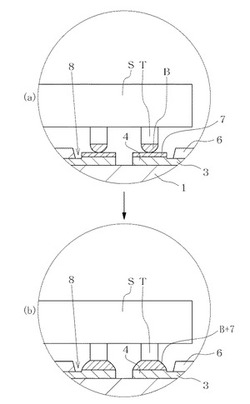

【課題】半導体素子接続パッドを形成する配線導体とソルダーレジスト層との間に半田が滲入して潜り込むことを有効に防止し、半導体素子の電極端子と半導体素子接続パッドとを接合する半田が不足することがなく両者を良好に接続することが可能であるとともに、ソルダーレジスト層が剥がれることがなく配線導体の絶縁信頼性に優れる配線基板を提供すること。

【解決手段】絶縁基板1と、絶縁基板1の上面に形成された銅から成る配線導体3と、絶縁基板1および配線導体3上に被着されており、配線導体3の一部を半導体素子接続パッド4として露出させる開口部6aを有するソルダーレジスト層6と、半導体素子接続パッド4の上面に被着された錫めっき層7とを備えた配線基板10であって、配線導体3における半導体素子接続パッド4とソルダーレジスト層6との間に配線導体3が銅のままで露出する銅露出部8が形成されている。

(もっと読む)

半導体装置の製造方法

【課題】配線を設計通りの形状に形成することができる半導体装置の製造方法を提供する。

【解決手段】本発明に係る半導体装置の製造方法は、半導体基板と、前記半導体基板の第1の面に位置する電極と、前記第1の面に設けられ、前記電極とオーバーラップする位置に開口部を有する絶縁膜と、を有する構造体を用意する工程と、前記絶縁膜の前記第1の面側の面とは反対側の第2の面に、樹脂突起を形成する工程と、前記電極および前記樹脂突起を覆う第1導電膜を前記第2の面に形成する工程と、前記第1導電膜の前記第2の面側の面とは反対側の第3の面に、前記第1導電膜の前記第3の面より反射率の低い第2導電膜を形成する工程と、前記第2導電膜の前記第3の面側の面とは反対側の第4の面に、フォトレジスト層を形成する工程と、前記フォトレジスト層の一部をマスク層で覆った状態で、前記フォトレジスト層を露光する工程と、前記フォトレジスト層を現像し、フォトレジストパターンを形成する工程と、前記フォトレジストパターンをマスクとして前記第1導電膜および前記第2導電膜をエッチングすることにより、前記第1導電膜から形成された配線であって、前記樹脂突起の少なくとも一部を覆い、かつ、前記電極と接続する前記配線を形成する工程と、を有する。

(もっと読む)

半導体装置およびその製造方法

【課題】多層プリント配線板の上面側に設けられた凹部内にCSPと呼ばれる半導体構成体を搭載した半導体装置において、凹部の底面に半導体構成体搭載用の半田を特殊な設備を用いることなく供給する。

【解決手段】多層プリント配線板1の凹部4内に、複数の円孔12を有し、且つ、前記円孔12内およびその上下に突出して設けられた半田ボール13aを有する半田支持シート11を配置する。次に、その上に半導体構成体21をフェースダウン方式で配置する。次に、リフローを行うことにより、多層プリント配線板1の凹部4内において半田支持シート11上に半導体構成体21をフェースダウン方式で搭載する。

(もっと読む)

半導体装置、及びその製造方法

【課題】ピラーを確実に配置することが可能な半導体装置、及びその製造方法を提供する。

【解決手段】本発明の一態様にかかる半導体装置30は、内部回路領域20と、内部回路領域20の外側に設けられたI/O領域10と、を備える半導体チップ1と、半導体チップ1とフリップチップ接続されたパッケージ基板6と、半導体チップ1とパッケージ基板6との間に配置され、半導体チップ1の最上層配線層12に含まれる2本以上の接地配線12a上に形成されて、2本以上の接地配線12aを接続する導電性のピラー4と、を備えるものである。

(もっと読む)

接着剤組成物、半導体装置の製造方法及び半導体装置

【課題】半導体チップ及び配線回路基板のそれぞれの接続部が互いに電気的に接続された半導体装置、又は、複数の半導体チップのそれぞれの接続部が互いに電気的に接続された半導体装置において、接続部を封止するための接続信頼性及び絶縁信頼性に優れた接着剤組成物、それを用いた半導体装置の製造方法、及び半導体装置の提供。

【解決手段】エポキシ樹脂と、硬化剤と、ビニル系表面処理フィラーとを含有する接着剤組成物。

(もっと読む)

接続構造体の製造方法及び塗布装置

【課題】電極間の位置ずれを抑制できる接続構造体の製造方法を提供する。

【解決手段】接続構造体1の製造方法は、電極2bを上面2aに有する第1の接続対象部材2上に、ディスペンサーを移動させながら、異方性導電ペーストをディスペンサーから塗布して、異方性導電ペースト層を形成する工程と、異方性導電ペースト層の少なくとも一部の領域を、除去装置により除去する工程と、異方性導電ペースト層上に、電極4bを下面4aに有する第2の接続対象部材4を積層する工程と、異方性導電ペースト層を加熱して本硬化させて、硬化物層3を形成する工程とを備える。除去装置により除去する前の異方性導電ペースト層3Aにおいて、第1の領域を除去装置14により除去するか、又は塗布量が多い第2の領域を除去装置により除去する。

(もっと読む)

導電性接合材料、導体の接合方法、及び半導体装置の製造方法

【課題】導電性接合材料を基板の電極に供給しつつ溶着する導電性接合材料供給工程、及び電子部品の端子に導電性接合材料を一度溶融させて転写する転写工程を選択することができ、基板と電子部品を150℃以下の低温で効率よく接合することができる導電性接合材料及び導体の接合方法、及び半導体装置の製造方法の提供。

【解決手段】融点が150℃以上の高融点金属粒子と、融点が80℃以上139℃以下の中融点金属粒子と、融点が79℃以下の低融点金属粒子とからなる金属成分を含む導電性接合材料である。前記金属成分が、高融点金属粒子表面に、中融点金属粒子から形成された中融点金属層と、低融点金属粒子から形成された低融点金属層とをこの順に有する多層金属粒子である態様などが好ましい。

(もっと読む)

接続構造体の製造方法

【課題】電極間の導通信頼性を高めることができる接続構造体の製造方法を提供する。

【解決手段】本発明に係る接続構造体1の製造方法は、電極2bを上面2aに有する第1の接続対象部材2上に、異方性導電材料層3Aを配置する工程と、異方性導電材料層3Aに光を照射することにより硬化を進行させて、異方性導電材料層3AをBステージ化する工程と、Bステージ化された異方性導電材料層3Bの上面3aに、電極4bを下面4aに有する第2の接続対象部材4をさらに積層する工程とを備える。異方性導電材料層3AをBステージ化する際に、Bステージ化された異方性導電材料層3Bの温度範囲23〜120℃における最低溶融粘度を示す温度での貯蔵弾性率G’を5×102Pa以上、1×105Pa以下にする。導電性粒子5の170℃で20%圧縮変形したときの圧縮弾性率は5.9×102N/mm2以上、5.9×103N/mm2以下である。

(もっと読む)

保護層形成用フィルム

【課題】 半導体装置の製造の際の工程数の増加を抑制しつつ、半導体ウエハが有する低誘電材料層のクラックを防止することを可能とする保護層形成用フィルムを提供すること。

【解決手段】 低誘電材料層が形成されているバンプ付きウエハに保護層を形成するための保護層形成用フィルムであって、支持基材と粘着剤層と熱硬化性樹脂層とがこの順で積層されており、熱硬化性樹脂層の溶融粘度が、1×102Pa・S以上2×104Pa・S未満となり、且つ、粘着剤層のせん断弾性率が、1×103Pa以上2×106Pa以下となる温度が50〜120℃の温度範囲内に存在する保護層形成用フィルム。

(もっと読む)

液状封止樹脂組成物および液状封止樹脂組成物を用いた半導体装置

【課題】高熱伝導率と低誘電率、高隙間流入性とを兼備した液状封止樹脂組成物を提供すること。

【解決手段】半導体素子と基板とをバンプ接続した後、半導体素子と基板との隙間を封止する際に用いる液状封止樹脂組成物であって、(A)エポキシ樹脂、(B)硬化剤、(C)無機充填材を含有し、(C)無機充填材が球状アルミナと球状シリカとの混合物を含み、且つ(D)塩基性化合物を含有することを特徴とする液状封止樹脂組成物であり、好ましくはpH値が7以上である液状封止樹脂組成物。

(もっと読む)

アンダーフィル樹脂組成物およびこれを用いた半導体装置

【課題】 アンダーフィルにより樹脂封止された半導体チップを、樹脂残渣少なく且つ基板表面を傷つけることなく配線基板から取り外すことができるようにする。

【解決手段】 配線基板10上にはんだバンプ8を介して半導体チップ1が搭載され、封止樹脂9により封止されている半導体装置において、封止樹脂9にはシロキサン骨格を有する多層構造の粒子が添加されている。半導体チップ1をリペアする際には、加熱して封止樹脂9の密着強度を低下させた状態で剥離用プレート12を、配線基板10と半導体チップ1との隙間に挿入して〔(b)図〕、封止樹脂9を配線基板10から剥離し、半導体チップ1を取り除く〔(c)図〕。

(もっと読む)

ICタグ

【課題】製造コストの高騰を招くことがなく、ICチップの破損を防止できるICタグを提供する。

【解決手段】回路基材11と、前記回路基材11の回路電極にフリップチップ方式により接合材を用いて実装されたICチップ13と、前記回路基材11の回路面に設けられた保護層311とを備えたICタグ1であって、前記ICチップ13の周縁には、前記接合材の硬化体からなるフィレットが形成され、前記フィレットは、前記ICチップ13を補強する補強部を備え、前記補強部は、前記ICチップ13の側面を被覆するとともに、前記側面に沿った高さ寸法と前記ICチップ13の高さ寸法とが略等しくされた状態が、前記ICチップ13の実装面に沿った方向に所定寸法延長された形状に形成され、前記保護層311は、ウレタン系オリゴマーと、エネルギー線硬化性モノマーとを含んで構成されている。

(もっと読む)

接着剤及び電気装置

【課題】低温、短時間の条件で硬化し、かつ、接続信頼性の高い接着剤を提供する。

【解決手段】接着剤は金属キレートと、シランカップリング剤と、熱硬化性樹脂とを有しており、シランカップリング剤のアルコキシ基が接着剤中で加水分解され、シラノール基となる。このシラノール基と金属キレートとが反応することによって接着剤中にカチオンが放出されると、そのカチオンによって熱硬化性樹脂であるエポキシ樹脂がカチオン重合する。このように、接着剤はカチオン重合によって硬化されるので、低い温度でも接着剤が硬化する。

(もっと読む)

回路基板及び電子装置

【課題】開示の技術によれば、回路基板の表面に形成される保護膜の膜厚の抑制と、該保護膜による回路基板の表面保護と、を実現しつつ、電極パッドに供給される半田ペーストを増加することができる。

【解決手段】

少なくとも電子部品がハンダ接続により搭載される電極パッド領域を除き表面保護膜が形成された回路基板であって、上記表面保護膜は多層で構成され、上記電極パッド領域の開口面積が下層から上層に向かって拡大する部分を有する回路基板。

(もっと読む)

半導体装置の製造方法

【課題】半導体チップ同士を積層する際に生じる曲げモーメントによる破損を防止する半導体装置の製造方法を提供する。

【解決手段】一面に形成された表面バンプFB及び積層方向から見て表面バンプFBと重なるように他面に形成された裏面バンプBBを含むコアチップCC1と、一面に形成された表面バンプFB及び積層方向から見て表面バンプFBと重ならないように他面に形成された裏面バンプBBを含むインターフェースチップIFとを準備し、コアチップCC1の裏面バンプBBとインターフェースチップIFの表面バンプFBが接続するように、インターフェースチップIFの裏面バンプBBに対応する位置に凹部GRを有するボンディングツールBTを用いて積層方向に重ね合わせる。これにより、積層時にチップに曲げモーメントが発生しないことからチップの破損を防止することが可能となる。

(もっと読む)

回路接続材料、これを用いたフィルム状回路接続材料、回路部材の接続構造及び回路部材の接続方法

【課題】 高精細回路における隣接する回路間の絶縁性の確保と、対向する回路間の導通性の確保とを両立させることが可能な回路接続材料を提供すること。

【解決手段】 相対峙する回路電極間に介在され、相対向する回路電極を加圧し加圧方向の電極間を電気的に接続する回路接続材料であって、有機絶縁物質中に導電性微粒子を分散させた異方導電粒子を含有する、回路接続材料。

(もっと読む)

半導体搭載用基板、半導体装置及び半導体装置の製造方法

【課題】 絶縁層から突出する電極からなるパッドを備えながら、信頼性の高い半導体装置を提供する。

【解決手段】 最下層の第1導体パターン58と外部基板接続用のパッド60Pを形成する電極体60との間に、第1絶縁層50が介在しているので、第1導体パターン58とパッド60Pとの間で短絡が発生し難い。また、パッド60Pを構成する電極体60の露出部分に対して、外部基板への実装の際に応力が加わっても、該電極体60は露出部分以外は第1絶縁層50により保護が図られるので、電極体60にクラック等が生じ難い。

(もっと読む)

半導体発光装置及びその製造方法

【課題】回路基板にバリスタペーストを塗布し静電気による破壊に対する防御手段を持たせる際、塗布量や塗布配置に対し高い精度が要求されず製造し易くする。

【解決手段】回路基板42は、導電性のポスト57,58を除く上面全体にバリスタ56を備え、ポスト57とバリスタ56の上面が同じ高さになっている。つまりポスト57,58の形成後、バリスタ56を塗布し研磨すれば良い。この回路基板42にLED素子43をフリップチップ実装する。

(もっと読む)

半導体素子およびフリップチップ相互接続構造を形成する方法

【課題】半導体素子を作製する方法を提供する。

【解決手段】半導体ダイの能動表面上に形成された複数のバンプを有する、半導体ダイを提供するステップと、基板を提供するステップと、前記基板上に相互接続部位を伴う複数の伝導性トレースを形成するステップであって、前記バンプは、前記相互接続部位よりも幅広い、ステップと、前記接続部位から離れた前記基板の領域上にマスキング層を形成するステップと、前記バンプが前記相互接続部位の頂面および側面を覆うように、前記バンプを前記相互接続部位に接着するステップと、前記半導体ダイと基板との間で前記バンプの周囲に封入材を堆積させるステップと、を含む、半導体素子を作製する方法。

(もっと読む)

配線基板のはんだバンプ平坦化方法および配線基板のはんだバンプ平坦化装置

【課題】基板本体を薄くした場合にもはんだバンプを均一に平坦化することができる配線基板のはんだバンプ平坦化方法および配線基板のはんだバンプ平坦化装置を提供する。

【解決手段】配線基板40における基板本体41の一方の面に複数のはんだバンプ42が形成されている。配線基板40に対し上治具30の下面30aを複数のはんだバンプ42に押し当てて複数のはんだバンプ42を平坦化する。基板本体41の厚さは0.5mm以下であるとともに、はんだバンプ42は3000個以上形成されている。はんだバンプ平坦化の際に、複数のはんだバンプ42を常温で上治具30により圧力を加えることにより複数のはんだバンプ42を平坦化する。

(もっと読む)

41 - 60 / 504

[ Back to top ]