Fターム[5F044KK02]の内容

ボンディング (23,044) | フェイスダウンボンディング用配線基板 (5,003) | 基板 (2,939) | 樹脂基板 (931)

Fターム[5F044KK02]の下位に属するFターム

フレキシブル基板 (427)

Fターム[5F044KK02]に分類される特許

121 - 140 / 504

半導体モジュールおよびその製造方法、ならびに携帯機器

【課題】半導体モジュールの実装信頼性を向上させる。

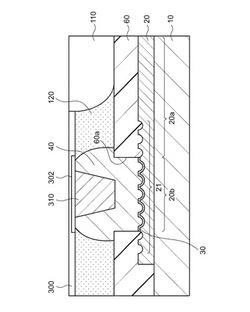

【解決手段】半導体モジュールは、配線領域20aとこれに接続された電極領域20bを含み、Cuからなる配線層20と、電極領域20bと半導体素子300の素子電極302とを電気的に接続し、Snを含むはんだボール40と、を備える。電極領域20bは、はんだボール40と接する側の主表面が粗面であり、はんだボール40と接する表層部分にCuとSnの合金を含む合金層30を有し、主表面の表面粗さRmaxが合金層30の層厚よりも大きい。

(もっと読む)

半導体装置の製造方法

【課題】チップの搭載を短時間で確実に実施できるようにする。

【解決手段】基板10上にBステージ化したフィルム接着剤21を設け、フィルム接着剤21を介してチップ1を基板10に仮固定する。さらに、チップ1上に封止フィルム41を供給してから、プレスヘッド43で押圧する。プレスヘッド43の温度を調整して、最初に封止フィルム41のみを軟化させてチップ1間の空間40に封止フィルム41の材料を充填させる。次に、プレスヘッド43の温度を上昇させ、フィルム接着剤21を軟化させてバンプ2と電極パッド13Aを接続させる。この後、プレスヘッド43の温度をさらに上昇させてフィルム接着剤21及び封止フィルム41をCステージ化する。

(もっと読む)

回路基板およびその製造方法

【課題】フリップチップ実装のための回路基板の銅配線をセミアディティブ法で形成した場合、その接続パッド部にすずなどの溶融金属を付着形成する工程で、特にシード膜が溶食し、接続パッドが細って断線障害などを生じるケースがある。

【解決手段】絶縁基板上に銅シード膜上に感光樹脂パターンを形成し、その開口部へ銅の埋め込み配線パターンを形成した後、ウエットブラスト法での選択的エッチングで、埋め込み配線パターンの頂部及び側面部を感光性樹脂膜から露出させる。その露出部に無電解置換めっき法ですずめっきパターンを付着形成する。次いで、そのめっきパターンをマスクに再度ウエットブラスト法で残りの感光性樹脂膜を除去する。この工程で溶融金属はシード膜に触れず溶食されない。また本工程の結果、実装工程でも両者は接触しないため構造のため、シード膜の溶食が発生せず、実装時でのパターンの細りも抑制される。

(もっと読む)

半導体装置及び電子機器

【課題】 本発明では剥離技術を用いることにより様々な基板上に薄膜素子を形成し、従

来の技術では不可能であると考えられていた部分に薄膜素子を形成することにより、省ス

ペース化を図ると共に耐衝撃性やフレキシビリティに優れた半導体装置を提供する。

【解決手段】 本発明では、剥離技術を用いて一旦基板から剥離させた膜厚50μm以下

の素子形成層を基板上に固着することにより、様々な基板上に薄膜素子を形成することを

特徴とする。例えば、可撓性基板上に固着された薄膜素子をパネルの裏面に貼り付けたり

、直接パネルの裏面に固着したり、さらには、パネルに貼り付けられたFPC上に薄膜素

子を固着することにより、省スペース化を図ることができる。

(もっと読む)

半導体装置の製造方法

【課題】半導体素子に設けられた突起電極と回路基板に設けられたはんだ電極とを接合する際に、突起電極とはんだ電極との位置ずれを低減し、突起電極を被覆した鼓状の接合電極を形成することが可能な半導体装置の製造方法を提供する。

【解決手段】突起電極15が設けられた半導体素子10と、固相液相共存領域を有する組成のはんだ電極25cが設けられた回路基板20とを、突起電極とはんだ電極とが対向するように位置合わせする第1工程と、はんだ電極を固相液相共存領域まで加熱し、所定時間保持する第2工程と、第2工程の後、はんだ電極を液相領域まで加熱する第3工程と、を有する。

(もっと読む)

バンプ付き配線基板、バンプ付き電子部品及び実装構造体

【課題】電気的信頼性を向上させる要求に応えるバンプ付き配線基板、バンプ付き電子部品及び実装構造体を提供する。

【解決手段】バンプ付き配線基板は、絶縁層10と絶縁層10上に設けられた導電層11とを有する配線基板3と、導電層11上に設けられ、導電層11と電気的に接続されたバンプ4と、配線基板3の表面からバンプ4の表面にかけて連続的に設けられた無機絶縁構造体13と、を備えていることを特徴とする。

(もっと読む)

半導体装置の製造方法

【課題】半導体装置の製造方法における歩留まり低下を防ぐ。

【解決手段】基材60上に絶縁膜30を積層する第1工程と、絶縁膜30にビアホール31を形成する第2工程と、絶縁膜30上に導体層を形成しパターニングすることで、ビアホール31上に貫通穴41a、42aを有する配線41、42を形成する第3工程と、貫通穴41a、42aの上部に電極12が配置されるように半導体チップ11をフェースダウンボンディングする第4工程と、を含む半導体装置1の製造方法である。

(もっと読む)

電子部品パッケージおよびその製造方法

【課題】位置ずれにも拘わらず導電パッドに導電バンプを確実に接続することができる電子部品パッケージおよびその製造方法を提供する。

【解決手段】LSIチップパッケージ15では、パッケージ基板16上で導電パッド23、23同士の間にソルダーレジスト29が配置される。導電パッド23のパッド面25とソルダーレジスト29の頂上面31とは共通の仮想平面26内に配置される。したがって、パッケージ基板16に対するLSIチップ22の位置が例えばパッケージ基板16の表面に平行に規定の位置からずれたとしても、導電バンプ27の先端は例えば導電パッド23のパッド面25とソルダーレジスト29の頂上面31との両方に受け止められる。導電パッド23、23同士の間への導電バンプ27の落下は確実に防止される。その結果、導電バンプ27の位置のずれにも拘わらず導電バンプ27は導電パッド23に確実に接合される。

(もっと読む)

電子部品の実装方法、およびソルダーマスクの設計方法

【課題】下面に多数の端子を備えた電子部品をリフロー方式によって基板に実装する際、基板などの反りに起因する半田の接続不良や短絡を、信頼性を低下させたり、コストを増加させたりすることなく、確実に防止する。

【解決手段】多数の端子のそれぞれを対応するランドに対向配置させた状態で、各端子とランドとをリフロー方式によって半田付けする際、互いに対向する端子とランドとの間に供給する半田の量を、各端子とそれらに対応する各ランドのそれぞれの距離に応じて個別に増減する。

(もっと読む)

フィルム状接着剤、フィルム状異方導電性接着剤

【課題】製造工程において、高度な分散技術を必要とせず、また品質管理に多大な労力を費やすことなく、ボイドの発生を効果的に抑制することができることができるフィルム状接着剤を提供する

【解決手段】本発明に係るフィルム状接着剤は、分子量10000以上のフェノキシ樹脂と、エポキシ基を含んだアクリルモノマーをラジカル重合させることにより生成されたラジカル重合物を含む第1のエポキシ樹脂と、潜在性硬化剤と、前記潜在性硬化剤との反応性を有する第2のエポキシ樹脂とを含有する。

(もっと読む)

配線基板および配線基板の製造方法

【課題】種々の部品を搭載する配線基板の信頼性を向上する。

【解決手段】層間絶縁層14から露出する電極パッド4a、6aを有する配線基板20Aを備えた半導体パッケージ30Aであって、電極パッド4a、6aはそれぞれ層間絶縁層14の表面からの深さが互いに異なって露出している。配線基板20Aには、半導体チップ21およびリッド23が搭載され、半導体チップ21の主面に形成されている外部接続端子22と、電極パッド4aとが電気的に接続され、リッド23に形成されている接続部23bと、電極パッド6aとが電気的に接続され、半導体チップ21の裏面にリッド23が接着して配置される。

(もっと読む)

回路板及び回路板の製造方法

【課題】回路部材間の接着剤層におけるボイド発生が十分に抑制され、ピッチ間が十分に封止充填されており、且つ接続信頼性に優れる回路板を提供すること、及び当該回路板の製造方法を提供すること。

【解決手段】高さtcの第一の突起電極と該第一の突起電極上に形成された高さtmのハンダを有する第一の回路部材と、高さtsの第二の突起電極を有する第二の回路部材とを、上記第一の突起電極と上記第二の突起電極を対向して配置し、対向配置した上記第一の突起電極と上記第二の突起電極の間に厚さt2の接着剤層を介在させ、加熱加圧して、下記式(1)、(2)及び(3)を満たすように対向配置した上記第一の突起電極と上記第二の突起電極を電気的に接続させてなる、回路板。

t1≧tc+ts (1)

t1×1.3≧t2>tc+tm (2)

t1×1.3≧t2>tc+ts (3)

[式中、t1は加熱加圧後の前記第一の回路部材と前記第二の回路部材の間の積層方向に沿った距離を示し、tcは第一の突起電極の高さを示し、tsは第二の突起電極の高さを示し、t2は加熱加圧前の接着剤層の厚さを示し、tmは第一の突起電極上に形成されたハンダの高さを示す。]

(もっと読む)

半導体装置

【課題】封止層中のボイドの形成を防止できる半導体装置を提供する。

【解決手段】この半導体装置1は、配線基板2と、この配線基板2の表面2aに機能面3aを対向させて接続された半導体チップ3とを含んでいる。配線基板2の表面2aには、矩形状の接続パッドが形成されており、配線基板2と半導体チップ3とは、接続パッドに接続された接続部材5によって、所定間隔を保つように接合され、かつ互いに電気的に接続されている。配線基板2の表面2aには、ソルダレジスト膜6が形成されている。ソルダレジスト膜6には、表面2aを垂直に見下ろす平面視において、半導体チップ3よりも大きなサイズ、すなわち、その内部に半導体チップ3が完全に含まれるように形成された開口6aが設けられている。配線基板2の表面2aに設けられ接続部材5に接続された配線により形成された段差を除き、開口6a内には段差が形成されていない。

(もっと読む)

圧着装置および保護シートの交換方法

【課題】ディスプレイパネル基板と半導体部品とを異方性導電膜を圧着して電気的に接続するときに用いる保護シートの交換を容易に行なうことのできる圧着装置を提供する。

【解決手段】圧着装置において、保護シート100のシートエンド検出器150と、保護シートカッター110と、新旧の保護シートを接続するための接続テープの供給部111と、新旧の保護シートへの接続テープの貼り付け位置の基準となる基準ローラ121と、基準ローラ121に対向して配置され、接続テープと新旧の保護シートを基準ローラで挟み込むことにより接続テープを新旧の保護シートに貼り付けるための押し当てローラ122と、接続テープを切断するための接続テープカッター113とを有する。

(もっと読む)

配線基板および半導体装置

【課題】ペリフェラル状配置のバンプとエリアアレイ状配置のバンプとが混在する半導体チップがフリップチップ接合される、電気的特性に優れた配線基板を提供する。

【解決手段】配線基板1は、半導体チップのバンプとフリップチップ接合される接続パッド11、12を備えた配線基板であって、前記配線基板の周辺部1aの接続パッド11は、ノン・ソルダーマスク・デファイン構造で形成され、前記配線基板1の中央部1bの接続パッド12は、ソルダーマスク・デファイン構造で形成されている。

(もっと読む)

部品内蔵配線基板の製造方法

【課題】フリップチップ実装後のウェット洗浄を排して、バンプの接合性などの実装品質を確保することができる部品内蔵配線基板の製造方法を提供する。

【解決手段】複数の配線層を積層して構成されコア層1にバンプ付きの電子部品7が実装された部品内蔵配線基板の製造において、部品搭載後のコア層1において電子部品7との隙間に樹脂を注入して硬化させて封止する樹脂封止工程後において、電子部品7が実装された実装面側をプラズマ処理することによって実装面側に形成された配線回路3の表面3bに生成した酸化膜3cを除去する方法を採用する。これにより、フリップチップ実装後のウェット洗浄を排することができ、ウエット洗浄に起因するバンプの接合性低下などの不良を防止して実装品質を確保することができる。

(もっと読む)

電子部品、並びに、接合体及びその製造方法

【課題】マイグレーションによる腐食及び剥離を防止することができると共に、異方性導電フィルムの充填効率を向上させることができる電子部品、並びに、接合体及びその製造方法の提供。

【解決手段】基材と、前記基材上に立設され、少なくとも表面が導電性部材で形成され、突出部を有する電極とを有し、前記突出部の突出方向に平行な断面における、該突出部の基部に形成された角部に、被覆材が被覆され、前記被覆された被覆材の最大高さが、前記電極の最大高さの90%以下である接合体である。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】半導体チップ上の樹脂厚にバラツキが少ない樹脂封止が可能で、製造コストを低減できる半導体装置の製造方法および半導体装置を提供する。

【解決手段】複数の単位回路パターン11を有するインターポーザ10にフリップチップ接続された複数の半導体チップ20上にフィルム状の封止樹脂を搭載する工程と、複数の半導体チップ上に封止樹脂が搭載されたワークを真空状態にてプレスして複数の半導体チップを樹脂封止する工程とを含む。複数の半導体チップを樹脂厚にバラツキが少ない封止樹脂で封止することができる。また、モールド成型のように高価な金型を必要としないため製造コストを削減することができる。

(もっと読む)

半導体装置の製造方法およびこの方法に用いる圧力容器

【課題】コストの低減を図りつつ、半導体チップのバンプと基板のパッドとの良好な半田接合を得ることができ、かつ接合信頼性を向上させた半導体装置の製造方法およびこの方法に用いる圧力容器を提供する。

【解決手段】バンプ4を有する複数の半導体チップ3を基板1上にフリップチップ実装して半導体装置を製造する半導体装置の製造方法は、以下の工程を含む。複数の半導体チップ3を、各バンプ4が基板1上の各パッド2表面の半田層5上に載るように、基板1上に配置する工程。複数の半導体チップ3が基板1上に配置されたワークWを圧力容器8に入れる工程。圧力容器8中の気圧を、ワークWを加熱する際の最高温度における接着剤層6に含まれる溶剤の蒸気圧よりも高くし、この状態で、ワークWをヒータ12により加熱し、半田層5を溶融させる工程。

(もっと読む)

インターポーザとその製造方法、並びにそのインターポーザを用いた半導体装置及びその製造方法

【課題】レーザー光の照射によって貫通孔をする場合であっても、反りの発生しないインターポーザとその製造方法、並びにそれを用いた半導体装置とその製造方法を提供する。

【解決手段】インターポーザの基板コア材1に形成される貫通孔5が、半導体チップ搭載側から形成される貫通孔5aと、実装側から形成される貫通孔5bとで構成されている。さらにこれらの貫通孔5は、1つの半導体装置を構成する単位領域に、両方配置されるように形成する。このように形成されたインターポーザは反りがなく、このインターポーザを用いて半導体装置を形成すると、反りのないインターポーザを備えた半導体装置を形成することができる。

(もっと読む)

121 - 140 / 504

[ Back to top ]