Fターム[5F044KK09]の内容

ボンディング (23,044) | フェイスダウンボンディング用配線基板 (5,003) | 配線パターン (129)

Fターム[5F044KK09]の下位に属するFターム

両面配線 (24)

Fターム[5F044KK09]に分類される特許

21 - 40 / 105

半導体装置

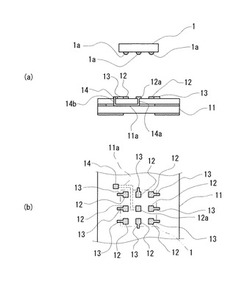

【課題】リフロー処理を行わずに、回路基板へ半導体用パッケージを、簡便に実装し、回路基板から取外すことができる半導体装置を提供する。

【解決手段】回路基板11のランドパターン12に、回路基板に実装されるBGAパッケージIC1の側面よりも外側に位置した熱入力部13を設ける。BGAパッケージICに覆われる部分のランドパターン12aは、バイアホール14a,14bと中間層11aを介して、BGAパッケージICに覆われない回路基板の上面の部分に配した熱入力部14に接続させる。熱入力部を加熱すると、ランドパターンに接触させたバンプ1aが溶融し、ランドパターンに接続される。

(もっと読む)

半導体装置

【課題】フリップチップ実装構造を有する構成にて半導体素子からの放熱性を確保できる半導体装置を提供すること。

【解決手段】この半導体装置1は、被実装対象2を実装対象3に対してバンプ4を介してフリップチップ実装して構成されている。この半導体装置1では、被実装対象2が回路面上であって発熱部の近傍にパッド部を有している。また、実装対象3が熱伝導性材料あるいは放熱性材料から成る実装部32を有している。そして、パッド部と実装部32とがバンプ4を介して接続されることにより、被実装対象2が実装対象3にフリップチップ実装されている。

(もっと読む)

超音波フリップチップ実装方法およびそれに用いられる基板

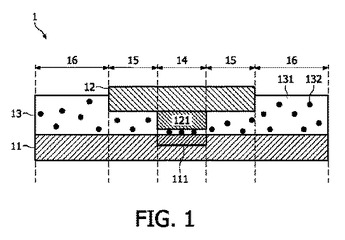

【課題】半導体チップと基板間の電極の接合状態にバラツキの少ない超音波フリップチップ実装方法を提供する。

【解決手段】超音波フリップチップ実装方法は、半導体チップ100の一方の主面に複数のバンプ電極106を形成するステップと、バンプ電極106を、基板上の対応する電極パターン132に接触させ半導体チップに超音波振動を印加するステップとを含む。ここで、電極パターン132は、超音波の振動方向Vに対して斜め方向に配向されている。これにより、電極パターン132の超音波振動に寄与し得る実効的な幅W1(W1>W)を得る。

(もっと読む)

配線基板、半導体装置、半導体モジュールおよびその製造方法

【課題】狭ピッチ配線化を可能にし、かつ、接合信頼性の高い配線基板、半導体装置、半導体モジュールおよびその製造方法を提供する。

【解決手段】主面に半導体素子が実装される配線基板100であって、絶縁性基材2と、実装されるべき前記半導体素子からの引き回し配線として、絶縁性基材2の主面に設けられた配線3と、外部と接続する外部接続端子として、配線3の一部領域に形成される外部接続端子部4、6と、少なくとも絶縁性基材2の主面における前記半導体素子が実装されるべき実装領域と外部接続端子部4、6の接続面とを露出した状態で絶縁性基材2の主面を覆うように形成された絶縁性樹脂7とを備え、絶縁性基材2の主面の法線方向における外部接続端子部4、6の厚さは、配線3における絶縁性基材2の主面の法線方向の厚さよりも厚い。

(もっと読む)

半導体装置とその製造方法、及び回路基板シート

【課題】半導体装置とその製造方法、及び回路基板シートにおいて、回路基板と半導体素子との接続信頼性を高めること。

【解決手段】回路基板20に設けられた接続パッド30の延長部30aに接続媒体35を供給する工程と、回路基板20の接続パッド30と半導体素子37の電極端子38とを対向させる工程と、接続媒体35を加熱して溶融することにより、溶融した該接続媒体35を延長部30aから接続パッド30に伝わせ、接続媒体35を介して接続パッド30と電極端子38とを接続する工程とを有する半導体装置の製造方法による。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】被実装体上に半導体チップが積層された半導体装置において、上側の半導体チップ上へのアンダーフィル材の乗り上げやチップ間でのボイドの発生を防止する。

【解決手段】第1の主面上に配線パターン7が形成された第1の半導体チップと、第1の半導体チップ上でかつ配線パターン7が形成された面上に搭載された第2の半導体チップと、第1の半導体チップと第2の半導体チップとの間に充填され、第2の半導体チップの外周部にフィレットを形成するアンダーフィル材とを備える半導体装置の構成として、第1の半導体チップ上でかつ第2の半導体チップが搭載されるチップ搭載領域15を区画する4つの辺部のうち、フィレットが最も長く形成される辺部15Aの外側に、アンダーフィル材をチップ間に導く導入部18を形成した。

(もっと読む)

RFID用インレット及びその製造方法

【課題】RFID用インレットにおいて入力用のバンプ電極及びGND用のバンプ電極のみの接合強度を測定する。

【解決手段】RFID用インレットの組み立てにおいて、チップ搭載領域4cの第3パターン4fが第1パターン4d及び第2パターン4eから分離されていることにより、超音波を印加してバンプ電極2を金属パターン4に接続する際に、第3パターン4fは梁となるようなパターンによって支持されていないため、超音波の振動に合わせて動く。これにより、チップ支持用のバンプ電極2cと第3パターン4fの接合力を、入力用のバンプ電極2aと第1パターン4dの接合力やGND用のバンプ電極2bと第2パターン4eの接合力に比べて弱くすることができ、バンプ電極2の接続強度検査において、入力用のバンプ電極2a及びGND用のバンプ電極2bのみの接合強度を測定することができる。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】本発明の目的は、ベアチップが高密度実装されたような半導体装置において、ベアチップの全端子を検査することを可能にした検査用パッド及びそれに付随する配線のレイアウトを提供する半導体装置を実現することである。

【解決手段】本発明に係る半導体装置は、ベアチップの全ての端子が配線基板内の特定の配線層を介して、ダミー領域に配置された検査用パッドにそれぞれ接続され、検査完了後は、そのダミー領域が切断されるものである。

(もっと読む)

電子部品用の実装基板

【課題】簡単な構成でワイヤボンディング接続及びフリップチップ接続の双方に対応可能な電子部品用の実装基板を提供する。

【解決手段】この電子部品用の実装基板10では、第2配線部16が、基板11の表裏方向について反転した位置関係にある第1電極パッド13と第2電極パッド14とを接続している。このため、ワイヤボンディング接続で接続する場合と、フリップチップ接続で接続する場合とで電子部品1の実装面2aが実装基板10に対して反転しても、電子部品1側の端子電極3の配列や実装基板10側の外部電極12の配列を変えずに、電子部品側の端子電極3と実装基板10側の外部電極12とを同一に対応付けることができる。また、上記の構成は、第2配線部16のパターニングによって実現でき、基板11や外部電極12の構造に変更を加える必要がないので、構成の複雑化も回避できる。

(もっと読む)

半導体パッケージのリペア、リワーク性の測定方法及びその装置

【課題】 本発明は、リペア、リワーク工程を前提とし、その工程の条件設定等有意義な情報を得るための測定方法及び測定装置を提供することを目的とする。

【解決手段】 半導体チップ及び基板と、この片面を封止する封止樹脂と、前記片面の半対面に形成されるバンプと、前記バンプが接合する実装基板と、アンダーフィル・サイドフィルとを備える半導体パッケージの実装構造において、アンダーフィル或いはサイドフィルした後、硬化した液状樹脂組成物のリペア、リワーク性を定量化するための測定方法及びその測定装置であって、半導体チップ及び基板下部に、実装基板との間に電気的接続をするための半田ボール間を、半田間隙を260℃に耐えられるワイヤーで通し、この状態でアンダーフィル或いはサイドフィルした後、ワイヤーをロードセル或いは圧力センサー等に取り付けたものを、所定の温度に加熱後、引き上げることで荷重を測定する方法。

(もっと読む)

実装基板、表示装置、および電子機器

【課題】表示パネルに対して回路基板をフェイスダウン実装した構成において、表示パネル側の電極端子と回路基板側の接続配線とを低抵抗で接続可能な表示装置を提供する。

【解決手段】表示パネル3の周縁部の実装領域3bに電極端子9が引き出され、接続配線15が延設された回路基板5を実装させた表示装置1Aである。表示パネル3と回路基板5との間には、電極端子9と接続配線15とを接続すると共に、表示パネル9と回路基板5とを接着する異方性導電膜7が挟持されている。表示パネル3の実装領域3bは、開口部13Aを備えた有機保護膜13で覆われ、この開口部13Aは、有機保護膜13下の無機絶縁膜11に設けた電極端子9を露出させる接続部開口11Aと共に、接続部開口11Aよりも表示パネル3の端縁側の領域を連続して露出させる形状である。この開口部13Aの底部において、接続配線15を対向させた状態で回路基板5が実装される。

(もっと読む)

撮像素子パッケージ

【課題】導電性、半田濡れ性、ガラス密着性のうち、少なくとも2つ以上の性能を向上させた電極パターンを備えた撮像素子パッケージを提供する。

【解決手段】撮像素子パッケージ1は、撮像素子2と、半田で構成される外部接続端子3と、撮像素子2および外部接続端子3が固定されるガラス基板4とを備え、ガラス基板4には、レジネートにより構成されるとともに撮像素子2と外部接続端子3とを接続する電極パターン7が形成され、電極パターン7は、外部接続端子3と撮像素子2とを接続する導電性の良い電極層9と、この導電性の良い電極層9に固着されるとともに、外部接続端子3が設けられる位置に対応して設けられる半田濡れ性の良い電極層10とを備える。

(もっと読む)

電子回路基板の製造方法

【課題】基材にベアICチップを実装して、品質の高い電子回路基板を効率良く生産することができる電子回路基板の製造方法を提供する。

【解決手段】インレット用基材21のうちベアICチップ23が実装される位置に、第1接着剤41が、第1のディスペンサー31により、ベアICチップ23のバンプ25に達しない程度の量だけ塗布される。次に、超音波を印加することができるピックアップノズル15により、半導体ウェハー16を個別に切り出して形成された個々のベアICチップ23が、インレット用基材21に塗布された第1接着剤41上に各々載置される。その後、ピックアップノズル15がICチップ23に対して超音波を印加し、このことにより、ベアICチップ23のバンプ25とアンテナ22とが電気的に接合される。更に、インレット用基材21およびベアICチップ23に、第2接着剤42が、第2のディスペンサー32により、ベアICチップ23の上面全域および側面外周全域を覆うように塗布される。

(もっと読む)

部品実装基板の製造方法

【課題】低コストで基板にICチップなどの電子部品を実装することが可能であり、電子部品の実装時にポリマー型導電インクによって導電部の端子間が電気的に接続され、回路がショートすることを防止する部品実装基板の製造方法を提供する。

【解決手段】本発明の部品実装基板の製造方法は、基板1の一方の面1aに、ポリマー型導電インクを塗布して未乾燥の塗膜2を形成する工程Aと、この塗膜2における電極部2aの間に熱可塑性樹脂3を付着する工程Bと、電極部2aに電子部品11の端子12が対向するとともに、端子12間に熱可塑性樹脂3が配されるように、基板1の一方の面1aに電子部品11を配置する工程Cと、未乾燥の塗膜2を加熱、乾燥させて導電部を形成するとともに、熱可塑性樹脂3を溶融させて導電部の一対の電極間および電子部品の端子12間に、熱可塑性樹脂3を充填する工程Dとを有することを特徴とする。

(もっと読む)

配線基板、半導体装置の製造方法及び装置

【課題】マルチチップモジュールを効率的に製造すること。

【解決手段】マルチチップモジュール10aは、1つの配線パターン領域2a内に実装される半導体チップ3L,3R同士の間隔Bに対し、隣接する配線パターン領域2a間における半導体チップ3L,3R同士の間隔Cを等しくしていることにより、製造時において、搬送ピッチを一定の間隔(間隔B=C)に設定すれば、全ての半導体チップ3L,3Rをテープ基板1Aの一巡の搬送で実装することが可能となる。したがって、マルチチップモジュールを効率的に製造することが可能となる。

(もっと読む)

電子布地

本発明は、基板電極を有する布地基板とコンポーネント電極を有する電極コンポーネントとを含む電子布地に関する。前記コンポーネント電極は、基板電極とコンポーネント電極との間において電流が優先的に流れることを可能にするために、前記基板電極と、結合層を介して電気伝導接触にある。寄生電流の発生を防ぐために結合層がパターン化される必要がないので、基板電極及びコンポーネント電極の間の電気伝導性接触部は、改善された信頼性を有する。  (もっと読む)

(もっと読む)

COFテープ

【課題】打抜き型で打抜く領域を変更するだけで、長さの異なるチップオンフィルムや、端子数の異なるチップオンフィルムが得られるように改良したCOFテープを提供する。

【解決手段】テープ基材1に多数のICチップ2を一定間隔をあけて搭載し、各ICチップ2の前側と後側に入力端子列と出力端子列40を形成して導電パターン5で配線することにより、チップオンフィルムの構成単位Aが前後方向に連続して形成されたCOFテープにおいて、上記入力端子列を横二列の入力端子列31,32に形成する。双方の入力端子列31,32の端子数を異ならせるのがよい。打抜き領域に横二列の入力端子列30,31を含めるか、ICチップ2に近い方の入力端子列31だけを含めるかによって、長さと入力端子数の異なるチップオンフィルムを得ることができる。

(もっと読む)

半導体装置

【課題】 半田の量に誤差あるいは部品位置ずれが生じた場合でも半田の流れを防止することを実現する。

【解決手段】 薄膜基板と、この薄膜基板に形成された電子部品を接続するパッドと、このパッドに設けられ半田の流れを抑制するように形成された凸部と、前記パッドに半田付けされて配置された前記電子部品とにより形成される半導体装置において、前記パッドに接続される前記電子部品の頂点に対応する位置に設けられると共に、前記パッドの周辺部に設けられる切りかけとを具備することを特徴とする。

(もっと読む)

電子装置

【課題】導電性部材による複数の接続箇所の相互間でのショートを確実に回避する。

【解決手段】回路を内蔵しバンプ111を有する回路部品110と、バンプ111と電気的に接続される接続端122aを有するアンテナパターン122がベース121の表面に設けられた配線基板120と、回路部品110を配線基板120の表面に固定するとともに、各バンプ111と各接続端122aとを電気的に接続した導電性接着剤130と、各接続端122aからはみ出た導電性接着剤130を、各々自己の方へと誘導する貫通孔部分123および窪み部分124とを備えた。

(もっと読む)

表示装置

【課題】圧接部を含む配線経路において、コンタクト抵抗を含む配線抵抗の増大を抑制し配線経路を簡略化することができる表示装置を提供する。

【解決手段】チャージポンプ方式の電源を内蔵するドライバIC1を表示パネル5上に実装し、このドライバIC1に接続された配線のうち、ドライバ内蔵電源への接続配線3のFPC実装用パッド4の幅を他の配線2のパッド4より広くする。また、パッド4からドライバIC1までの配線経路が短くなるように、FPC実装用パッド4の端子列のうち一部の端子間隔をその他の端子間隔より広くする。FPC実装用パッド4と圧接により電気的に接続されるフレキシブル基板7側の端子6についても、同様の端子幅及び端子間隔とする。

(もっと読む)

21 - 40 / 105

[ Back to top ]