Fターム[5F044KK09]の内容

ボンディング (23,044) | フェイスダウンボンディング用配線基板 (5,003) | 配線パターン (129)

Fターム[5F044KK09]の下位に属するFターム

両面配線 (24)

Fターム[5F044KK09]に分類される特許

81 - 100 / 105

半導体パッケージ及びその製造方法

【課題】配線の高密度化及び、配線設計の自由度の向上を図り得る半導体パッケージを提供する。

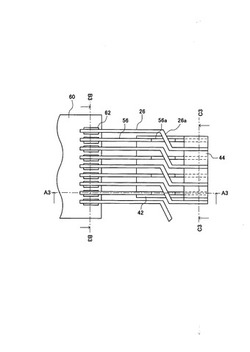

【解決手段】半導体パッケージは、第1及び第2の面を有する第1の基体と;前記第1の基体の第1の面側に設けられた第1の配線26と;第1及び第2の面を有する第2の基体42と;前記第2の基体の第1の面側に設けられた第2の配線56と;前記第1及び第2の配線に連結された半導体チップ60とを備える。そして、前記第1及び第2の基体の第1の面同士が対向するように配置し、前記第1及び第2の配線が絶縁された状態で立体的に交差させる。

(もっと読む)

電子部品及びその製造方法

【課題】

耐湿性に優れ、電極間の電気的接続及び振動部を含む封止領域への気密性を確実なものとし、さらに大型化が抑えられた電子部品を提供すること。

【解決手段】

圧電基板の一面に振動部及び第1の電極が設けられた圧電素子と第2の電極を備えた配線基板とを含む電子部品において、第1の電極及び第2の電極の一方側に設けられ、第1の電極及び第2の電極の他方側に接続されたバンプと、振動部を囲う環状の第1の金属層と、前記第1の金属層に沿って設けられ、第1の金属層と配線基板との間を封止して振動部の配置領域を気密空間とするバンプより固相線温度が低いはんだ材料と、を備えた電子部品を構成することで気密空間への透湿及びはんだ材料の外方への広がりが抑えられ、またバンプが溶融して広がるスペースを省くことができる。また電極間の電気的接続と配置領域の封止とを別工程にて行えるので高い気密性が得られる。

(もっと読む)

導電性相互接続体を用いて半導体装置を製造するための裏面処理方法及びそのシステム

導電性相互接続体(44)を有する半導体装置(50)を製造するための方法であって、半導体基板(12)回路側面(14)、裏面(16)および前記回路側面(14)上の基板接点(18)を有する半導体基板(12)を提供するステップを含む。この方法はまた前記裏面(16)から基板接点(18)への基板開口部(30)を形成するステップとそれから導電性相互接続体(44)を半導体接点(18)の内表面(32)へボンディングするステップを含む。その方法を実行するシステムは半導体基板(12)、前記半導体基板(12)の薄化システム(64)、基板開口部(30)を形成するためのエッチングシステム(66A)および前記導電性相互接続体(44)を基板接点(18)へボンディングするためのボンディング機構システム(38)からなる。半導体装置(50)はモジュール部材(98)、アンダーフィル部材(106)積層部材(216)および画像センサ半導体装置(50IS)とを形成するために使われる。 (もっと読む)

電気光学装置、電気光学装置の製造方法、実装構造体及び電子機器

【課題】

電子部品の端子に接続された基板側の端子の破損を別部材を用いずに防止することが可

能な電気光学装置、電気光学装置の製造方法、実装構造体及び該電気光学装置を備えた電

子機器を提供する。

【解決手段】

回路基板3には、開口部25a、25b、25c及び25dが、図1に示すように半導

体素子23の近傍であって、半導体素子23の角部に対応する位置に設けられているので

、例えば回路基板3のうち半導体素子23が実装されている部分に対して実装されていな

い部分を折り曲げるような力が働き回路基板3が曲がるときに、曲げによる回路基板3の

応力が例えば半導体素子23の角部の近傍の端子27a等に伝わらないように開口部25

a等により分断すると共に、開口部25a等で回路基板3を曲がり易くすることができ、

配列された端子27に力が働かないようにして、端子27の破損を防止することができる

。

(もっと読む)

フリップチップ実装基板

【課題】 チップからの信号を正確に伝送することができるフリップチップ実装基板を実現することにある。

【解決手段】 本発明は、 チップに設けられたバンプがフリップチップ実装されるフリップチップ実装基板に改良を加えたものである。本基板は、開放端が形成された配線パターンと、この配線パターンのうち絶縁膜に覆われない所定の長さの導体パターンと、この導体パターンに連続して形成され、バンプが接合される電極パターンとを有し、配線パターンは、複数並んで設けられ、電極パターンは、導体パターンの長さ方向に対して、開放端近傍に設けられることを特徴とするものである。

(もっと読む)

基板上に狭い配線部分を有するフリップチップ配線

基板上のダイのフリップチップ配線は、配線の隆起を、キャプチャパッド上にではなく、リードまたはトレースの上の狭い配線パッドの上に嵌合することによってなされる。狭い配線パッドの幅は、取り付けられるダイ上の隆起のベース直径未満である。また、フリップチップパッケージは、活性表面において配線パッドに取り付けられた半田の隆起を有しているダイと、ダイ取り付け表面において導電性トレースの上に狭い配線パッドを有している基板とを含んでおり、上記基板における隆起は、トレース上の狭いパッドに嵌合される。  (もっと読む)

(もっと読む)

基板接合構造

【課題】 セラミック基板と樹脂基板をバンプ接続する際、セラミック基板の外縁部に位置するバンプに対する熱応力の作用によって接続部にクラックが生じて、機器の長期信頼性が低くなる。

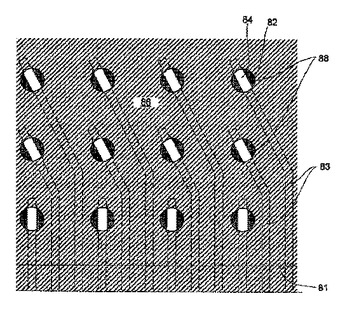

【解決手段】 複数のランドが配列されたセラミック基板と、複数のランドが配列された樹脂基板と、前記樹脂基板のランドと前記セラミック基板のランドの間に接合されボールグリッドアレイを構成する複数のバンプとを備えて、最外縁部に配列されたそれぞれの前記バンプを、隣接する前記バンプと並列に接続する。

(もっと読む)

フレキシブルプリント配線板

【課題】フレキシブルプリント配線板の製造時の応力集中に基づく、ICチップ、LSIチップ等のデバイス実装時のインナーリードの断線やソルダーレジストのクラック発生を防止することができるフレキシブルプリント配線板を提供する。

【解決手段】絶縁層11と、この絶縁層11の少なくとも一方面に積層された導体層をパターニングして形成され半導体チップが実装されると共に複数の配線が並設された配線パターン12を具備するフレキシブルプリント配線板10において、前記配線パターン12が形成されていない余白領域に、ストライプ状のダミーパターン23〜26が当該フレキシブルプリント配線板の長手方向を基準にして幅方向に略対称に形成されている。

(もっと読む)

電子装置

【課題】 環境汚染物質を含まず、装置に熱負荷が加わってもSAWチップの周波数特性がずれない高精度で且つ高信頼性な電子装置を開発すること。

【解決手段】 セラミック基板4の上面中央部に入出力電極5を形成するとともに上面外周部に全周にわたって環状金属層7を形成し、入出力電極5に電子回路素子1の下面中央部に形成した素子入出力電極2を接合材8を介してフリップチップ接合するとともに環状金属層7に電子回路素子1の下面外周部に形成した素子環状金属層3を封着材9を介して全周にわたって接合した電子装置であって、接合材8および封着材9を錫−銀合金を主成分とする半田もしくは錫−銀−銅を主成分とする半田に金、ニッケルおよびコバルトを含有させたもので構成した。

(もっと読む)

半導体装置

【課題】 小型化が可能で、かつ、信頼性の高い半導体装置を提供する。

【解決手段】 半導体装置は、ベース基板12と、第1の配線16及びその隣に配置された第2の配線18を含む複数の配線14とを有する配線基板10と、第1の配線16と接触して電気的に接続されてなり、ベース基板12と接触する先端面25を有するバンプ24を有する半導体チップ20とを含む。配線14のピッチPは、0<P<35μmである。配線14の上端面の幅Ltは、0<Lt<10μmである。バンプ24の先端面25と第2の配線18とのギャップGは2μm以上である。幅Ltと、ボンディング精度に起因する位置ずれ寸法Kと、バンプ24の幅Bとは、B>Lt+Kの関係を有する。

(もっと読む)

フリップチップ実装半導体装置の製造方法及びフリップチップ実装半導体装置

【課題】接続媒体溜りの位置をコントロールすることができるとともに配線間隔が狭い場合であっても端子間隔を十分に確保することができ、また容易により端子を形成することができるフリップチップ実装半導体装置の製造方法及びフリップチップ実装半導体装置を提供する。

【解決手段】フリップチップ実装半導体装置1は、インターポーザ基板2上に、幅が一方から他方にかけて徐々に小さい複数の端子6と、端子6の少なくとも一方の端部にそれぞれ連設された配線7とを形成する工程と、端子6上にそれぞれ半田層を形成する工程と、半田層を溶融させて、端子6上に半田溜りを形成する工程と、半導体チップ3に設けられた複数の突起状電極を、半田溜りを介して端子6にそれぞれ電気的に接続するとともに固定する工程とを含む方法により形成される。

(もっと読む)

配線基板及びこれを用いた半導体装置

【課題】半導体チップへの負担を低減させ、半導体チップの破壊を防ぐことができる配線基板及びこれを用いた半導体装置を提供する。

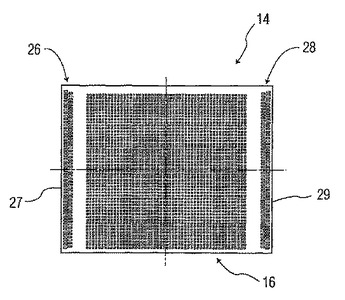

【解決手段】半導体チップのバンプに対応する位置に接続パッド14を有する配線パターン13Aを配置し、半導体チップが実装される領域12を含む接続パッド14の近傍に配線パターン13Bを配置する。

(もっと読む)

チップ・オン・フィルム回路基板及びこのチップ・オン・フィルム回路基板を用いた画像表示装置

【課題】 ドライバICを小型化してコストを削減し、かつノイズを抑え電磁妨害(EMI)対策に有利な配線パターンを有するCOF回路基板及びこのCOF回路基板を用いた液晶表示装置を提供すること。

【解決手段】 薄膜絶縁フィルム上に設けた配線パターン14にドライバIC16を実装するチップ・オン・フィルム回路基板10において、ドライバIC16の入力端子側からプリント配線板1に接続される該回路基板10の入力端子側に伸びる信号・電源・GNDラインの配線パターン14aが、その各パターン間にダミーパターンを設けることなく、かつプリント配線板1に伸びる配線パターン14aは拡幅して形成されている。前記配線パターン14aは、プリント配線板1に接続される前記回路基板10の入力端子側YからドライバIC16の入力端子側Zに向けて配線パターンに屈曲点を設けて配線され、配線パターンはその屈曲点において段階的に線幅を縮幅して、最終的にドライバIC16の入力端子幅に合致させている。

(もっと読む)

配線基板、その製造方法、及び半導体装置

【課題】絶縁信頼性と製造歩留まりとの向上を図ることが可能な配線基板を提供すること。

【解決手段】本発明の配線基板によれば、有機層上に形成された厚みtが幅Wよりも大きいリード5からなる導体パターンを備えた配線基板10である。

(もっと読む)

半導体装置、半導体装置の接続構造および半導体装置の実装方法

【課題】 接続相手の回路基板において制約の少ない配線形成を可能とし、高集積化、高信頼性化が可能な半導体装置およびこの半導体装置とこれと接続される回路基板からなる接続構造を提供する。

【解決手段】 半導体装置は半導体チップ(1)と、この半導体チップを支持し、前記半導体チップの接続電極が下面側に形成されると共に、階段状の突出部分を有する基板(2a,2b,2c,2d)とを備え、前記基板の前記階段状の突出部分は前記基板の外周に向かうにしたがって段階的に突出量が減少することを特徴とする。接続構造はこのような半導体装置と、その突出部分を収納する階段状に形成された凹部であって、その表面に前記突出部分に形成された接続電極と接続される配線パッドを有する配線基板とを備えたことを特徴とする。

(もっと読む)

超音波医療用トランスデューサアレイ

超音波トランスデューサ(40、70、100)は、個々のダイが結合された集積回路(42、72、102)と、この個々のダイが結合された集積回路にフリップチップバンプのアレイ(46、76、106)を介して結合された音響素子アレイ(44、74、104)とを有する。個々のダイが結合された集積回路は、第1の集積回路ダイ(48、78、108)と、前記第1の集積回路ダイに整列された少なくとも1つの更なる集積回路ダイ(50、80、(110、112))とを含んでいる。また、第1の集積回路ダイと、少なくとも1つの更なる集積回路ダイと、音響素子アレイとは一緒になって大口径のトランスデューサアレイを形成している。  (もっと読む)

(もっと読む)

実装基板、および表示装置

【課題】異方性導電膜を確実に実装領域に仮留めすることが可能で、これによりICチップやFPCを接続状態良好に実装することが可能な実装基板、およびこの実装基板を用いた表示装置を提供する。

【解決手段】フィルム状の異方性導電膜3を介してICチップ33が実装されるものであって、配線が設けられた支持基板2と、配線の端子11を露出させる開口部を有して支持基板2上を覆う有機絶縁膜12とを備えた表示パネル(実装基板)において、ICチップ33が実装される有機絶縁膜12側の第1搭載部7に、フィルム状の異方性導電膜31を密着させるための密着領域14が設けられている。この密着領域14は、異方性導電膜31の配置部である第1搭載部7の端部に設けられ、有機絶縁膜12よりも異方性導電膜31との密着性が良好な材料パターンとして金属パターン15が設けられている。

(もっと読む)

配線構造および電子機器

【課題】配線パターンの形状が変化する場合の特性インピーダンス不整合を抑制すること。

【解決手段】本発明は、絶縁基板1の表面に形成される配線パターン11(第1の配線パターン)と、配線パターン11の幅が変化する部分に対応して絶縁基板1の内部に形成され、配線パターン11と電気的に並列接続される補助配線パターン12(第2の配線パターン)とを備える配線構造である。また、この配線構造の配線パターン11と導通する電極ランド10に電子部品を接続してなる電子機器である。

(もっと読む)

駆動装置及び表示装置

【課題】

チップを搭載する基板上の配線領域を縮減可能とし、全体のコストを低減する装置の提供。

【解決手段】

基板10と、基板10上に設けられる複数の信号出力端子電極12と、基板上に設けられる複数の信号入力端子電極13と、信号入力端子電極13に入力端子が接続され、信号出力端子電極12に出力端子が接続される表示用駆動IC20を有し、信号入力端子電極13側に対向する表示用駆動IC20の第1の辺に複数の出力端子(1、3、5、…i+1、n−1)を有し、第1の辺と反対側の第2の辺は信号入力端子電極13に対向し、第2の辺の少なくとも1部の区間に入力端子22を有し、第2の辺の残りの区間の少なくとも1部に出力端子(2、4、6、i、j、j+2、n−2、n)を有し、第2の辺の一の出力端子は、半導体チップ20下面を通る配線15により、該一の出力端子に対応する前記第1の辺の2つの出力端子の間を通過して対応する信号出力端子電極12に接続される。

(もっと読む)

電子部品モジュールおよびその製造方法

【課題】半田などの熱融解型接続部材を使用することなく、貫通スルーホールによる層間接続も同時に達成できる信頼性の高い電極接続を達成できる電子部品モジュールおよびその製造方法を提供すること。

【解決手段】電子部品モジュールは、複数の貫通孔が穿設された絶縁基板と、接続電極を前記貫通孔に挿入又は当接させて前記絶縁基板の一主面に固定された表面実装用電子部品と、前記絶縁基板の他主面に、その一部が前記表面実装用電子部品の接続電極と電気的に接触するよう形成された金属微粒子による回路パターンと、前記金属微粒子による回路パターン上に形成された金属めっき層とを有することを特徴とする。

(もっと読む)

81 - 100 / 105

[ Back to top ]