Fターム[5F044KK09]の内容

ボンディング (23,044) | フェイスダウンボンディング用配線基板 (5,003) | 配線パターン (129)

Fターム[5F044KK09]の下位に属するFターム

両面配線 (24)

Fターム[5F044KK09]に分類される特許

1 - 20 / 105

配線基板及びその製造方法、半導体パッケージ

半導体装置

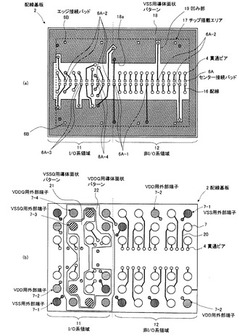

【課題】半導体装置のI/O系および非I/O系の電源およびGNDをバランス良く強化して、低電圧動作性能および高速動作性能を向上させること。

【解決手段】配線基板2の一面は、接続パッド6Aの列を取り囲むように形成され、かつVSS用接続パッド6A−1と配線16を介して接続されたVSS用面状導体パターン18を備える。配線基板2の他面は、複数のVSSQ用外部端子7−3を連結するように配置されたVSSQ用面状導体パターン21と、複数のVDDQ用外部端子7−4を連結するように配置されたVDDQ用面状導体パターン22とを備える。

(もっと読む)

電子装置、配線基板、及び、電子装置の製造方法

【課題】フリップチップ接続されて構成される半導体装置などのように、はんだを用いた電極どうしの電気的接続が行われる電子装置においても、チップなどの電子部品の回路、又は、配線基板の回路を変更する以外の手法で、電子部品の電極の接続先を切り替える。

【解決手段】電子装置(例えば、半導体装置100)は、複数の第1電極210を一方の面上に有する配線基板200と、複数の第1電極210とそれぞれ対応して配置された複数の第2電極310を一方の面上に有する電子部品(例えば、チップ300)を有する。第1電極210のうちの少なくとも1つ以上は、複数の分割部分221、222に分割された特定電極220であり、分割部分221、222が、各々異なる配線251、252に接続されている。分割部分221、222のうちの何れか1つ以上が、対応する第2電極310とはんだ110を介して接続されている。

(もっと読む)

半導体装置

【課題】フリップチップ実装の半導体装置において、パッケージ外部の設計を変更せずに、特定の端子の電位を変更できる半導体装置を提供する。

【解決手段】本発明の半導体装置は、外部端子にバンプを備えるICチップと、前記ICチップを搭載するパッケージとを備え、前記パッケージは、前記外部端子に第1の信号又は第2の信号を印加するインナーリード部を備える。前記インナーリード部は、前記ICチップの搭載位置により、前記外部端子に印加する信号を、前記第1の信号又は前記第2の信号に変更可能なインナーリードのパターンを有する。

(もっと読む)

圧電装置

【課題】

本発明は、集積回路素子の電極パッドと、半田バンプとの接合強度の低下を防ぐ圧電装置を提供することを課題とする。

【解決手段】

本発明の圧電装置100は、素子搭載部材110と、素子搭載部材110に搭載されている圧電素子120と、素子搭載部材110の表面に形成されており、素子搭載領域118aおよび引き回し領域118bを含んでいる金属パターン118と、半田バンプ132によって金属パターン118の素子搭載領域118aに電気的に接続されている集積回路素子130とを備え、金属パターン118が素子搭載領域118aと引き回し領域118bとの間に設けられた凸部119を有しており、凸部119の少なくとも表面部分が金属酸化物から成る。

(もっと読む)

フリップチップ構造の実装基板、製造方法、及び、半導体装置

【課題】 フリップチップ接合により半導体発光素子を搭載する場合に、半導体発光素子を精度よく位置決めして実装できる実装基板を提供する。

【解決手段】 半導体発光素子20をフリップチップ接合により実装可能な実装基板1であって、第1方向に延伸するように形成された第1パターンと、第1パターンと同じ材料で形成された第1位置合わせパターンM1と、はんだ濡れ止め用のレジスト材料を用い、第1方向とは異なる第2方向に延伸するように形成された第2パターンPR1と、第2パターンPR1と同じレジスト材料で形成された第2位置合わせパターンM2と、を備え、第1パターンにより第2方向の境界が、第2パターンPR1により第1方向の境界が夫々規定される矩形領域にバンプ形成領域Rが設定されている。

(もっと読む)

基板、プリント回路板及びそれらの製造方法

【課題】電機製品のさらなる小型化に伴う電子部品搭載密度の高度化要求に対応するため、マザーボード用基板等の安価な基板上に半導体チップなどの電子部品を搭載することが可能であり、かつ接続信頼性に優れる、基板を提供する。

【解決手段】基板表1面に部分的にシリコーン重合体含有樹脂2を備える基板であり、シリコーン重合体含有樹脂を形成する樹脂組成物の硬化後の熱膨張係数が50×10-6/℃以下である基板であって、シリコーン重合体含有樹脂を形成する樹脂組成物はシリコーン重合体及び無機充填剤を含み、シリコーン重合体100重量部に対して無機充填剤を100〜2000重量部含有している基板。

(もっと読む)

プリント配線基板

【課題】配線の断面形状を安定化して、接続信頼性を向上させる。

【解決手段】絶縁性フィルムと、前記絶縁性フィルム上に形成されるインナーリード部およびアウターリード部を含む配線と、を備えるプリント配線基板において、前記配線は、前記絶縁性フィルム上の銅箔層をエッチングして形成されるエッチング形成配線部と、前記絶縁性フィルム上に、金属ナノ粒子を主成分とする導電性インクを直接描画することにより形成される直接描画形成配線部と、から構成され、少なくとも前記インナーリード部が前記直接描画形成配線部であることを特徴とする。

(もっと読む)

導電性接着剤、及びそれを用いた回路基板、電子部品モジュール

【課題】従来の導電性接着剤では、0.8mmより更に細かいファインピッチのランドを有する電子回路基板への印刷が出来なかったという課題。

【解決手段】本発明の導電性接着剤は、10〜90wt%のSnBi系はんだ粉末と、残部が有機酸を含有する接着剤とを含む導電性接着剤であって、SnBi系はんだ粉末は、粒子径L1が20〜30μmのはんだ粒子A〜Dと、粒子径L2が8〜12μmのはんだ粒子Eから構成されており、SnBi系はんだ粉末の混合割合は、粒子径が20〜30μmのはんだ粒子A〜Dがはんだ粉末全体の40〜90wt%で、残部が8〜12μmのはんだ粒子Eである。

(もっと読む)

配線基板及びその製造方法と半導体装置

【課題】接続パッド上にはんだが設けられるフリップチップ実装用の配線基板において、接続パッドのピッチを狭小化できる配線基板を提供する。

【解決手段】複数の接続パッド22と接続パッド22にそれぞれ繋がる引き出し配線部24とが表層側の絶縁層30に配置された構造を含み、引き出し配線部24は接続パッド22から屈曲して配置され、接続パッド22上に突出するはんだ層42が設けられており、接続パッド22は長方形状を有し、引き出し配線部24は接続パッド22の長手方向の端部全体から屈曲して引き出されており、接続パッド22と引き出し配線部24とが表層側の絶縁層30から露出して設けられている。引き出し配線部24上のはんだが屈曲部B側に移動して接続パッド22上に突出するはんだ層42が形成される。

(もっと読む)

基板上に狭い配線部分を有するフリップチップ配線

【課題】フリップチップ配線を提供すること。

【解決手段】基板上のダイのフリップチップ配線は、配線の隆起を、キャプチャパッド上にではなく、リードまたはトレースの上の狭い配線パッドの上に嵌合することによってなされる。狭い配線パッドの幅は、取り付けられるダイ上の隆起のベース直径未満である。また、フリップチップパッケージは、活性表面において配線パッドに取り付けられた半田の隆起を有しているダイと、ダイ取り付け表面において導電性トレースの上に狭い配線パッドを有している基板とを含んでおり、上記基板における隆起は、トレース上の狭いパッドに嵌合される。

(もっと読む)

半導体装置

【課題】半導体パッケージの実装抵抗を低減する。

【解決手段】第1の金属部材(リード端子5,6)が、第1の貴金属を含む第1の金属体(Auバンプ8)を介して、半導体素子(半導体チップ1)の第1の電極(ソース電極2)と接続され、かつ、第2の金属部材(ダイ端子7)が、第2の貴金属を含む第2の金属体(貴金属メッキ14及びAgメッキ15)を介して、第2の電極(裏面電極4)と接続される。裏面電極に接続される金属部材を有し、配線基板との半導体装置の実装面が回路形成面側であり、金属部材が折り曲げ加工されている。

(もっと読む)

半導体パッケージ、配線基板、及びリフロー炉

【課題】複数の金属ボール端子を備えた半導体パッケージをリフロー法により配線基板に実装する際に、金属ボール端子の溶融状態を正確に把握する。

【解決手段】複数の金属ボール端子のうち四隅の金属ボール端子15A〜15Dはその他の金属ボール端子14よりも相対的に径が小さい導通検出用の金属ボール端子であり、導通検出用の金属ボール端子15A〜15Dの径が式(X)を充足し、互いに対角にある2個の導通検出用の金属ボール端子15Aと15C、15Bと15Dが配線16を介して接続されている。

d2≧d1−x・・・(X)

(上記式中、d1は導通検出用ではない金属ボール端子の径、d2は導通検出用の金属ボール端子の径、xは配線基板上に半導体パッケージを載置した時点に対する金属ボール端子の溶融後の半導体パッケージの沈み込み量を各々示す。)

(もっと読む)

布製半導体素子のパッケージ及びその製造方法

【課題】着用した際の異物感を最小限に抑えると共に、生産性が向上した布製半導体素子のパッケージ、その布製半導体素子のパッケージの製造方法を提供する。

【解決手段】布製半導体素子のパッケージは、織布と、前記織布上に導電材をパターニングして形成された第1リード部と、を有する布製印刷回路基板と、前記布製印刷回路基板のリード部に接続された電極部を有する半導体素子と、前記布製印刷回路基板と、前記半導体素子とを密封する成形部(molding)と、を含む。前記第1リード部は、前記第1リード部の端部において別の布製半導体素子と電気的に接続された導電性繊維によって前記織布とともに縫合されることにより、あるいは、前記第1リード部は、前記第1リード部の端部において別の布製半導体素子と電気的に接続された布製印刷回路基板の第2リード部と前記織布と共に縫合されることにより、前記別の布製半導体素子と電気的に接続されている。

(もっと読む)

半導体装置

【課題】半導体素子と配線基板との間にボイドが発生するのを効果的に防ぎ、フリップチップ実装の信頼性を高める半導体装置を提供する。

【解決手段】配線基板1における半導体素子2の側端部2eの近傍に、アンダーフィル3の塗布位置8がある。配線基板1には、アンダーフィル3が塗布される塗布位置8の近傍であって、半導体素子2のコーナー部2a,2bに対向する位置に、アンダーフィル3の充填の際にアンダーフィル3の進行を減速させる凹部4a,4bが形成されている。

(もっと読む)

基板、基板の製造方法、及び、半導体装置

【課題】半導体装置の信頼性を向上させる。

【解決手段】基板100は、基材11に、複数の電極12と、ベタ導体101とを形成することで構成されている。ベタ導体101は、半導体チップを装着するのにACF(Anisotropic Conductive Film)が貼り付けられる基材11のACF領域よりも所定のサイズだけ大きい領域である大サイズ領域のうちの、電極12が形成される基材11の電極領域とその周囲を除く領域の全体を被覆するように、基材11に形成される。本発明は、例えば、フリップチップ実装により、半導体装置を製造する場合等に適用できる。

(もっと読む)

電子部品、半導体装置、及び半導体装置の製造方法

【課題】半導体基板の側面を基点としたクラックが半導体装置の多層配線層に伝播することを抑制する。

【解決手段】半導体装置100は実装基板10上に、バンプ130を用いてフリップチップ実装されている。アンダーフィル樹脂層200は、半導体装置100の能動面と実装基板10の間の空間を封止している。また半導体装置100の多層配線層120は半導体基板110の能動面側の面に形成されており、かつ半導体基板110の縁に位置する部分122が全周にわたって除去されている。多層配線層120のうち除去されている部分122の幅をwとして、半導体基板110の厚さをhとしたときに、w>hである。

(もっと読む)

半導体装置とその製造方法

【課題】フリップチップ実装の際のアンダーフィル樹脂の流れ拡がりの問題を解決する。

【解決手段】半導体装置は、基板と、前記基板の主面上にフリップチップ状態で搭載された半導体素子と、前記基板の主面に於いて、前記半導体素子の少なくとも一つの縁部に沿って配設された第1の導電パタ―ンと、前記基板の主面上に於いて、前記第1の導電パタ―ンから離間し、かつ前記第1の導電パタ―ンに沿って配設された第2の導電パタ―ンと、前記基板の主面上に於いて、前記第1の導電パタ―ンと第2の導電パタ―ンとの間に橋絡状態をもって配置された受動素子と、前記基板と前記半導体素子との間に充填された樹脂とを有し、前記樹脂は、前記基板の主面に於いて、前記半導体素子と前記第1の導電パタ―ンと間に延在する。

(もっと読む)

半導体装置とその製造方法

【課題】半導体装置とその製造方法において、半導体部品と回路基板との位置合わせを容易にすること。

【解決手段】表面に複数の第1の電極22が形成された第1の回路基材20と、第1の回路基材20の上方に設けられ、第1の電極22の各々の上方に第1の貫通孔30aと第2の貫通孔30bとが形成された第2の回路基材30と、第2の回路基材30の上方に設けられた半導体パッケージ50と、第1の貫通孔30aと第2の貫通孔30b内に設けられ、第1の電極22と半導体パッケージ50とを接続する複数の第1のバンプ51とを有する半導体装置による。

(もっと読む)

実装マウント装置

【課題】 ランド状接続端子とバネ状接触子を電気的に接触させた接触面に低周波振動を印加することによって金属間接合部を生成される実装マウント装置を提供する。

【解決手段】 バネ状接触子2を有するインターコネクタ3を備えた実装基板4に、ランド状接続端子5を備えた電子部品6を接合させる実装マウント装置1であって、ランド状接続端子5は、バネ状接触子2との接触面にSn―Agメッキ7が施され、ランド状接続端子5とバネ状接触子2とを少なくとも一対設け、低周波振動アクチュエータ8を備えた加振台9と、この加振台9の下面に設けられたゴム板14と、を備え、ランド状接続端子5とバネ状接触子2とを対面させて重ね合わせ、低周波振動アクチュエータ8を電気的に駆動させて振動させることによって接触面に金属間接合部10が生成される。

(もっと読む)

1 - 20 / 105

[ Back to top ]