Fターム[5F044KK13]の内容

ボンディング (23,044) | フェイスダウンボンディング用配線基板 (5,003) | 電極部 (1,724) | 金属多層 (179)

Fターム[5F044KK13]の下位に属するFターム

ハンダコーティング (67)

Fターム[5F044KK13]に分類される特許

1 - 20 / 112

はんだ接続用通電部材、配線用基板及びめっき皮膜の形成方法

【課題】CuまたはCu合金からなる通電部材(電極端子)に、Cu成分を含有しないはんだを使用しても、通電部材側とはんだとが十分な接合強度を発現するはんだ接続用通電部材、配線用基板及びめっき皮膜の形成方法を提供する。

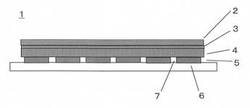

【解決手段】CuあるいはCu合金を含む通電部材1上に、ピンホール7を有する置換Snめっき皮膜5と、電解Niめっき皮膜4と、電解Pdめっき皮膜3と、電解Auめっき皮膜2と、がこの順に積層されているはんだ接続用通電部材である。

(もっと読む)

半導体パッケージの製造方法

【課題】接続信頼性が高く、コストに優れた、狭ピッチ化にも対応可能な接続端子を有する半導体パッケージの製造方法を提供する。

【解決手段】半導体素子をフリップチップ実装する配線基板の最上層の導体回路上に、複数の金属ポスト形成用のソルダーレジスト開口を有するソルダーレジスト層を設け、シード層(無電解金属めっき)を形成し、ソルダーレジスト開口と対応する位置にレジスト開口が形成されたドライフィルムレジスト層を形成し、電解金属めっきで金属ポストを形成した後、前記開口内に前記ドライフィルムレジスト層の表面と同等の高さまではんだペーストを充填する工程を含む。はんだを形成する手法として採用されていた電解めっき工法に替わり、はんだペーストの充填(印刷)手法を採用する。

(もっと読む)

半導体チップパッケージ及びその製造方法

【課題】本発明は、半導体チップパッケージ及びその製造方法に関する。

【解決手段】本発明の実施形態によると、(a)IC基板上に形成されたバンプパッド上にスズ系金属メッキ層を形成する段階と、(b)ベアチップの電極パッド上にCuフィラーを形成する段階と、(c)ベアチップのCuフィラーをIC基板の金属メッキ層に載置し、Cuフィラーと金属メッキ層とを接合させる段階と、(d)接合されたIC基板とベアチップとの間を絶縁体で充填する段階と、を含むスズメッキを利用した半導体チップパッケージの製造方法が提案される。また、その方法により製造された半導体チップパッケージが提案される。

(もっと読む)

配線基板およびはんだバンプ付き配線基板ならびに半導体装置

【課題】 エレクトロマイグレーションによる接続パッドの空隙を抑制することが可能な配線基板を提供すること。

【解決手段】 上面に半導体素子4の搭載部1aを有する絶縁基板1と、ガラス成分を含む銅の多結晶体からなり、搭載部1aから絶縁基板1の内部にかけて形成された貫通導体3と、貫通導体3を形成している銅の結晶よりも平均粒径が大きい銅の多結晶体からなり、搭載部1aにおける貫通導体3の端面を覆うように形成された接続層2とを備えており、接続層2を形成している銅の結晶配向性が無配向であり、半導体素子4の電極5が接続層2にはんだ6を介して電気的に接続される配線基板である。

(もっと読む)

接着剤組成物及びこれを用いた回路接続材料、並びに、回路部材の接続方法及び回路接続体

【課題】200℃程度の高温条件で回路部材同士の接続を行った場合でも、回路部材の反りを十分に抑制できる接着剤組成物及びこれを用いた回路接続材料を提供すること。

【解決手段】本発明の接着剤組成物は、回路部材同士を接着するとともにそれぞれの回路部材が有する回路電極同士を電気的に接続するために用いられるものであって、エポキシ樹脂、エポキシ樹脂硬化剤、及び、架橋反応性基を有し且つ重量平均分子量が30000〜80000であるアクリル系共重合体を含有する。当該接着剤組成物を温度200℃で1時間加熱して得られる硬化物は、−50℃における貯蔵弾性率が2.0〜3.0GPaであり且つ100℃における貯蔵弾性率が1.0〜2.0GPaであるとともに、−50〜100℃の範囲における貯蔵弾性率の最大値と最小値との差が2.0GPa以下である。

(もっと読む)

半導体装置

【課題】半導体チップに形成するはんだバンプの形成方法を限定することなく、はんだバンプによる複数の接続部の面積をいずれも同程度に保ったままで、接続信頼性が高い実装を可能とする半導体装置を得られるようにする。

【解決手段】半導体装置は、少なくとも1つの素子が形成された素子形成面と該素子形成面に形成された複数の電極パッド2とを有する半導体チップ1と、主面が半導体チップ1の素子形成面と対向し、且つそれぞれが主面の各電極パッド2と対向する位置に形成された複数の接続パッド15を有する配線基板10と、各電極パッド2と各接続パッド15との間にそれぞれ設けられ、それらを電気的に接続する複数のはんだバンプ4とを備えている。各はんだバンプ4における、電極パッド2側の組成と接続パッド15側の組成とは同一である。

(もっと読む)

半導体装置

【課題】50ミクロンピッチ以下の微細ピッチ電極を有する半導体素子を基板上のパッドもしくは配線を接続する構造において、接続時の加熱または荷重負荷時に発生するバンプ間ショートや、高歪みによる接続部破断を防止しあるいは接触抵抗を低減し、高信頼性で高速伝送に対応可能な半導体装置を提供する。

【解決手段】基板20と半導体素子1は縦弾性係数(ヤング率)が65GPa以上600GPa以下のバンプ11と、錫、アルミニウム、インジウム、あるいは鉛のいづれかを主成分とする緩衝層12を介して接続されており、バンプ11と基板20上のパッドもしくは配線21の対向した面の少なくとも一方に突起が形成され、超音波により接続することにより低温接続が可能な半導体装置。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】接続信頼性の高い半導体装置を提供する。

【解決手段】半導体チップ5は、第1金属により形成されたバンプ電極51を有する。また、回路基板1は、第2金属と第3金属とにより形成された金属層27を有する。この回路基板1は、半導体チップ5のバンプ電極51が形成された面と対向するように、半導体チップ5と接合している。バンプ電極51と金属層27とが接合する接合部300は、第1金属を含む第1領域320と、第1金属を含む海部と、第2金属を含む島部と、を有する海島構造からなる第2領域340と、を備えている。

(もっと読む)

電子部材ならびに電子部品とその製造方法

【課題】本発明は、接合材料を微細ピッチで供給し電気的な接続が可能な電子部材を提供することを目的とする。

【解決手段】回路基板に設けられた一つ以上の接続端子に対して、電子部材に設けられた一つ以上の電極が接合層を介して電気的に接合され、前記接合層は焼結銀を主体として構成され、前記接合層と接していない電極表面の全面あるいは一部が酸化銀の粗化層であり、当該酸化銀の粗化層の厚さは400nm以上5μm以下であり、前記酸化銀の層の最表面は1μmより小さい曲率半径となっていることを特徴とする電子部品。

(もっと読む)

配線基板およびその製造方法

【課題】半導体素子接続パッドを形成する配線導体とソルダーレジスト層との間に半田が滲入して潜り込むことを有効に防止し、半導体素子の電極端子と半導体素子接続パッドとを接合する半田が不足することがなく両者を良好に接続することが可能であるとともに、ソルダーレジスト層が剥がれることがなく配線導体の絶縁信頼性に優れる配線基板を提供すること。

【解決手段】絶縁基板1と、絶縁基板1の上面に形成された銅から成る配線導体3と、絶縁基板1および配線導体3上に被着されており、配線導体3の一部を半導体素子接続パッド4として露出させる開口部6aを有するソルダーレジスト層6と、半導体素子接続パッド4の上面に被着された錫めっき層7とを備えた配線基板10であって、配線導体3における半導体素子接続パッド4とソルダーレジスト層6との間に配線導体3が銅のままで露出する銅露出部8が形成されている。

(もっと読む)

インターポーザ基板、インターポーザ基板の製造方法、及び電子装置

【課題】電子部品及びインターポーザ基板の隙間を狭小化しても、電子部品及びインターポーザ基板の隙間を充分に確保することが出来るインターポーザ基板を提供すること。

【解決手段】基板本体11と、前記基板本体11の表面に設けられ、電子部品30の突起端子32を接続するための電極パッド15を有する配線パターン12と、前記配線パターン12の前記電極パッド15の周囲に選択的に形成され、前記電極パッド15より半田の濡れ性が低い金属膜13と、を備えるインターポーザ基板。

(もっと読む)

半導体装置の製造方法

【課題】配線を設計通りの形状に形成することができる半導体装置の製造方法を提供する。

【解決手段】本発明に係る半導体装置の製造方法は、半導体基板と、前記半導体基板の第1の面に位置する電極と、前記第1の面に設けられ、前記電極とオーバーラップする位置に開口部を有する絶縁膜と、を有する構造体を用意する工程と、前記絶縁膜の前記第1の面側の面とは反対側の第2の面に、樹脂突起を形成する工程と、前記電極および前記樹脂突起を覆う第1導電膜を前記第2の面に形成する工程と、前記第1導電膜の前記第2の面側の面とは反対側の第3の面に、前記第1導電膜の前記第3の面より反射率の低い第2導電膜を形成する工程と、前記第2導電膜の前記第3の面側の面とは反対側の第4の面に、フォトレジスト層を形成する工程と、前記フォトレジスト層の一部をマスク層で覆った状態で、前記フォトレジスト層を露光する工程と、前記フォトレジスト層を現像し、フォトレジストパターンを形成する工程と、前記フォトレジストパターンをマスクとして前記第1導電膜および前記第2導電膜をエッチングすることにより、前記第1導電膜から形成された配線であって、前記樹脂突起の少なくとも一部を覆い、かつ、前記電極と接続する前記配線を形成する工程と、を有する。

(もっと読む)

回路基板、半導体部品、半導体装置、回路基板の製造方法、半導体部品の製造方法及び半導体装置の製造方法

【課題】容易に電極部間のピッチを狭めたり、容易に電極部上に微小な半田バンプ形成したりすることができる回路基板等の技術を提供すること。

【解決手段】回路基板10は、電極部21を有する配線部20を備える。電極部は、銅層22と、銅層上の酸化銅層23と、酸化銅層を貫通する孔24とを有する。孔により露出された銅層露出部25上には、フリップチップ実装用の半田バンプ1が形成される。半田バンプ形成時には、電極部上にクリーム半田等が塗布されて加熱される。半田は、銅には接着し易いが、酸化銅には接着にくい性質を有しており、この関係が利用される。つまり、クリーム半田加熱時には、半田バンプは、接着し易い銅層露出部上に形成され、酸化銅層上には形成されない。これにより、孔の大きさを調整することで、容易に微小な半田バンプを形成することができ、また、電極部の構造を複雑化する必要もないので、容易にピッチを狭めることができる。

(もっと読む)

配線基板およびはんだバンプ付き配線基板ならびに半導体装置

【課題】 絶縁基板に配置された接続パッドに半導体素子の電極がはんだバンプを介して接合される配線基板において、接続パッドおよび電極のエレクトロマイグレーションによる空隙が抑制された配線基板を提供する。

【解決手段】 電子部品素子の搭載部1aを有する絶縁基板1と、搭載部1aから絶縁基板1の内部にかけて形成された貫通導体3と、銅または銅を主成分とする合金からなり、絶縁基板1の上面から貫通導体3の端部にかけて被着された、半導体素子4の電極5がはんだ6を介して接合される接続パッド2とを備え、平面視で貫通導体3の端部に被着された領域において、接続パッド2の上面にニッケルまたはニッケルを主成分とする合金からなる金属層8が被着されている配線基板である。金属層8によって接続パッド2のマイグレーションを抑制し、はんだ6に接合された接続パッド2の銅成分によって接続パッド2のマイグレーションを抑制できる。

(もっと読む)

実装構造体およびその製造方法

【課題】本発明は、電気的信頼性を向上させる要求に応える実装構造体およびその製造方法を提供するものである。

【解決手段】電子部品2の電極パッド6は、銅または金を含む第1下地層7aと、該第1下地層7aおよび導体バンプ4に接続された、ニッケルを含む第1介在層8aとを具備し、配線基板3の接続パッド11は、銅または金を含む第2下地層7bと、該第2下地層7bおよび導体バンプ4に接続された、ニッケルを含む第2介在層8bとを具備し、電極パッド6および接続パッド11に接続された、スズ、インジウムまたはビスマスを含む導体バンプ4は、第1介在層8aの前記ニッケルが拡散してなる第1拡散層領域18aと、第2介在層8bの前記ニッケルが拡散してなる第2拡散層領域18bとを具備し、第1拡散層領域18aは、第2拡散層領域18bよりも厚みが小さい。

(もっと読む)

バンプオンリード相互接続を形成する半導体素子および方法

【課題】半導体素子を作製する方法を提供する。

【解決手段】半導体ダイの表面上に形成された複数の複合バンプを有する、半導体ダイを提供するステップであって、前記複合バンプは、可融性部分および非可融性部分を有する、ステップと、基板を提供するステップと、エスケープルーティング密度を増加させるための平面図から、伝導性トレースと平行な縁を有する相互接続部位を伴って前記基板上に複数の伝導性トレースを形成するステップであって、前記複合バンプは、前記相互接続部位よりも幅広い、ステップと、前記可融性部分が前記相互接続部位の頂面および側面を覆うように、前記複合バンプの前記可融性部分を前記相互接続部位に接着するステップと、前記半導体ダイと基板との間で前記複合バンプの周囲に封入材を堆積させるステップとを含む、半導体素子を作製する方法。

(もっと読む)

電子部品装置及びその製造方法と配線基板

【課題】電子部品を配線基板から離した状態で実装する電子部品装置において、信頼性を向上させること。

【解決手段】基板10xと、基板10xの上に立設する金属材料からなる電極ポスト30と、電極ポスト30に接続電極42が接合された電子部品40とを含み、電極ポスト30と電子部品40の接続電極42とは電極ポスト30の金属材料と異なる金属を含む合金層31(金・インジウム合金層など)によって接合されている。

(もっと読む)

半導体装置、回路配線基板及び半導体装置の製造方法

【課題】信頼性の高い半導体装置を作製する。

【解決手段】回路配線基板20と半導体パッケージ10とを実装させた半導体装置1において、回路配線基板20の表面にパターニングされた電極21と、半導体パッケージ10に電極端子としてアレイ状に形成された半田11とが中間層30を介して電気的に接続されていることを特徴とする。中間層30は、加熱処理によって電極21の上に成長させた層であり、半田11の主たる成分及び電極21の主たる成分を共に含有している。これにより、半田11にかかる応力が緩和され、オープン不良が抑止された、信頼性の高い半導体装置1の実現が可能になる。

(もっと読む)

Bi系はんだ接合用の電子部品と基板及び電子部品実装基板

【課題】 Pbを含まないBi系はんだ合金により電子部品と基板を接合する際に、電子部品又は基板の最上層であるNi含有層のNiとBi系はんだ合金のBiとの反応を抑制し、確実な接合が可能な電子部品及び基板を提供する。

【解決の手段】 Pbを含まずBiを80質量%以上含有するBi系はんだ合金を用いて接合する電子部品又は基板において、その電子部品又は基板の最上層であるNi含有層の上に、厚さ0.05〜8.00μmのZnメタライズ層若しくは厚さ0.05〜3.00μmのSnメタライズ層を形成する。好ましくは、Znメタライズ層若しくはSnメタライズ層の上に、Ag、Au、Cuから選ばれる厚さ0.05〜1.00μmの第2のメタライズ層を成形する。

(もっと読む)

半導体装置の製造方法

【課題】半田接続部に生じる熱応力の緩和効果を維持しつつ、半田接続部の耐疲労性を向上させることを可能にした半導体装置の製造方法を提供する。

【解決手段】実施形態においては、配線基板2の接続パッド4上にSn合金からなる予備半田層10を形成する。半導体チップ2の電極パッド5上にSn合金からなる半田バンプ13を形成する。予備半田層10と半田バンプ13とを位置合せしつつ接触させた後、予備半田層10及び半田バンプ13の融点以上の温度に加熱して溶融させ、Ag及びCuを含むSn合金からなる半田接続部6を形成する。予備半田層10と半田バンプ13のうち、予備半田層10のみをAgを含むSn合金で形成する。

(もっと読む)

1 - 20 / 112

[ Back to top ]