Fターム[5F044LL00]の内容

ボンディング (23,044) | フェイスダウンボンディング (4,630)

Fターム[5F044LL00]の下位に属するFターム

直接ハンダ付け状態 (1,160)

ハンダ付け方法 (478)

導電ペースト、接着剤によるもの (335)

異方性導電材料によるもの (820)

絶縁材料でチップと配線を密着させるもの (1,009)

介在物を介して接続 (286)

接触によるもの (125)

基板とチップ間のスペーサー (91)

ハンダパッキング (4)

Fターム[5F044LL00]に分類される特許

21 - 40 / 322

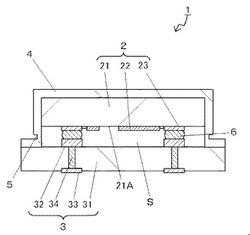

電子装置

【課題】 チップ部品および配線基板の接続不良を抑制することが可能な電子装置を提供すること。

【解決手段】 電子素子22および電子素子22が第1主面21Aに搭載された基板21を有するチップ部品2と、チップ部品2が第1主面21Aを対向させた状態で搭載される配線基板3と、チップ部品2の表面から配線基板3の表面にかけて設けられ、電子素子22を封止する封止空間Sを取り囲む樹脂層4とを備え、樹脂層4は、封止空間Sの側方に位置する部位に、外表面に開口する窪み部5を有している電子装置1である。封止空間Sの側方の樹脂層4は体積が減少するので、チップ部品および配線基板の接合部にかかる繰り返し応力が抑制され、この接合部の接続不良を抑制できる。

(もっと読む)

フリップチップ実装構造およびその製造方法

【課題】低コストな手段で放熱性の高い、小型・薄型のフリップチップ実装構造およびその製造方法を提供する。

【解決手段】半導体素子と配線基板とがバンプを介して接合されたフリップチップ実装構造において、前記配線基板の前記半導体素子と対向する面にランドが設けられ、前記ランド上には金属部材が設けられ、前記金属部材は前記半導体素子の表面の一部と接触している。またその製造方法において、前記配線基板を前記金属部材の融点以上まで加熱し、前記ランド上に設けられた前記金属部材が溶融した状態で前記半導体素子と前記配線基板とを前記バンプを介して接合する。

(もっと読む)

半導体装置及びその製造方法

【課題】 半導体素子間の接続不良の発生を低減可能な半導体装置を提供する。

【解決手段】 下部構造体110cと第1半導体素子110aとを連結する第1連結構造体140aは、複数の連結部141および複数の補助部142を有する。また、第1半導体素子110aと第2半導体素子110bとを連結する第2連結構造体140bは、複数の連結部141を有する。第1連結構造体140aの連結部141および補助部142の数に比べて、第2連結構造体140bの連結部141の数は小さい。これにより、第1半導体素子110aを下部構造体110cに連結するときのボンディング力に比べて、小さいボンディング力で第2半導体素子110bを第1半導体素子110aに連結することができる。したがって、第1連結構造体140aが変形または変性することなく、半導体素子間の接続不良の発生を低減することができる。

(もっと読む)

半導体装置の製造方法

【課題】半導体チップの組立工程におけるハンドリング性を向上し、しかも、半導体チップの損傷を回避する半導体装置の製造方法を提供すること。

【解決手段】ダイシングライン16によって区画された複数の半導体チップ4を含む半導体ウエハ2を準備する第1の工程と、半導体ウエハ2に支持板13を付着する第2の工程と、半導体ウエハ2および支持板13をダイシングライン16に沿って切断し、半導体チップ4および分割された支持板13からなる積層体3を形成する第3の工程と、積層体3を配線基板18に搭載し、積層体3の半導体チップ4および配線基板18を電気的に接続する第4の工程とを有する半導体装置1の製造方法。

(もっと読む)

電子部品装置及びその製造方法と配線基板

【課題】電子部品を配線基板から離した状態で実装する電子部品装置において、信頼性を向上させること。

【解決手段】基板10xと、基板10xの上に立設する金属材料からなる電極ポスト30と、電極ポスト30に接続電極42が接合された電子部品40とを含み、電極ポスト30と電子部品40の接続電極42とは電極ポスト30の金属材料と異なる金属を含む合金層31(金・インジウム合金層など)によって接合されている。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】ポスト状の電極を用いて大電流を通電した際の熱ストレスを緩和するとともに、このポスト状電極を確実に半導体チップの電極に接合できる半導体装置を提供する。

【解決手段】半導体チップ1のおもて面電極とポスト電極15との接合面の少なくとも一方に、有機被膜で保護された金属粒子を塗布し、前記半導体チップのおもて面電極とポスト電極15との間を加圧するとともに加熱して、前記有機被膜を破壊して前記金属粒子を露出させてこの金属粒子を活性接合させて、前記おもて面電極とポスト電極とを接合する。

(もっと読む)

オーバーレイミスアライメントを減少させた直接ボンディング法

【課題】第1のウェーハを第2のウェーハに直接ボンディングする新規な方法を提供する。

【解決手段】本発明の方法は、固有湾曲を有する第1のウェーハ(100)を固有湾曲を有する第2のウェーハ(200)に直接ボンディングする方法であり、2枚のウェーハのうちの少なくとも一方(100)が少なくとも一組のマイクロコンポーネント(110)を備える。本方法は、2枚のウェーハ間でのボンディング波の伝搬を開始させるように、2枚のウェーハ(100、200)を互いに接触させる少なくとも1つのステップを含む。接触させるステップ中に、回転放物面の形態の所定のボンディング湾曲(KB)が、ウェーハ(100)のボンディング前の固有湾曲に依存して2枚のウェーハのうちの一方に与えられ、他方のウェーハが所定のボンディング湾曲(KB)と一致するように自由である。

(もっと読む)

ドライバ

【課題】ドライバの半導体集積回路装置の出力端子数が増加しても、半導体集積回路装置内部の配線層による電圧降下を防止する。

【解決手段】第1の配線層と第2の配線層とが形成されたフィルム基板と、前記フィルム基板上にチップオンフィルム方式で実装された半導体チップとを有し、前記第1の配線層と前記半導体チップの出力端子とが電気的に接続され、前記第2の配線層によって、前記半導体チップの複数の端子同士が電気的に接続されており、前記第2の配線層を介して、前記半導体チップの電源、或いはクロックが伝達される。前記第2の配線層は、前記半導体チップと前記フィルム基板との間に形成される。

(もっと読む)

超音波フリップチップ実装方法

【課題】実装後に生じる熱応力を確実に低減し、良好な接続状態を得ることができ、実装品の信頼性を高めることが可能な超音波フリップチップ実装方法を提供する。

【解決手段】チップ11と配線部品21との間のバンプ14に超音波を印加してチップ11と配線部品21とを超音波フリップチップ実装する。チップ11の線膨張係数Ccと配線部品21の線膨張係数Csの関係がCc<Csである場合に、フリップチップ実装時におけるチップ11の実装時温度Tfcと、フリップチップ実装時における配線部品21の実装時温度Tfsと、配線部品21にチップ11が実装された実装品の取り出し温度Toとの関係を、Tfc>Tfs>Toとする。

(もっと読む)

実装構造、電子部品、回路基板、基板組立体、電子機器、及び応力緩和部材

【課題】 半導体装置の接合部の耐圧迫性や長期信頼性を改善することができ、実装した半導体装置を容易に回路基板から取り外すことができる実装構造を提供することを課題とする。

【解決手段】 電子部品10を回路基板18に実装するための実装構造は、電子部品10と回路基板18の間に設けられた絶縁シート積層体16と、絶縁シート積層体16中に形成された複数の螺旋状導体14とを有する。螺旋状導体14の一端は電子部品10の外部接続端子12に接合される。螺旋状導体14の他端は回路基板18接続電極18aに接合される。

(もっと読む)

モジュールの製造方法

【課題】半導体素子のサイズによらずに気泡の混入確率が低減されたモジュールの製造方法の提供を目的とする。

【解決手段】本発明のモジュールの製造方法は、絶縁層の一の面に導体のパターンが形成された配線板と、導体上にバンプを介してフェイスダウンで実装された機能素子とを備え、配線板の機能素子が実装された位置の、機能素子の投影面よりも小さく、かつ、バンプが導体に接合された部位よりも内側の領域に、絶縁層の厚さ方向に沿って開口部が形成されており、機能素子及び配線板間の隙間と、開口部とが封止樹脂によって封止されているモジュールの製造方法であって、配線板の導体上に、バンプを介して機能素子を実装する実装工程と;機能素子及び配線板間の隙間と、開口部とを、封止樹脂によって封止する樹脂封止工程と;を有することを特徴とする。

(もっと読む)

素子の基板実装方法、および、その基板実装構造

【課題】電解メッキを用いて配線基板と素子電極との強固な接合が得られるように素子の基板実装を実現する。

【解決手段】トリオ基板2にシードメタル配線層4を形成し、LEDチップ3の電極パッド(3P,3N)がシードメタル配線層4と電気的に非接続で、その上方に位置するように、LEDチップ3をトリオ基板2に仮固定し、シードメタル配線層4を給電層として電解メッキを行う。このときシードメタルからメッキが成長し始め、電気的接触後は、そのとき既に形成されたメッキ層と電極パッド面とを1つの成長面としてメッキが成長する。電極パッド1つに対しては、複数箇所からの非連続メッキ成長による接合面やギャップがないシームレスなメッキ成長を行うことができ、これによりLEDチップ3を配線基板に強固に固定できる。

(もっと読む)

ダイシングテープ一体型半導体裏面用フィルム

【課題】半導体素子のピックアップの際の良好な剥離性を維持しつつ、半導体ウェハのダイシングの際の半導体素子のチップ飛びやチッピングの発生、ダイシングの際に用いる切削水が粘着剤層とフリップチップ型半導体裏面用フィルムとの間に進入するのを防止することが可能なダイシングテープ一体型半導体裏面用フィルム及び半導体装置の製造方法を提供する。

【解決手段】本発明のダイシングテープ一体型半導体裏面用フィルムは、被着体上にフリップチップ接続された半導体素子の裏面を保護するためのフリップチップ型半導体裏面用フィルムと、ダイシングテープとを備えるダイシングテープ一体型半導体裏面用フィルムであって、前記ダイシングテープは、基材上に少なくとも粘着剤層が設けられた構造であり、前記フリップチップ型半導体裏面用フィルムは前記粘着剤層上に設けられており、前記粘着剤層は、放射線の照射により、フリップチップ型半導体裏面用フィルムに対する粘着力が低下する放射線硬化型であることを特徴とする。

(もっと読む)

フリップチップ型半導体裏面用フィルム、ダイシングテープ一体型半導体裏面用フィルム、半導体装置の製造方法、及び、フリップチップ型半導体装置

【課題】被着体上にフリップチップ接続された半導体素子に反りが発生するのを抑制又は防止することが可能なフリップチップ型半導体裏面用フィルム、及びダイシングテープ一体型半導体裏面用フィルムを提供する。

【解決手段】被着体上にフリップチップ接続された半導体素子の裏面に形成するためのフリップチップ型半導体裏面用フィルムであって、熱硬化前のフリップチップ型半導体裏面用フィルムの全体積に対する、熱硬化による収縮量が2体積%以上30体積%以下であるフリップチップ型半導体裏面用フィルム。

(もっと読む)

半導体発光装置の製造方法

【課題】フリップチップ用のLED素子はp型半導体層を削ってn型半導体層を露出させるため、しばしばp側バンプとn側バンプの間に段差を持つ。この段差はLED素子の接続信頼性を劣化させることがある。

【解決手段】複数の回路基板領域を含む大判基板80に電極パターンを形成してから、n側バンプ23が接続する領域に段差と略等しい厚さを有する補正膜17を形成する。続いてLED素子13を大判基板80に配置して接合する。最後に大判基板80を個片化し半導体発光装置10を得る。接合工程前の大判基板80処理段階で補正膜17を形成する工程を追加したので簡単に高い接続信頼性が得られた。

(もっと読む)

2つの金属表面を永久的に接続するための方法

実装方法及び実装装置

【課題】チップと実装基板との間の位置合わせを高い位置精度で行うことができる実装方法及び実装装置を提供する。

【解決手段】第1の基板を第2の基板に実装する実装方法において、第1の基板の一の面を清浄化処理する清浄化処理工程S15と、清浄化処理工程S15の後、第1の基板を保持している第1の基板保持部と、第2の基板を保持している第2の基板保持部との距離を近づけることによって、一の面であって親水化処理されている第1の領域と、第2の基板の表面であって親水化処理されている第2の領域とを、液体を介して接触させる接触工程S17とを有する。

(もっと読む)

フリップチップ実装装置及びその製造方法

【課題】半導体回路基板に形成された高周波回路の高周波特性への影響を抑えることができるフリップチップ実装装置を提供する。

【解決手段】基板26の一面上に、導体層23、誘電体層25、及び導体層と対向するように配された配線層21が順に積層されてなる実装基板2上に、半導体回路基板1をフリップチップ接合させたフリップチップ実装装置であって、実装基板は、基板の一部が露呈する開口部Aを備え、実装基板と半導体回路基板とが、バンプ31を介して電気的に接続されており、実装基板と半導体回路基板との間には、開口部による空間3が設けられていることを特徴とするフリップチップ実装装置。

(もっと読む)

フリップチップ実装装置

【課題】インピーダンスの不連続性を抑えるとともに、反射損失の低減することができ、かつ、半導体回路基板(CMOS−IC)の特性インピーダンスに影響を及ぼすことなくフリップチップ実装する。

【解決手段】基板26の一面上に、第一導体層21、第一誘電体層24、第二導体層23、第二誘電体層25が順に積層されてなる実装基板2上に、半導体回路基板1をフリップチップ接合させたフリップチップ実装装置であって、実装基板2は、第二導体層23の一部が露呈する開口部Aを備え、第二導体層23の露呈部に配した金属薄膜27及び第一バンプ31を介して、実装基板2と半導体回路基板1とが電気的に接続されており、実装基板2と半導体回路基板1との間には空間が設けられたフリップチップ実装装置。

(もっと読む)

3次元でパッケージされた集積回路に対するダイ間結合の間の静電放電ダメージへの感受性の低減

本発明は、電子集積回路パッケージの製作、より具体的には3次元でパッケージされた集積回路を製造する際の静電放電ダメージの軽減に関する。一実施形態では、第2層ダイが第1層ダイと接触して配置されるとき、第2層ダイおよび第1層ダイ上の他の信号導電バンプおよびパワー導電バンプが電気的に接触する前に、第2層の基板と電気的に結合された第2層の周辺部付近の導電バンプが、第1層の基板と電気的に結合された第1層の対応する導電バンプと接触する。  (もっと読む)

(もっと読む)

21 - 40 / 322

[ Back to top ]