Fターム[5F044LL00]の内容

ボンディング (23,044) | フェイスダウンボンディング (4,630)

Fターム[5F044LL00]の下位に属するFターム

直接ハンダ付け状態 (1,160)

ハンダ付け方法 (478)

導電ペースト、接着剤によるもの (335)

異方性導電材料によるもの (820)

絶縁材料でチップと配線を密着させるもの (1,009)

介在物を介して接続 (286)

接触によるもの (125)

基板とチップ間のスペーサー (91)

ハンダパッキング (4)

Fターム[5F044LL00]に分類される特許

1 - 20 / 322

半導体デバイスおよびその製造方法

銅を含む電極連結構造体

バンプ接合構造体の製造方法

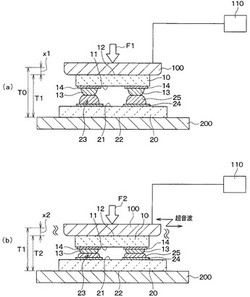

【課題】バンプを有する第1の部品を、当該バンプを介して第2の部品に接合してなるバンプ接合構造体の製造方法において、沈み込み量のばらつきを抑制して安定した接合が実現できるようにする。

【解決手段】バンプ13への超音波振動の印加を開始し、当該超音波振動の印加を続けながら、第1の荷重F1よりも大きい第2の荷重F2を、第1の部品10および第2の部品20に印加することにより、第1の工程の終了時点よりも更に第2の部品20側へ第1の部品10が沈み込むようにバンプ13を潰して接合させる第2の工程において、第1の部品10の第2の部品20側への沈み込みによる変位量を沈み込み量としたとき、第2の工程では、第2の工程における沈み込み量x2をモニタし、当該沈み込み量x2が所定値になった時点で、超音波振動の印加を停止し、第2の荷重F2の印加のみとする。

(もっと読む)

基板張り合わせ方法

【課題】 より最適に半導体ウエハ同士の接合を行うことができる基板張り合わせ方法を提供する。

【解決手段】 基板張り合わせ方法は、第1条件下で、第1基板(W1)と第2基板(W2)とのそれぞれ被加工領域毎(ES)に設定された計測点のうち、予め選択された所定数のサンプル計測点(SA)の位置を計測する計測工程(P11、P12)と、サンプル計測点の計測位置を演算パラメータとして統計演算を行い、第1基準マーク及び第2基準マークを基準としたそれぞれの被加工領域の配列のオフセットなどを算出する算出工程(P13)と、第1条件とは異なる第2条件下で、第1基板及び第2基板に対して表面を活性化させる表面活性工程(P15)と、第2条件下で、第1基準マーク及び第2基準マークを観察しながら、算出工程の算出結果に基づいて第1基板と第2基板とを重ね合わせる重ね合わせ工程(P18、P19)と、を備える。

(もっと読む)

電子デバイス、及び電子機器

【課題】電子デバイスを小型化、低背化し、且つコストを低減する手段を得る。

【解決手段】電子デバイスは、第1の電子素子20と、第1の電子素子20を搭載する絶縁基板11と、を備えた電子デバイスであって、絶縁基板11は一方の主面に第1の電子素子20を搭載する電極パッド12を有すると共に、他方の主面に実装端子13を備え、第1の電子素子20に設けた端子と電極パッド12とは、接続用導電部材15を介して導通接続されている。

(もっと読む)

半導体装置およびその設計方法、電子機器

【課題】半導体装置とプリント基板で適用可能なプロセスが異なる際に、コストあるいは回路面積の増加を抑制する。

【解決手段】半導体装置1は、その底面に規則的に配置された複数の裏面電極10を備える。複数の第1裏面電極10aは、M行N列(M、Nは4以上の整数)のマトリクス状に配置される仮想的な格子点のうち、半導体装置1の最外周の複数の第1格子点30aに対応する箇所に設けられる。複数の第2裏面電極10bは、最外周を除く(M−2)行(N−2)列の格子点から複数の格子点を間引いた結果残る複数の第2格子点に対応する箇所に配置される。

(もっと読む)

半導体パッケージの製造方法

【課題】半導体チップに熱及び圧力を伝えるツールへの封止樹脂の付着を抑制しながら、高い接合信頼性を実現することのできる半導体パッケージの製造方法を提供する。

【解決手段】突起状電極を有する厚みが150μm以下の半導体チップに、該半導体チップに熱及び圧力を伝えるツールを接触させ、封止樹脂を介して該半導体チップを対向基板に接合する半導体パッケージの製造方法であって、前記ツールと前記半導体チップとの接触面の面積が、前記半導体チップの面積よりも小さく、前記接触面のエッジと前記半導体チップのエッジとの最短距離(d1)が、前記ツールの全周において、0μmより大きく200μm以下である半導体パッケージの製造方法。

(もっと読む)

パッケージされたデバイス、パッケージング方法及びパッケージ材の製造方法

【解決課題】特殊な技術や装置を必要とせず、接合の際に電気的な接続を歩留まりよく確立可能な、パッケージされたデバイス及びパッケージング方法並びにそれに用いられるパッケージ材の製造方法を提供する。

【解決手段】電子回路、MEMSその他のデバイスを搭載したデバイス基板10と、ビア配線21を配設してかつキャビティ22を有するパッケージ材20とを接合して成る。ビア配線21と一体化した接続用バンプ24がキャビティ22内に突出しており、かつデバイスに接続された配線接続用パッド12が接続用バンプ24と対向して接続していることにより、接続用バンプ24を経由してデバイスがビア配線21に配線接続している。

(もっと読む)

半導体装置

【課題】50ミクロンピッチ以下の微細ピッチ電極を有する半導体素子を基板上のパッドもしくは配線を接続する構造において、接続時の加熱または荷重負荷時に発生するバンプ間ショートや、高歪みによる接続部破断を防止しあるいは接触抵抗を低減し、高信頼性で高速伝送に対応可能な半導体装置を提供する。

【解決手段】基板20と半導体素子1は縦弾性係数(ヤング率)が65GPa以上600GPa以下のバンプ11と、錫、アルミニウム、インジウム、あるいは鉛のいづれかを主成分とする緩衝層12を介して接続されており、バンプ11と基板20上のパッドもしくは配線21の対向した面の少なくとも一方に突起が形成され、超音波により接続することにより低温接続が可能な半導体装置。

(もっと読む)

半導体装置とその製造方法

【課題】上下の半導体チップ間の隙間を維持しつつ、アンダーフィル樹脂の充填前における半導体チップ間の接続強度を高めることを可能にした積層型半導体装置を提供する。

【解決手段】実施形態の半導体装置1は、第1の半導体チップ2と、第1の半導体チップ2上に積層された第2の半導体チップ3とを具備する。第1および第2の半導体チップ2、3は、バンプ接続体6を介して電気的に接続されている。第1および第2の半導体チップ2、3の少なくとも一方には、ストッパ用突起7と接着用突起8とが設けられている。ストッパ用突起7は、第1および第2の半導体チップ2、3の他方に非接着状態で接触している。接着用突起8は、第1および第2の半導体チップ2、3に接着されている。

(もっと読む)

電子装置及びその製造方法

【課題】 信頼性の高い電子装置を提供すること。

【解決手段】 外表面に電極31を有する電子部品3と、基板本体21、および基板本体21の一方主面に設けられ電子部品3の電極31と電気的に接続された電気配線22を含む配線基板2とを備え、基板本体21の表面と、電子部品3の下面とは、直接接合している電子装置1である。電子部品3と配線基板2との間には別体の部材が存在しない。よって、異なる部材同士の境界が減少するので、剥離の可能性を低減できる。

(もっと読む)

アライメント装置およびアライメント方法

【課題】より高速に且つより高精度に2つの対象物の位置合わせを行うことが可能なアライメント技術を提供する。

【解決手段】ボンディング装置30は、チップCPを保持するヘッド部33Hと基板WTを保持する基板保持部と、両対象物CP,WTの相対位置誤差を測定する測定手段(撮像部35a,35b等)とを備える。測定手段は、両対象物CP,WTが対向配置され且つ基板WTの載置面に平行な平面内においてチップCPが所定のボンディング位置(X、Y)に配置された状態で、両対象物CP,WTの各対向面とは反対側の面である2つの反対向面のうちの少なくとも一方面側(チップCPの上側および/または基板WTの下側)から、チップCPに関するアライメントマークMC1と基板WTに関するアライメントマークMC2とを撮像することによって、両対象物MC1の相対位置誤差を測定する。

(もっと読む)

半導体装置

【課題】半導体チップの搭載時における位置ずれや短絡不良の発生が抑制される半導体装置を提供する。

【解決手段】端面CEGを有し、電気回路を含む半導体素子CHPと、半導体素子CHPの電気回路と電気的に接続される複数のリードフレームLFと、半導体素子CHPを覆うように形成される樹脂材料MRとを備えている。上記リードフレームLFの半導体素子CHP側の端部には半導体素子CHPの端面CEGに沿って延びるとともに半導体素子CHPの端面CEGに連なる裏面CHPbに対向する位置にまで延びる半導体素子保持部IL1,IL2が形成されている。

(もっと読む)

フリップチップ型半導体裏面用フィルム、及び、ダイシングテープ一体型半導体裏面用フィルム

【課題】半導体素子を保護することができ、且つ、半導体素子の貼り剥がしを容易とするフリップチップ型半導体裏面用フィルムを用いた半導体装置の製造方法を提供する。

【解決手段】 ダイシングテープとフリップチップ型半導体裏面用フィルムとを備えるダイシングテープ一体型半導体裏面用フィルムを用いた半導体装置の製造方法であって、フリップチップ型半導体裏面用フィルムは、半導体素子の裏面に形成する際に半導体素子の裏面に対向しない側の表面粗さ(Ra)が、硬化前において、50nm〜3μmの範囲内であり、ダイシングテープ一体型半導体裏面用フィルム上に半導体ウエハを貼着する工程と、半導体ウエハをダイシングする工程と、ダイシングにより得られた半導体素子をピックアップする工程と、半導体素子を被着体上にフリップチップ接続する工程とを具備する半導体装置の製造方法。

(もっと読む)

電子部品の実装構造体

【課題】接続部に不具合の生じにくい構造を備えた電子部品の実装構造体を提供する。

【解決手段】電子部品4の実装構造体10は、コアとなる樹脂の表面の長手方向に沿う複数箇所が金属からなる導電膜で覆われた構造を有するバンプ電極23を備えた電子部品4と、金属端子12を備えた基板11とを電気的に接続することで構成されており、バンプ電極23の金属端子12と接続される位置に、金属端子12との接触領域を少なくとも二分割する溝部が形成されている。

(もっと読む)

電子部品実装体の製造方法

【課題】樹脂コアを有するバンプ電極を備えた電子部品を簡便かつ確実に実装でき、歩留まりよく電子部品実装体を製造する方法を提供する。

【解決手段】本発明の電子部品実装体の製造方法は、コアとなる樹脂の表面に導電膜が形成されたバンプ電極を有する電子部品と、金属端子を有する基板とを電気的に接続してなる電子部品実装体の製造方法であって、電子部品の少なくともバンプ電極を加熱し、樹脂の硬度を上昇させる加熱工程と、硬度を上昇させたバンプ電極を金属端子に接触させた状態で電子部品を基板に押圧し、電子部品を実装する実装工程と、を有することを特徴とする。

(もっと読む)

半導体装置の製造方法

【課題】コストの上昇を抑えながら高い信頼性の接合を実現することができる半導体装置の製造方法を提供する。

【解決手段】半導体素子に設けられた第1の電極の表面の機械加工を行って、当該機械加工前よりも粒径が小さい微結晶の第1の層を設け、前記半導体素子が搭載される搭載部材に設けられた第2の電極の表面の機械加工を行って、当該機械加工前よりも粒径が小さい微結晶の第2の層を設ける(ステップS1)。前記第1の電極を構成する金属が固相拡散する温度未満、かつ前記第2の電極を構成する金属が固相拡散する温度未満の温度で、前記第1の層の表面に存在する酸化膜及び前記第2の層の表面に存在する酸化膜を還元する(ステップS2)。前記第1の層及び前記第2の層を互いに固相拡散接合する(ステップS4)。

(もっと読む)

半導体素子の実装方法

【課題】基板の第1電極に、半導体素子の第2電極を超音波接合することにより半導体素子を実装する方法において、第1電極と第2電極との間の金属接合を、求められる接合強度を確保しながら、少なくとも銅を含む金属間の接合として実現する半導体素子の実装方法を提供する。

【解決手段】第1電極3と第2電極5との間の金属接合を、少なくとも銅を含む金属間の超音波接合として行う際に、少なくとも第1電極3と第2電極5との接合界面の周囲に還元性を有する接合補助剤7が存在する状態にて超音波接合を行う。これにより、第1電極3と第2電極5との接合界面に既に形成されている銅の酸化膜6を除去できるとともに、超音波接合の実施に伴って接合界面に酸化膜が形成されることを抑制することができる。

(もっと読む)

半導体装置、センサーおよび電子デバイス

【課題】貫通電極を有する半導体基板の積層時に、半導体基板の破損を防止する。

【解決手段】突起電極117が形成された第2基板100上に、貫通電極40が形成された第1基板10が積層され、貫通電極40には凹部28を有し、凹部28に突起電極117が入り込んで積層され、凹部28の開口幅に対して、突起電極117の先端幅が小さくなっている。

(もっと読む)

半導体装置の製造方法

【課題】電子部品を接続して半導体装置を製造する際に、加熱加圧ツールに接続材料が付着することを防止するツール保護材において不具合を発生させることなく、加熱加圧ツールの汚染を防止し、歩留りを向上させることができる半導体装置の製造方法を提供すること。

【解決手段】相対向する第1電子部品1及び第2電子部品2の間に接続材料4を介在させ、第1電子部品1を加熱加圧ツール3によって加熱及び加圧し、第1電子部品1及び第2電子部品2を接続して半導体装置を製造する際、加熱加圧ツール3の加熱加圧面31と第1電子部品1の被加熱加圧面である背面13との間に、加熱加圧面31と同等の大きさで、金属箔、シリコンチップ、及びセラミックシートのいずれか一つからなるツール保護材5を介在させて加熱及び加圧を行う。

(もっと読む)

1 - 20 / 322

[ Back to top ]