Fターム[5F044LL01]の内容

ボンディング (23,044) | フェイスダウンボンディング (4,630) | 直接ハンダ付け状態 (1,160)

Fターム[5F044LL01]の下位に属するFターム

基板の貫通孔を介してハンダ付け (18)

Fターム[5F044LL01]に分類される特許

81 - 100 / 1,142

電子部品、及びその製造方法

【課題】機能部を有する機能性素子が配線基板上に搭載されるとともに、少なくとも配線基板と機能性素子との接合部を保護するための封止層が設けられている電子部品において、封止層の機能部への侵入を防止し、当該機能部が動作できるような空間を、電子部品のサイズを大型化させることなく、また工程数を増大させることなく形成する。

【解決方法】配線基板の導電層における非接続領域を保護するための保護層を、前記配線基板の主面上において、前記配線基板上に搭載した機能性素子と相対向する位置であって、その機能部と相対向する位置を除く領域にまで延在させ、封止層を配線基板と機能性素子との接合部から前記機能性素子の前記機能部にまで延在させることなく、前記配線基板の前記主面と前記機能部との間に空隙を形成するようにして、電子部品を構成する。

(もっと読む)

電子部品、及びその製造方法

【課題】機能部を有する機能性素子が配線基板上に搭載されるとともに、少なくとも配線基板と機能素子との接合部を保護するための封止層が設けられている電子部品において、封止層の機能部への侵入を防止し、当該機能部が動作できるような空間を、電子部品のサイズを大型化させることなく形成する。

【解決方法】配線基板の主面上において、機能性素子の機能部と対向する領域に撥水層を形成し、封止層を形成する際のその構成樹脂が、配線基板の主面と機能性素子の機能部との間に流入するのを抑制して、これらの間に前記機能部が動作できるための空間を形成するようにして、電子部品を構成する。

(もっと読む)

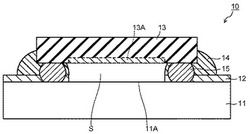

半導体装置およびその製造方法

【課題】キャビティの上面側に設けられた半導体構成体用凹部内に半導体構成体を配置した半導体装置において、薄型化する。

【解決手段】キャビティ1の上面側に設けられた半導体構成体用凹部4内には半導体構成体11がフェースダウン方式で配置されている。半導体構成体用凹部4内には絶縁層35が半導体構成体11を覆うように設けられている。絶縁層35の上面は、キャビティ1の上面に設けられた上層オーバーコート膜33の上面と面一となっている。絶縁層35および上層オーバーコート膜33の上面には上層配線37が設けられている。この場合、キャビティ1および半導体構成体11上には上層絶縁膜を設けておらず、したがってその分薄型化することができる。

(もっと読む)

電子部品モジュール及び電子部品

【課題】本発明は、ハンダを溶融したときに発生する気泡を外部に排出して、端子電極と実装基板とを接合するハンダ内に存在するボイドを減らしてハンダ接合の信頼性を向上させることができる端子電極を有する電子部品モジュール及び電子部品を提供する。

【解決手段】本発明は、ベース基板1と、ベース基板1の一方の面に実装してある複数の電子部品2と、ベース基板1の他方の面に形成してある複数の端子電極3とを備える電子部品モジュール10である。端子電極3は、3層以上の電極層3a〜3cを積層することで形成され、電極層3a〜3cのそれぞれの面積が、ベース基板1側から順に小さくなる。

(もっと読む)

液状封止樹脂組成物および液状封止樹脂組成物を用いた半導体装置

【課題】高熱伝導率と低誘電率、高隙間流入性とを兼備した液状封止樹脂組成物を提供すること。

【解決手段】半導体素子と基板とをバンプ接続した後、半導体素子と基板との隙間を封止する際に用いる液状封止樹脂組成物であって、(A)エポキシ樹脂、(B)硬化剤、(C)無機充填材を含有し、(C)無機充填材が球状アルミナと球状シリカとの混合物を含み、且つ(D)塩基性化合物を含有することを特徴とする液状封止樹脂組成物であり、好ましくはpH値が7以上である液状封止樹脂組成物。

(もっと読む)

アンダーフィル樹脂組成物およびこれを用いた半導体装置

【課題】 アンダーフィルにより樹脂封止された半導体チップを、樹脂残渣少なく且つ基板表面を傷つけることなく配線基板から取り外すことができるようにする。

【解決手段】 配線基板10上にはんだバンプ8を介して半導体チップ1が搭載され、封止樹脂9により封止されている半導体装置において、封止樹脂9にはシロキサン骨格を有する多層構造の粒子が添加されている。半導体チップ1をリペアする際には、加熱して封止樹脂9の密着強度を低下させた状態で剥離用プレート12を、配線基板10と半導体チップ1との隙間に挿入して〔(b)図〕、封止樹脂9を配線基板10から剥離し、半導体チップ1を取り除く〔(c)図〕。

(もっと読む)

集積回路および中継基板

【課題】本発明は、マイクロ波帯やミリ波帯において、1つの集積回路で複数の機能を実現する集積回路と、その集積回路が表面実装される中継基板とに関し、特性の劣化の原因となる広帯域設計をすることなく、多様に異なる帯域に柔軟に対応可能とすることを目的とする。

【解決手段】基板上に個別に形成された複数の回路と、前記基板上で前記複数の回路に隔たって形成され、前記複数の回路の何れにも接続され得る特定の回路とを備え、前記特定の回路と前記複数の回路とは、表面実装型の中継基板との突起電極を介する接続に供されるパッドを有する。

(もっと読む)

回路基板、半導体部品、半導体装置、回路基板の製造方法、半導体部品の製造方法及び半導体装置の製造方法

【課題】容易に電極部間のピッチを狭めたり、容易に電極部上に微小な半田バンプ形成したりすることができる回路基板等の技術を提供すること。

【解決手段】回路基板10は、電極部21を有する配線部20を備える。電極部は、銅層22と、銅層上の酸化銅層23と、酸化銅層を貫通する孔24とを有する。孔により露出された銅層露出部25上には、フリップチップ実装用の半田バンプ1が形成される。半田バンプ形成時には、電極部上にクリーム半田等が塗布されて加熱される。半田は、銅には接着し易いが、酸化銅には接着にくい性質を有しており、この関係が利用される。つまり、クリーム半田加熱時には、半田バンプは、接着し易い銅層露出部上に形成され、酸化銅層上には形成されない。これにより、孔の大きさを調整することで、容易に微小な半田バンプを形成することができ、また、電極部の構造を複雑化する必要もないので、容易にピッチを狭めることができる。

(もっと読む)

回路基板及び電子装置

【課題】開示の技術によれば、回路基板の表面に形成される保護膜の膜厚の抑制と、該保護膜による回路基板の表面保護と、を実現しつつ、電極パッドに供給される半田ペーストを増加することができる。

【解決手段】

少なくとも電子部品がハンダ接続により搭載される電極パッド領域を除き表面保護膜が形成された回路基板であって、上記表面保護膜は多層で構成され、上記電極パッド領域の開口面積が下層から上層に向かって拡大する部分を有する回路基板。

(もっと読む)

半導体装置およびその製造方法

【課題】半導体チップと外部基板を接合する接合樹脂による接合応力を均一化し、半導体チップのトランジスタ特性変動が生じない半導体装置を提供する。

【解決手段】フリップチップ組立において、半導体チップ1と外部基板13の間に接合樹脂17を注入して接合させる際、本接合樹脂を2種類にわけ、半導体チップ1の中心部分には低応力接合樹脂23、周辺部分には高応力接合樹脂21を注入したり、半導体チップ1の中心部分にはSiN等をはじめとした第1層表面保護膜とポリイミドやPBO等をはじめとした第2層表面保護膜の2層構造、周辺部分にはSiN等をはじめとした第1層表面保護膜の1層構造とすることにより、半導体チップ1内のトランジスタ特性変動を抑制する。

(もっと読む)

基板の接続構造、基板セット、光センサアレイ装置及び基板を接続する方法

【課題】基板と基板との突き合わせ接続時に、2つの基板の間の相対的な位置がずれていても、2つの基板が電気的に接続される基板の接続構造を提供する。

【解決手段】本明細書に開示する基板の接続構造は、複数の第1電極15が配置された第1電極面12を有する第1基板11と、複数の第2電極16が配置された第2電極面14を有し、第2電極面14が第1電極面12と対向する第2基板13と、を備え、複数の第2電極16それぞれは、第2電極面14の中心C2を除いて、第1電極15と対向する第2電極面14上の位置に対して、第2電極面の中心C2とは反対の方向にずれて配置されており、複数の第2電極16それぞれは、対向する第1電極15とバンプ17を介して電気的に接続している。

(もっと読む)

扁平はんだグリッド配列のための処理方法、装置及びコンピュータシステム

【課題】プリント回路基板表面実装部品のための扁平はんだグリッド配列を提供する。

【解決手段】スタンドオフ接触配列は、フリップフロップパッケージの実装基板とボードとの間に配置される(410)。このスタンドオフ接触配列は、実装基板上の扁平なはんだバンプをボード上の扁平なはんだペーストと結合する(430)ことによって、形成可能である。その後に、スタンドオフ接触配列は、実装基板上の扁平なはんだバンプに対してボード上の扁平なはんだペーストをリフローする(440)ことによって、形成される。

(もっと読む)

電子装置

【課題】 電気特性の変化を抑制することが可能な電子装置を提供すること。

【解決手段】 電子素子22および電子素子22が第1主面21Aに搭載され、第1主面21Aと対向しており、かつ第1主面21Aに比して平面視での面積が大きい第2主面21Bを有する基板を有するチップ部品2と、チップ部品2が第1主面21Aを第1空間S1を介して対向させた状態で搭載される配線基板31と、基板21の第2主面21Bから配線基板31の表面にかけて設けられる樹脂層4とを備え、基板31と基板31の側方に位置する樹脂層4との間に、第1空間S1に通じる第2空間S2が設けられている電子装置1である。

(もっと読む)

半導体装置の製造方法

【課題】半導体チップ同士を積層する際に生じる曲げモーメントによる破損を防止する半導体装置の製造方法を提供する。

【解決手段】一面に形成された表面バンプFB及び積層方向から見て表面バンプFBと重なるように他面に形成された裏面バンプBBを含むコアチップCC1と、一面に形成された表面バンプFB及び積層方向から見て表面バンプFBと重ならないように他面に形成された裏面バンプBBを含むインターフェースチップIFとを準備し、コアチップCC1の裏面バンプBBとインターフェースチップIFの表面バンプFBが接続するように、インターフェースチップIFの裏面バンプBBに対応する位置に凹部GRを有するボンディングツールBTを用いて積層方向に重ね合わせる。これにより、積層時にチップに曲げモーメントが発生しないことからチップの破損を防止することが可能となる。

(もっと読む)

半導体装置

【課題】アンダーフィル樹脂の充填が困難な場合であっても、半導体装置の信頼性が低下することを防ぐ技術を提供する。

【解決手段】半導体チップ(2)と、基板(8)と、チップ面に形成されたチップ面絶縁層(7)と、基板面に形成された基板面絶縁層(10)と、フリップチップボンディングによってチップ側電極(4)と基板側電極(9)とを接続する接続部材(11)とを具備する半導体装置(1)を構成する。接続部材(11)は、チップ面絶縁層(7)を貫通するバンプ部分(12)と、基板面絶縁層(10)を貫通する低融点部分(13)と、バンプ部分(12)と低融点部分(13)とが接触している接触領域(16)とを備えることが好ましい。ここで、チップ面絶縁層(7)と基板面絶縁層(10)とは、空隙(14)を介して向かい合うように配置されている。そして、接触領域(16)は、空隙(14)によって露出される表面を有する。

(もっと読む)

フリップチップ実装構造

【課題】フレキシブル基板に半導体素子をフェイスダウンで実装する半導体装置において、低コストな手段で、小型・薄型構造を妨げずに放熱性を高めるフリップチップ実装構造を提供する。

【解決手段】半導体素子1とフレキシブル基板10とがバンプ2を介して接合され、半導体素子とフレキシブル基板との間が封止樹脂9により封止されたフリップチップ実装構造において、フレキシブル基板には、半導体素子と対抗する面の一部にランド3が形成され、フレキシブル基板は、バンプと接合されることで画定される領域の内側で屈曲し、このときのランドと半導体素子との間隔が、バンプと接合後の半導体素子とランドとの間隔よりも狭小になっている。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】接続電極を覆うアンダーフィル樹脂が形成されている場合にも、アライメントマークの認識が容易な半導体装置を提供する。

【解決手段】半導体素子11と、半導体素子11に形成されたパッド電極12と、半導体素子11に形成されたアライメントマーク15と、パッド電極12上に形成された接続電極と、接続電極を覆うように形成されたアンダーフィル樹脂18とを備える半導体装置10を構成する。そして、この半導体装置10は、半導体素子11からの高さが接続電極よりも大きいアライメントマーク15を備える。

(もっと読む)

半導体装置の製造方法

【課題】半田バンプ同士の接続性を良好に保ちつつ、溶融後の半田バンプ内に発生するボイドを抑制した半導体装置の製造方法を提供する。

【解決手段】第1の半田バンプ1を有する第1の基板2と第2の半田バンプ3を有する第2の基板4とを、半田バンプ1、3同士を仮固定しつつ積層した後に炉内に配置する。炉内に不活性ガスを導入した後、炉内の温度を半田バンプ1、3の溶融温度以上の温度域まで上昇させる。炉内の温度を半田バンプ1、3の溶融温度以上の温度域に維持しつつ、不活性ガスを排気して減圧雰囲気とした後、炉内にカルボン酸ガスを導入し、第1および第2の半田バンプ1、3の表面に存在する酸化膜を除去しつつ、溶融した第1の半田バンプ1と第2の半田バンプ3とを一体化して接合する。

(もっと読む)

フリップチップ用樹脂封止材及び半導体実装体の製造方法

【課題】リフロー装置を用いて電極接合と樹脂封止とを行う際に、信頼性の高い電極接合を行うことができ、かつ、基板又は半導体素子の反りを抑制することのできるフリップチップ用樹脂封止材を提供する。また、該フリップチップ用樹脂封止材を用いた半導体実装体の製造方法を提供する。

【解決手段】リフロー装置を用いて電極接合と樹脂封止とを行う際に用いられるフリップチップ用樹脂封止材であって、エポキシ化合物と、酸無水物硬化剤又はフェノール系硬化剤とを含有し、260℃でのゲルタイムが20秒以上であり、回転式レオメーターにより測定した1Hzでの50〜250℃の間における最低溶融粘度が1Pa・sより小さいフリップチップ用樹脂封止材。

(もっと読む)

フリップチップ型半導体裏面用フィルム、ダイシングテープ一体型半導体裏面用フィルム、フリップチップ型半導体裏面用フィルムの製造方法、及び、半導体装置

【課題】被着体上にフリップチップ接続される半導体素子の裏面に電磁波シールド層を設けることができ、かつ、当該電磁波シールド層を有する半導体装置を、生産性を低下させることなく製造できること。

【解決手段】 被着体上にフリップチップ接続された半導体素子の裏面に形成するためのフリップチップ型半導体裏面用フィルムであって、接着剤層と、電磁波シールド層とを有するフリップチップ型半導体裏面用フィルム。

(もっと読む)

81 - 100 / 1,142

[ Back to top ]