Fターム[5F044LL01]の内容

ボンディング (23,044) | フェイスダウンボンディング (4,630) | 直接ハンダ付け状態 (1,160)

Fターム[5F044LL01]の下位に属するFターム

基板の貫通孔を介してハンダ付け (18)

Fターム[5F044LL01]に分類される特許

161 - 180 / 1,142

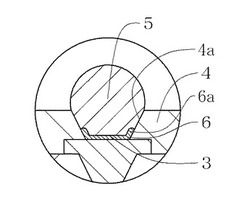

配線基板

【課題】

半導体素子の電極と半導体素子接続パッドとの接続を良好に保ち、半導体素子との電気的接続信頼性が高い配線基板を提供することを課題とする。

【解決手段】

絶縁基板1と、絶縁基板1の表面に形成された配線導体層2と、絶縁基板1および配線導体層2の上に形成されており、配線導体層2の一部を半導体素子接続パッド3として露出させる開口部4aを有するとともに半導体素子接続パッド3周辺の配線導体層2を被覆するソルダーレジスト層4と、半導体素子接続パッド3表面を覆うめっき金属層6とを備えた配線基板10であって、めっき金属層6は、半導体素子接続パッド3の外周部から開口部4aの側壁の途中まで延在する突起部6aを開口部4aの側壁に密着して有している。

(もっと読む)

電子部品の実装方法、電子部品の製造方法および電子部品、電子部品の製造装置

【課題】加熱時に電子部品に反りが発生した場合でも、電子部品の電極をプリント基板の電極に確実に接合することができる電子部品の実装方法、電子部品の製造方法および電子部品、電子部品の製造装置を提供する。

【解決手段】電子部品1は、電子部品1を形成する複数の電極3a〜3eが格子状に配列された基板本体2を備え、複数の電極3a〜3eのうち、基板本体2の反りが大きくなる外側の位置には、所定の高さを有する電極3a及び電極3eを有し、基板本体2の反りが小さくなる中央の位置には、加圧ヘッド4による加圧により外側の電極3a、3eよりも半田ボールの高さが低く潰された電極3b、3c、3dを有する。

(もっと読む)

半導体装置及びその製造方法

【課題】半導体パッケージを配線基板にフリップチップ接合した半導体装置において、接合部での電極間短絡と応力集中を防止し、リワークが容易な構成とする半導体装置及びその製造方法を提供する。

【解決手段】半導体パッケージ11を配線基板21にフリップチップ接合した半導体装置1において、半導体パッケージと配線基板を接合する突起電極30を有し、突起電極は、はんだ電極32と、はんだ電極を被覆する熱収縮モールド31を含む。

(もっと読む)

超音波実装ツール及び電子部品の実装装置

【課題】この発明は電子部品を吸着保持するための吸引孔を超音波振動するホーンに腹の部分に容易に形成できるようにした超音波実装ツールを提供することにある。

【解決手段】ホーン22の一端に設けられホーンを所定方向に振動させる振動子23と、ホーンの振動の振幅が最大となる部分に設けられ下面に半導体チップCを吸着保持する吸引孔31の先端部が開口したツール部25を具備し、吸引孔は、ホーンの振動方向と交差する上下方向に沿って真直ぐに貫通して形成されている。

(もっと読む)

実装構造体

【課題】SMT方式により実装構造体を作製する際、フラックスの熱ダレによるはんだ流動を抑え、はんだボールの発生を抑制する。

【解決手段】実装構造体18は、絶縁基板10上の基板電極11に設けた電極切欠部12と、基板電極11と接合する電子部品電極16を備えた電子部品15からなる。電極切欠部12の位置は、接合のため載置された電子部品15の電子部品電極16と基板電極11とが重なる領域内の、電子部品15の長手軸A−A’上の端点12aと、長手軸A−A’上で電子部品15の外側方向に電子部品電極16と重なる領域外の基板電極11境界上の端点12bとの間である。電極切欠部12の端点12b側は基板電極11を貫通するように設けている。この電極切欠部12により、接合する際、電子部品104下部の空間Sへのフラックスの流動を抑制して、はんだの電子部品104下部への流動を防止できはんだボールの発生を抑制する。

(もっと読む)

半導体装置及びその製造方法

【課題】簡単な製造方法でハンダを用いた接合部の強度を高める。

【解決手段】半導体装置41は、実装基板1の上に電極パッド5を有し、電極パッド5の表面には触媒層10を形成した後に、カーボンナノチューブ15を成長させている。カーボンナノチューブ15は、実装基板1に垂直に多数形成されている。実装基板1に実装される半導体素子31は、基板32の他方の面32Aに形成された電極パッド35にハンダボール36が形成されている。ハンダボール36は、カーボンナノチューブ15が食い込むように実装基板1の電極パッド5に接合される。

(もっと読む)

ボンディング装置及びボンディング方法

【課題】複雑な形状の異形パッドを対象とする場合にあっても、目合わせ処理を十分な精度で行うことができるボンディング装置およびボンディング方法を提供することを目的とする。

【解決手段】チップを基板5に形成されたパッド10にボンディングするボンディング処理において、対象となるパッド10が目視による位置合わせが困難な矩形以外の輪郭形状を有する異形パッドである場合には、認識処理部による自動認識処理が不調のときに実行される目合わせ処理において、認識画像5aと重ね合わせた状態でこの認識画像5aの視認を妨げない特性を有するレファレンスパターン5*を使用し、基板保持部4上の基板5を手動操作で移動させながら、表示画面25a上でパッド画像10aとパッドパターン10*とのパターンマッチングを目視により行い、パッド10の基準位置を検出する。

(もっと読む)

Bi系はんだ接合用の電子部品と基板及び電子部品実装基板

【課題】 Pbを含まないBi系はんだ合金により電子部品と基板を接合する際に、電子部品又は基板の最上層であるNi含有層のNiとBi系はんだ合金のBiとの反応を抑制し、確実な接合が可能な電子部品及び基板を提供する。

【解決の手段】 Pbを含まずBiを80質量%以上含有するBi系はんだ合金を用いて接合する電子部品又は基板において、その電子部品又は基板の最上層であるNi含有層の上に、厚さ0.05〜8.00μmのZnメタライズ層若しくは厚さ0.05〜3.00μmのSnメタライズ層を形成する。好ましくは、Znメタライズ層若しくはSnメタライズ層の上に、Ag、Au、Cuから選ばれる厚さ0.05〜1.00μmの第2のメタライズ層を成形する。

(もっと読む)

電子装置の製造方法

【課題】環境負荷が小さく低コストで、150℃以上の高温下で長時間使用しても接続信頼性を維持できる電子装置の製造方法を提供する。

【解決手段】電子装置のはんだ接続部1において、基板5の電極となるCu層上にNiめっき層3が形成され、はんだボールを構成し、かつ室温から200℃においてCu6Sn5相を含有するSn系はんだ8との間に化合物層2を有する。化合物層2はCu6Sn5相がNiめっき上に析出あるいは移動してバリア層を形成し、界面反応を抑制する。

(もっと読む)

フリップチップ型半導体裏面用フィルム、ダイシングテープ一体型半導体裏面用フィルム、半導体装置の製造方法、及び、フリップチップ型半導体装置

【課題】被着体上にフリップチップ接続された半導体素子に反りが発生するのを抑制又は防止することが可能なフリップチップ型半導体裏面用フィルム、及びダイシングテープ一体型半導体裏面用フィルムを提供する。

【解決手段】被着体上にフリップチップ接続された半導体素子の裏面に形成するためのフリップチップ型半導体裏面用フィルムであって、熱硬化前のフリップチップ型半導体裏面用フィルムの全体積に対する、熱硬化による収縮量が2体積%以上30体積%以下であるフリップチップ型半導体裏面用フィルム。

(もっと読む)

ボンディング方法

【課題】工程の簡略化を達成可能なボンディング方法を提供する。

【解決手段】表面に複数のバンプ2を有するデバイスDをリードフレーム28にボンディングするボンディング方法であって、表面に複数のバンプを有するデバイスが複数形成された半導体ウエーハの裏面に粘着シートTを貼着するステップと、粘着シートが貼着された半導体ウエーハを個々のデバイスへと分割して、粘着シート上に複数のデバイスが配設された形態にするステップと、粘着シート上に配設されたデバイスのバンプと、リードフレームのバンプに対応する電極30とを対面させて、粘着シート側からバンプを電極に押し付けるとともに外的刺激を付与することで、リードフレームにデバイスのバンプを接続させるステップと、を具備したことを特徴とする。

(もっと読む)

バンプ形成方法及び半導体装置の製造方法

【課題】弾力性を有するバンプを安価に効率よく形成することにより、バンプを用いた実装に際して、あるいは製品としての使用に際して負荷される熱応力を軽減することができ、しかも狭ピッチ化に対応することができるバンプ形成方法、及び、そのバンプを使用することで信頼性に優れたフリップチップ実装が容易にできる半導体装置の製造方法を提供する。

【解決手段】基材の金属電極上にノズルから液滴を吐出してバンプを形成するバンプ形成方法であって、樹脂を含む第1の液滴をノズルから吐出して、前記金属電極の一部に樹脂突起部を設ける工程と、分散剤と金属ナノ粒子とを含む第2の液滴をノズルから吐出して、前記金属電極の残部と前記樹脂突起部とを前記金属ナノ粒子で覆う工程と、を含むことを特徴とするバンプ形成方法である。

(もっと読む)

半導体装置の製造方法

【課題】パッシベーション膜に形成された開口部から露出するボンディングパッドの表面に導電性部材を接続する半導体装置において、パッシベーション膜に発生するクラックを抑制することができる技術を提供する。

【解決手段】電極層ELの一端とパッドPADの一端との間の平面的な距離(L2)を、電極層ELの一端と開口部OPの一端との間の平面的な距離(L1)よりも大きくする。これにより、ワイヤWの接続位置が電極層ELの端部側にずれる場合であっても、電極層ELの一端とパッドPADの一端との間の平面的な距離(L2)が大きくなっているため、電極層ELの段差部にワイヤWが接続することに起因した応力がパッドPADの端部にまで伝わることを抑制できる。

(もっと読む)

LEDパッケージおよびLEDパッケージ実装構造体

【課題】はんだ疲労寿命の向上を実現し、低コストで信頼性の高いLEDパッケージ実装構造体を提供する。

【解決手段】LEDパッケージ10は、回路基板20との実装面に対して垂直な方向に発光面11を持ち、パッケージの側面あるいは側面と底面に接続用端子部121、122、131,132を備え、該接続用端子部を介して回路基板とはんだ接続される。さらに、LEDパッケージ中心側におけるLEDパッケージ本体底面の電極端と回路基板の部品搭載用パッド端の相対位置関係を規定することによりはんだの形状を適正化する。

(もっと読む)

半導体装置の製造方法

【課題】半田バンプのオープン不良を防止することができる半導体装置の製造方法を得る。

【解決手段】配線基板上に配線を形成し、配線基板上をソルダレジストで覆い、配線を露出させるようにソルダレジストに開口を形成する。配線基板の配線と半導体チップの電極とを半田バンプを介して接続させることで、配線基板上に半導体チップをフリップチップ接続させる。半田バンプの半田の量を、ソルダレジストの開口の角と電極に内接する球の体積よりも小さくする。

(もっと読む)

プリント配線板ユニット、電子機器およびプリント配線板ユニットの作製方法

【課題】リペア性を確保しつつ電子部品をプリント配線板に実装するとき、プリント配線板への接合の補強を十分に行なう作製方法を提供する。

【解決手段】プリント配線板ユニットは、プリント配線板と、前記プリント配線板の所定位置にはんだ接合により電気的に接続され、かつ、接着層により前記プリント配線板と接合された電子部品と、を有する。前記プリント配線板と前記電子部品との間の接着層の一部の領域が、第1補強用樹脂層30を前記プリント配線の側に、前記第1補強用樹脂層30に比べて接着強度が高い第2補強用樹脂層32を前記電子部品の側に備える多層積層領域34である。

(もっと読む)

電子デバイス

【課題】半田の接合前の形状に影響されずに半田接合を良好にするための電子デバイスを提供する。

【解決手段】第1の素子1と、第1の素子1の上に形成されて少なくとも露出面が絶縁材から形成される柱状突起5と、柱状突起5の周囲に形成される複数の第1電極3とを有し、柱状突起5は、第1の素子1に対向して配置される第2の素子11の上に形成された複数の突起電極14の間に嵌め込まれ、第1電極3と突起電極14は半田層4、15を介して接続される。

(もっと読む)

半導体装置の構造および製造方法

【課題】挟ピッチかつ高い接続信頼性を確保した簡易な構造の半導体装置、および製造方法を提供する。

【解決手段】半導体素子1の電極端子1b上に突起状電極1aを形成する。突起状電極1aよりも大きくし、位置を合わせた転写用の金型4に、粘着層5を供給し半田粒子3を付与する。金型4と半導体素子1の対向する位置を合わせ、加熱・加圧して半田粒子3を突起状電極1a上に付与、金型4を引き剥がして半導体素子1を個片化する。半導体素子1の突起状電極1aに対向して回路基板2の電極端子2aの位置を合わせて、加熱、荷重し半導体素子1を回路基板2上へ搭載する。半導体素子1の端部の回路基板2との距離が最も大きな電極同士でも、微細半田が鼓状に伸びて接合し平行度の悪化を吸収する。端部電極の熱応力集中を微小半田接合体(半田接合部3c)が受けて、電極直下の脆弱な絶縁膜の熱応力を低減して剥離や亀裂を防ぎ、高い接続信頼性を確保する。

(もっと読む)

半導体装置及びその製造方法

【課題】半導体装置において、各バンプの先端位置、即ち、各バンプの突出量がばらついていても、実装基板に接合した場合に、全てのバンプにおいて十分な接合強度が得られるようにする。

【解決手段】半導体装置を、半導体素子3と、半導体素子3の表面側に位置し、半導体素子3の裏面3Aとの間の距離が第1の距離である第1バンプ形成面4(4E)上に形成された第1バンプ1(1E)と、半導体素子3の表面側に位置し、半導体素子3の裏面3Aとの間の距離が第1の距離よりも長い第2の距離である第2バンプ形成面4(4A)上に形成され、第1バンプ1(1E)よりも径が大きい第2バンプ1(1A)とを備えるものとする。

(もっと読む)

布製半導体素子のパッケージ及びその製造方法

【課題】着用した際の異物感を最小限に抑えると共に、生産性が向上した布製半導体素子のパッケージ、その布製半導体素子のパッケージの製造方法を提供する。

【解決手段】布製半導体素子のパッケージは、織布と、前記織布上に導電材をパターニングして形成された第1リード部と、を有する布製印刷回路基板と、前記布製印刷回路基板のリード部に接続された電極部を有する半導体素子と、前記布製印刷回路基板と、前記半導体素子とを密封する成形部(molding)と、を含む。前記第1リード部は、前記第1リード部の端部において別の布製半導体素子と電気的に接続された導電性繊維によって前記織布とともに縫合されることにより、あるいは、前記第1リード部は、前記第1リード部の端部において別の布製半導体素子と電気的に接続された布製印刷回路基板の第2リード部と前記織布と共に縫合されることにより、前記別の布製半導体素子と電気的に接続されている。

(もっと読む)

161 - 180 / 1,142

[ Back to top ]