Fターム[5F044LL04]の内容

ボンディング (23,044) | フェイスダウンボンディング (4,630) | ハンダ付け方法 (478)

Fターム[5F044LL04]の下位に属するFターム

加熱方法 (145)

Fターム[5F044LL04]に分類される特許

1 - 20 / 333

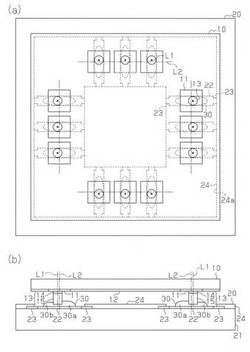

半導体装置の製造方法、半導体装置、及び半導体素子

【課題】はんだによる短絡不良を低減すること。

【解決手段】半導体素子10の一主面には複数の電極パッド11が、半導体素子10の外周に沿って矩形枠状に配列されている。各電極パッド11には、柱状の電極端子13が立設されている。各々の電極端子13の中心軸L1は、電極パッド11の中心から、電極パッド11の配列方向と直交する方向に沿って半導体素子10の外側にずれた位置に形成されている。半導体素子10が実装される配線基板20には、半導体素子10の電極パッド11と対応する複数の接続パッド22が形成されている。各接続パッド22の中心L2は、半導体素子10の電極パッド11の中心と略一致する。また、各接続パッド22は、配列方向と直交する方向、即ち半導体素子10の外周と直交する方向に沿って延びる矩形状に形成されている。電極端子13は接続パッド22にはんだ30により電気的に接続される。

(もっと読む)

リフローフィルム、はんだバンプ形成方法、はんだ接合の形成方法及び半導体装置

【課題】はんだ成分を自己組織化により基板の電極上に偏在させることにより、保存性、運搬性、及び使用時のハンドリング性に優れ、電極上に選択的にはんだバンプ又ははんだ接合を形成できるリフローフィルムを提供し、更にこれを用いたはんだバンプ又ははんだ接合の簡便な形成方法、これにより形成されたボイドが少なく高さばらつきが少ないはんだバンプ及びはんだバンプ付き基板を提供する。

【解決手段】ポリビニルアルコールと、分子量500以下の水に溶解または分散する化合物と、分散したはんだ粒子とを含むフィルム21であって、前記分子量500以下の化合物はポリビニルアルコール100質量部に対して20〜300質量部であるリフローフィルム、および基板10の電極12面側に前記リフローフィルムを載置する工程、さらに平板12を載置する工程、加熱する工程、及び前記リフローフィルムを溶解除去する工程を含むはんだバンプ形成方法。

(もっと読む)

リフローフィルム、はんだバンプ形成方法、はんだ接合の形成方法及び半導体装置

【課題】はんだ成分を自己組織化により基板の電極上に偏在させることにより、保存性、運搬性、及び使用時のハンドリング性に優れ、電極のみに対して選択的にはんだバンプ又ははんだ接合を形成することができるリフローフィルムを提供し、さらにこれを用いたはんだバンプ又ははんだ接合の簡便な形成方法、これにより形成されたボイドが少なく高さばらつきが少ないはんだバンプ及びはんだバンプ付き基板を提供する。

【解決手段】溶媒に溶解可能な熱可塑性樹脂と、はんだ粒子とを含むフィルムであって、前記はんだ粒子は前記フィルム中に分散した状態であることを特徴とするリフローフィルム、および(ア)基板の電極面側に前記リフローフィルムを載置する工程、(イ)さらに平板を載置して固定する工程、(ウ)加熱する工程、及び(エ)前記リフローフィルムを溶解除去する工程を含むはんだバンプ形成方法。

(もっと読む)

はんだバンプのセルフアライメントに利用するスタッドの作成

【課題】 3次元実装のプロセスに親和性のある、高精度のアライメントを提供すること。

【解決手段】 複数のシリコンチップ間においてはんだバンプが溶融した場合に、複数のシリコンチップ同士の横方向の相対的な動きを規制する複数のスタッド(40)の組合わせであって、複数のシリコンチップ間に配置される複数のはんだバンプ(10)のピッチに従い、これらの横方向の位置をリファレンスにして横方向位置が決定されていて、複数のシリコンチップが横方向に相対的に移動した場合に相対的に動きが規制されて、複数のシリコンチップのそれぞれに設定された複数のはんだバンプ同士の横方向位置が(高さ方向において)整列するように、一方のシリコンチップおよび他方のシリコンチップにおいて複数のスタッド(40)が設けられる。

(もっと読む)

無線装置およびその製造方法

【課題】ICチップのプロセスばらつきによって高周波特性がばらついた場合でも、回路特性を最適化できるICチップを基板にフリップチップ実装する無線装置を提供する。

【解決手段】無線装置は、マイクロ波、ミリ波帯の電力増幅器用高周波ICチップ100、バンプ102、入力端子103、出力端子104、基板105、アンダーフィル106、プロセスばらつき検出部110を有する。プロセスばらつき検出部は、プロセスばらつきによる回路特性の変動量をモニタし、モニタされた回路特性の変動量を用いて、算出されたパラーメータを有するアンダーフィル106が、基板105とミリ波帯の電力増幅器用高周波ICチップ100との間に充填されることで、プロセスばらつき及びアンダーフィルの影響があっても、所望の回路特性が得られる無線装置を提供できる。

(もっと読む)

半導体装置の製造方法、半導体装置、接着フィルム、及び、接着フィルムの貼り合わせ方法

【課題】接着フィルムと半導体ウエハとを貼り合わせる際のボイドを抑制し、高い接合信頼性を実現することのできる半導体装置の製造方法を提供する。

【解決手段】接着フィルムの接着剤層と半導体ウエハとを1cm以下のクリアランスで対向させる工程と、50〜100℃、10000Pa以下の加熱真空下、前記接着フィルムの接着剤層と前記半導体ウエハとを0.1〜1MPaの圧力で貼り合わせる工程と、接着剤層付きの半導体ウエハを得る工程と、前記接着剤層付きの半導体ウエハを接着剤層付きの半導体チップに個片化する工程と、前記接着剤層付きの半導体チップを実装する工程とを有し、前記接着フィルムの接着剤層は、半導体ウエハに貼り合わされる側の表面のプローブタック法で測定したタック値が、貼り合わせ温度において100gf/5mmφ以上である半導体装置の製造方法。

(もっと読む)

半導体装置、電子装置、半導体装置の製造方法

【課題】低温で接合でき、接合後にはんだバンプの溶融温度を上昇させることができる半導体装置の製造方法を提供する。

【解決手段】第1の接続部材11の第1の主面11Aに第1の接続パッド11aを形成する工程と、半導体チップ21の回路形成面21Aに、第2の接続パッド21aを形成する工程と、第1の接続部材の上に半導体チップを、第1の接続パッドが前記第2の接続パッドに、Sn−Bi合金よりなるはんだバンプ31Aを介してコンタクトするように載置する工程と、はんだバンプをリフローさせ、前記第1の接続パッドと前記第2の接続パッドとを接合する工程と、前記接合工程の後、前記第1および第2の接続パッドの一方をアノード、他方をカソードとして、前記アノードから前記カソードへと直流電流を通電し、前記はんだバンプ中のBiを前記アノードの側に濃集させ、前記はんだバンプ中のSnを前記カソードの側に濃集させる工程と、を含む。

(もっと読む)

ハンダ接続シートおよびそれを用いた電子部品の実装方法

【課題】電子部品に形成された電極端子間距離が狭い場合であっても、隣接する電極端子間を短絡させることなく、しかも容易且つ確実に、回路基板の接続用端子に電子部品の各電極端子を接続させることが可能なハンダ接続シートと、それを用いた電子部品の実装方法を提供すること。

【解決手段】織布または不織布で構成してあり、表裏面を貫通する複数の貫通孔6が所定パターンで形成してあるシート基材4と、貫通孔6の内部に保持され、予めボール状に成形されたハンダ部材8と、を有するハンダ接続シート2である。

(もっと読む)

半導体チップを3次元積層アセンブリへと多段に形成していく、はんだ接合プロセス

【課題】 エレクトロマイグレーション(EM)の耐性があり、ハイエンドの半導体チップにも採用できるようなプロセスとして、半導体チップを3次元積層アセンブリへと多段に形成していく、はんだ接合プロセスの提供。

【解決手段】

電気接合部に異なる融点をもつ2種のはんだを積層させて構成しておき、3次元積層アセンブリを作成するにあたって、チップ積層時(一次)は低温はんだのみを溶融して積層接合して、アンダーフィルによって封止する。マザーボードへの積層時(二次)は高温はんだを溶融させる。マザーボードへの二次実装時においてもそのギャップとバンプ形状を保持することができる。

(もっと読む)

アンダーフィルとの間で化学的に硬化物を形成する無洗浄フラックス

【課題】 無溶剤の熱可塑性残渣を生成し、その熱可塑性残渣がアンダーフィル成分と反応して熱硬化性樹脂を形成する無洗浄フラックス、を提供すること。

【解決手段】 フラックス活性剤としてジカルボン酸、樹脂成分として平均官能基数が約2.0を有するエポキシのプレポリマー、および粘度調整剤として沸点260度以下の溶剤を含む無洗浄フラックスが、リフロー時にはんだの酸化膜を除去するとともに、ガラス転移温度が100℃以下でアンダーフィル塗布時に液状となる熱可塑性エポキシ硬化物を形成する。粘度調整剤としての溶剤は、リフロー中にそのほとんど全量が揮発し、リフロー後、洗浄することなく、アンダーフィルを塗布する際、その硬化物はアンダーフィルと相溶してアンダーフィルに含まれる硬化剤と反応し、アンダーフィルとともに3次元架橋構造を形成できる。

(もっと読む)

ウエハの接合方法及び接合部の構造

【課題】ウエハの接合部どうしをAuSn共晶接合する工程において、AuSnによる密着層の劣化を防ぐこと。

【解決手段】ウエハ1の表面に密着層4を形成し、密着層4の上方にAuSnとの濡れ性の悪い材料からなる拡散防止層7を積層する。さらに、拡散防止層7の縁よりも引っ込めて拡散防止層7の表面に接着層8を形成し、ウエハ1の表面に接合部3を形成する。一方、ウエハ11の下面に接合部13を設け、接合部13の下にAuSnハンダ層19を設ける。ウエハ1とウエハ11とを向かい合わせ、AuSnハンダ層19を溶融させて接合部3と接合部13をAuSnハンダ22によってAuSn共晶接合させる。

(もっと読む)

電子部品実装装置および電子部品実装装置におけるペースト転写方法

【課題】塗膜形成ステージにおけるペーストの残量管理を適正に行って、ペーストの転写品質を安定させることができる電子部品実装装置および電子部品実装装置におけるペースト転写方法を提供することを目的とする。

【解決手段】検出方向を塗膜形成面24aに向けて配設された光センサ14によってフラックス25を検出することにより、塗膜形成ステージ24へのフラックス25の補給の要否を判断するペースト残量検出手段を備え、補給要否の判断に際し、光センサ14によるフラックス25からの反射光の受光量が、残量が適正である場合の受光量の上限値を示す第1の基準値L1以上であって、かつ残量が過多である場合の受光量の下限値を示す第2の基準値L2以下の場合に、補給の必要有りと判断する。

(もっと読む)

リフロー前処理装置およびリフロー前処理方法

【課題】はんだ付け対象のうちのはんだバンプが形成される表面にスズが付着することを防止すること。

【解決手段】水素ラジカル発生装置3と、浮遊物質捕獲用フィルター5とを備えている。水素ラジカル発生装置3は、はんだ付け対象10に配置されたはんだに水素ラジカルを照射する。浮遊物質捕獲用フィルター5は、その水素ラジカルが浮遊物質捕獲用フィルター5を通り抜けた後にそのはんだに照射されるように、配置される。そのはんだは、水素ラジカルに照射されたときに、表面に形成された酸化膜が除去され、そのはんだから遊離した浮遊物質を放出する。このようなリフロー処理装置は、その浮遊物質を浮遊物質捕獲用フィルター5が捕獲することにより、はんだ付け対象10の表面にその浮遊物質が堆積することを防止することができる。

(もっと読む)

三次元実装装置

【課題】半導体デバイスの製造のスループットをさらに向上できるとともに、製造される半導体デバイスの品質の低下を防止できる三次元実装装置を提供する。

【解決手段】三次元実装装置11において、搬送トレイ16は配置面16aaをそれぞれ含む8つの内側トレイ16aを有し且つ各配置面16aaに配置された8つの積層チップ21を搬送し、チャンバ27は全ての内側トレイ16aを収容し、複数の下部ステージ28の各々はチャンバ27内において複数の内側トレイ16aの各々を載置し、複数のチャック29の各々は、チャンバ27内において、配置面16aaに配置された積層チップ21の各々と一対一で対応して配設され、各下部ステージ28及び各複数のチャック29が各下部ステージ28及び各複数のチャック29の間を詰めるように移動する。

(もっと読む)

半導体装置

【課題】フリップチップ実装の半導体装置において、パッケージ外部の設計を変更せずに、特定の端子の電位を変更できる半導体装置を提供する。

【解決手段】本発明の半導体装置は、外部端子にバンプを備えるICチップと、前記ICチップを搭載するパッケージとを備え、前記パッケージは、前記外部端子に第1の信号又は第2の信号を印加するインナーリード部を備える。前記インナーリード部は、前記ICチップの搭載位置により、前記外部端子に印加する信号を、前記第1の信号又は前記第2の信号に変更可能なインナーリードのパターンを有する。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】半田ペースト溶融時の半導体チップの傾きを抑制し、半導体チップと電極板との接合の信頼性を向上できる半導体装置及び半導体装置の製造方法を提供すること。

【解決手段】実施形態に係る半導体装置は、電極を有する裏面電極板と、裏面電極板に半田により接合された半導体チップと、電極が露出した状態で、半導体チップを封止する封止材と、を備え、裏面電極板と半導体チップとの接合面に、1以上の第1のバンプが形成されていることを特徴とする。

(もっと読む)

半導体装置、半導体装置の再生方法、および半導体装置の製造方法

【課題】回路基板から半導体パッケージを取り外した後、半導体パッケージの再取り付けが容易である半導体装置を提供する。

【解決手段】半導体装置は、回路基板と、半導体パッケージと、回路基板と前記半導体パッケージとを電気的に接続するはんだ接合部と、回路基板と半導体パッケージとの間に配置され、はんだ接合部が通る穴を有し、穴は、穴の最も狭い部分に対し半導体パッケージ側に配置された部分のはんだ接合部よりも細く形成されている板状部材とを有する。

(もっと読む)

電子機器、電子部品、および基板アセンブリの製造方法

【課題】電子部品を回路基板により精度良く実装することが可能な電子機器、電子部品、および基板アセンブリの製造方法を得る。

【解決手段】実施形態にかかる電子機器では、接合部は、第一導体部と第二導体部との間に介在し、第一導体部と第二導体部とを電気的に接続した。封止部は、少なくとも第一面と第二面との間に介在し、酸化膜を還元する還元剤を含み、接合部を封止した。位置決め部は、第一面から突出し、その突出側の端部が第一面と第二面との間に位置され、第二面に封止部が塗布された電子部品が第一面に載せられる際に当該第一面に沿って移動しようとした場合にあっても封止部と接触することにより電子部品が第一導体部と第二導体部とが対向した位置から外れるのを抑制する。

(もっと読む)

半導体装置、半導体装置の製造方法及び電子機器

【課題】低いリフロー温度で信頼性良く接合できる接合部を備えた半導体装置、半導体装置の製造方法及び電子機器を提供する。

【解決手段】素子11上に形成された第1電極12と、基板21上に形成された第2電極22との上に、それぞれSn-Bi又はSn-Inを含むはんだ層13、23を形成し、これらのはんだ層13、23の間にSn-Ga合金ボール14を、はんだ層13、23の融点よりも高く、且つSn-Ga合金ボール14の融点よりも低い温度でリフロー接合する。リフロー接合の際にはんだ層13、23とSn-Ga合金ボール14との界面にSn-Bi-Ga合金層15又はSn-In-Ga合金層が形成され、Sn-Ga合金ボール14からのGaを含む融液の拡散が阻止される。

(もっと読む)

半導体装置およびその製造方法並びに電子装置

【課題】素子と基板との接合の際の熱処理に起因した熱応力の緩和をバンプの中央部で行なうこと。

【解決手段】素子10と、基板20と、第1導電体32と、前記第1導電体上に形成された第2導電体34と、前記第2導電体上に形成された第3導電体36と、前記第3導電体上に形成された第4導電体38と、を有し、前記第1導電体と前記第4導電体のいずれか一方が前記素子に接合され、前記第1導電体と前記第4導電体の他方が前記基板に接合され、前記素子と前記基板とを電気的に接続するバンプ30と、を具備し、前記第1導電体および前記第3導電体は、前記第2導電体および前記第4導電体より融点が高く、前記第4導電体は前記第2導電体より融点が高い半導体装置。

(もっと読む)

1 - 20 / 333

[ Back to top ]