Fターム[5F044LL17]の内容

ボンディング (23,044) | フェイスダウンボンディング (4,630) | 基板とチップ間のスペーサー (91)

Fターム[5F044LL17]に分類される特許

1 - 20 / 91

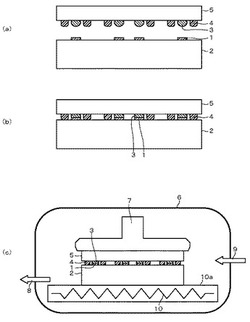

半導体装置の製造方法および半導体装置の製造装置

【課題】はんだバンプ表面の酸化膜を良好に除去しつつ、半導体素子の反り等を防止し、はんだバンプの接続性向上を可能にした半導体装置の製造方法を提供する。

【解決手段】実施形態によれば、第1の半導体チップ2と第2の半導体チップ5との間の隙間をスペーサ突起4により保持しつつ、第2の半導体チップ5のはんだバンプ3と第1の半導体チップ2の金属電極1とを仮固定する。次いで、仮固定された積層体を、荷重を負荷しながらギ酸等のカルボン酸ガス雰囲気で加熱し、はんだバンプ3表面の酸化膜を還元・除去しつつはんだバンプ3の接合を行う。

(もっと読む)

半導体装置の製造方法

【課題】より簡便に樹脂突起に形成された凹部の深さ(樹脂の除去量)を検査することができる半導体基板の製造方法を提供する。

【解決手段】本発明に係る半導体装置の製造方法は、第1の面を有する半導体基板と、前記第1の面に位置する第1電極及び第2電極と、前記第1の面に位置する第1樹脂突起及び第2樹脂突起と、前記第1樹脂突起の第1の部分を覆い、前記第1電極に接続された第1配線と、前記第1樹脂突起の第2の部分を覆い、前記第2電極に接続された第2配線と、を有する構造体を用意する第1工程と、前記第1樹脂突起の前記第1の部分と前記第2の部分の間の第3の部分の一部と、前記第2樹脂突起の少なくとも一部と、を同時にエッチングする第2工程と、前記第2工程後の前記第2樹脂突起の形状から、前記第2工程のエッチングにおける前記第3の部分の除去量が適正であるかを判断する第3工程と、を含む。

(もっと読む)

半導体装置、半導体装置の製造方法及び電子機器

【課題】低いリフロー温度で信頼性良く接合できる接合部を備えた半導体装置、半導体装置の製造方法及び電子機器を提供する。

【解決手段】素子11上に形成された第1電極12と、基板21上に形成された第2電極22との上に、それぞれSn-Bi又はSn-Inを含むはんだ層13、23を形成し、これらのはんだ層13、23の間にSn-Ga合金ボール14を、はんだ層13、23の融点よりも高く、且つSn-Ga合金ボール14の融点よりも低い温度でリフロー接合する。リフロー接合の際にはんだ層13、23とSn-Ga合金ボール14との界面にSn-Bi-Ga合金層15又はSn-In-Ga合金層が形成され、Sn-Ga合金ボール14からのGaを含む融液の拡散が阻止される。

(もっと読む)

回路基板、半導体パワーモジュール、製造方法

【課題】半導体素子から多層基板への熱拡散性能の向上、および、多層基板と半導体素子との接合強度の向上。

【解決手段】半導体パワーモジュール30は、セラミックス多層基板300と、接合層310と、半導体素子330を備える。接合層310は、セラミックス多層基板100側が平面状に形成されている薄膜層である。接合層310の絶縁接合部312は、半導体素子330側の端部からセラミックス多層基板300側の端部に向けて先細な形状に形成されている。半導体素子130の実装時、半導体素子330の突状部335は窪み部316内に収められ、接合層310の導電接合部311と導通する。こうすれば、半導体素子330と接合層との接合面積を広く接合でき、多層基板と半導体素子との接合強度、絶縁性能を確保しつつ、半導体素子から多層基板への熱拡散性能を向上できる。

(もっと読む)

半導体装置とその製造方法

【課題】上下の半導体チップ間の隙間を維持しつつ、アンダーフィル樹脂の充填前における半導体チップ間の接続強度を高めることを可能にした積層型半導体装置を提供する。

【解決手段】実施形態の半導体装置1は、第1の半導体チップ2と、第1の半導体チップ2上に積層された第2の半導体チップ3とを具備する。第1および第2の半導体チップ2、3は、バンプ接続体6を介して電気的に接続されている。第1および第2の半導体チップ2、3の少なくとも一方には、ストッパ用突起7と接着用突起8とが設けられている。ストッパ用突起7は、第1および第2の半導体チップ2、3の他方に非接着状態で接触している。接着用突起8は、第1および第2の半導体チップ2、3に接着されている。

(もっと読む)

半導体パッケージ

【課題】半導体チップと配線基板との接続信頼性が高い半導体パッケージを提供すること。

【解決手段】本半導体パッケージは、複数の電極パッドを有する半導体チップと、前記半導体チップを搭載する、複数の電極パッドを有する配線基板と、を有し、前記半導体チップの複数の電極パッドは、第1電極パッドと、前記第1電極パッドよりも外周側に配置された第2電極パッドと、を含み、前記配線基板の複数の電極パッドは、第3電極パッドと、前記第3電極パッドよりも外周側に配置された第4電極パッドと、を含み、前記第1電極パッドと前記第3電極パッドとは、接合部を介して接続されており、前記第2電極パッドと前記第4電極パッドとは、ピンを含む接合部を介して接続されている。

(もっと読む)

基板貼り合わせ方法

【課題】搬送中に、位置合わせされた基板と基板との相対位置がずれるといった課題がある。

【解決手段】基板貼り合せ方法は、仮接合部において、複数の基板を重ね合わせて複数の対向面および側面の少なくとも一方の一部を仮接合部材によって接合する仮接合段階と、前記仮接合段階で仮接合された前記複数の基板を、本接合部へ搬送する搬送段階と、前記本接合部において、前記仮接合段階で仮接合された前記複数の基板を本接合部材によって本接合する本接合段階とを備える。

(もっと読む)

半導体装置のプリント配線板への固定のためのシステムおよび方法

【課題】ボールグリッドアレイのプリント配線板への固定のためのシステムおよび方法を提供する。

【解決手段】ボールグリッドアレイ200は、1つ以上の巻からなるスプリング216に取り付けられるように形成される1つ以上のボール226からなる。加えて、スプリングを整合および分離するように形成されるスペーサープレート208、228、はんだをプリント配線板上に整合するように形成されるはんだ補助材236、およびスプリングを介してボールグリッドアレイに取り付けられる導電性パッド234とともに形成されるプリント配線板230を設ける。

(もっと読む)

チップパッケージとその製造方法

【課題】チップパッケージとその製造方法を提供する。

【解決手段】本発明の実施例は、チップパッケージの製造方法を提供する。複数のスクライブラインにより隔てられる複数のデバイス領域を有する半導体ウェハを提供する工程と、パッケージ基板を半導体ウェハに接合し、スペーサ層をパッケージ基板と半導体ウェハの間に設置して、スペーサ層は、それぞれデバイス領域を露出する複数のキャビティを区画し、半導体ウェハの外縁に隣接する複数の貫通孔を有する工程と、貫通孔中に、接着材料を充填し、スペーサ層は粘性を有し、材料は接着材料と異なる工程と、スクライブラインに沿って半導体ウェハ、パッケージ基板とスペーサ層をダイスして、互いに分離した複数のチップパッケージを形成する工程と、を含む。

(もっと読む)

電子回路、及び、電子回路の製造方法

【課題】高周波信号の信号処理を行う集積回路基板と配線基板とが簡易的かつ高精度に所定距離離間するようにしつつ、集積回路基板の基板表面に形成されたバンプと、集積回路基板の電極端子とを接合することが可能な電子回路を提供する。

【解決手段】波長がミリメートル単位以下である高周波信号の信号処理を行う信号処理回路を有し、基板表面21aに設けられた第1の電極端子22上にバンプ23が形成された集積回路基板21と、集積回路基板21に形成されたバンプ23と接合される第2の電極端子12が形成された配線基板11とを備え、配線基板11には、集積回路基板21と所定距離離間させる絶縁性の樹脂スペーサ13aが、集積回路基板21の信号処理回路の回路パターンに重畳しない位置であって、配線基板11の基板表面11aの同一直線上とならない3つ以上の位置に形成されている。

(もっと読む)

半導体素子およびフリップチップ相互接続構造を形成する方法

【課題】半導体素子を作製する方法を提供する。

【解決手段】半導体ダイの能動表面上に形成された複数のバンプを有する、半導体ダイを提供するステップと、基板を提供するステップと、前記基板上に相互接続部位を伴う複数の伝導性トレースを形成するステップであって、前記バンプは、前記相互接続部位よりも幅広い、ステップと、前記接続部位から離れた前記基板の領域上にマスキング層を形成するステップと、前記バンプが前記相互接続部位の頂面および側面を覆うように、前記バンプを前記相互接続部位に接着するステップと、前記半導体ダイと基板との間で前記バンプの周囲に封入材を堆積させるステップと、を含む、半導体素子を作製する方法。

(もっと読む)

フリップチップボンデッドパッケージ

【課題】微細ピッチ技術に適用可能なフリップチップボンデッドパッケージを提供する。

【解決手段】2列に、かつ互いにジグザグに配列されるボンディングパッドを有する半導体チップ10aと、半導体チップ10a上の、隣接する3つのボンディングパッド毎に3つのパッド間の領域及びその3つのパッドのそれぞれの一部を覆うように形成された絶縁ポスト50aと、絶縁ポスト50aによって覆われていないボンディングパッドの部分及びこれに隣接した絶縁ポスト50aの部分上に形成された信号接続金属部材52aと、半導体チップ10aが絶縁ポスト50a及び信号接続金属部材52aによってフリップチップボンディングされ、第1面に電極を有し、第2面にボールランドを有する基板と、半導体チップ10aと基板との間の空間をアンダーフィルする埋込材と、各ボールランド上に付着されたソルダボールとを備える。

(もっと読む)

電子部品装置およびその製造方法

【課題】実装基板およびこれに実装される電子部品のリフロー時の反りを抑える。

【解決手段】実装基板4と電子部品3との間にスペーサー1を配置するとともに、スペーサーの配置位置とは異なる位置に、実装基板と電子部品とを接合する接着剤2を配置した。実装基板と電子部品の少なくとも一方に、はんだボール、スペーサーを配置するとともに、スペーサーの配置位置とは異なる位置に熱硬化型接着剤を塗布し、その後、実装基板上に電子部品を搭載し、加熱処理により、熱硬化型接着剤を硬化させた後に、はんだボールを溶融させる。

(もっと読む)

電子部品の実装構造体及びその製造方法

【課題】半田付けと補強樹脂の熱硬化を同一の加熱工程で行うに際しての、補強樹脂の硬化時の熱収縮の影響を小さく抑えることができる電子部品の実装構造体を提供する。

【解決手段】プリント基板2と、プリント基板2上に半田ボール3を介して実装された平面形状が正方形状の電子部品4と、プリント基板2と電子部品4との両方に跨って塗布形成された補強樹脂5とを備えた電子部品の実装構造体1である。電子部品4の上面の法線方向から見た場合に、補強樹脂5は、電子部品4の上面の各角部を起点として各辺に沿って時計回りに隣の角部に到達しない長さで塗布形成されている。

(もっと読む)

回路基板ユニット、回路基板ユニットの製造方法、及び電子装置

【課題】パッケージ基板の回路基板に対する実装高さをより大きくすることによりパッケージ基板と回路基板との間の接続信頼性を高めるに当り、所望の実装高さを容易に達成することができる手段を提供する。

【解決手段】熱膨張率が異なる第1基板27と第2基板24とが半田材28により加熱接合されて形成される回路基板ユニットであって、第1基板27と第2基板24との間に配置され、熱膨張性材11と熱硬化性材12から形成されるスペーサ10を備え、熱硬化性材12の硬化温度は前記半田材28の融点よりも高い。

(もっと読む)

接続構造体の製造方法及び接続構造体並びに接続方法

【課題】ショートの発生を抑制し、良好な導通状態を実現する接続方法及び接続構造体並びに接続構造体の製造方法を提供する。

【解決手段】ガラス基板1の接続面11には、導電性粒子の移動方向を制御するガイド面部131,132を備えた誘導板13が形成されている。誘導板13は、隣接する配線電極12間領域を介して対峙する領域の一方に立設される。ガイド面部131,132は、誘導板13の立設方向と直交する側面方向が配線電極12を向く。熱加圧によって異方性導電フィルムを介してガラス基板1とICチップとを圧着接続し、配線電極12とバンプとを異方性導電接続させる。

(もっと読む)

LSIパッケージ及びコア入りはんだバンプ並びにLSIパッケージ実装方法

【課題】CSP,BGA等のようなはんだバンプを有するLSIパッケージをプリント基板に実装する際、LSIパッケージが熱により反り返っても、良好なはんだ接続部を形成する。

【解決手段】LSIパッケージ1のパッド4には、コア部31及びコーティング部32からなるコア入りはんだバンプ3が配置されている。コア部31及びコーティング部32は組成の異なるはんだ合金から構成され、コーティング部32の方が融点が低くなっている。従って、熱処理を開始すると、先ず、LSIパッケージ1の反り返りが小さな段階で、コーティング部32が溶融し、コア部31及びはんだペースト7に濡れた状態となる。その後、温度が上昇して反り返りが大きくなっても、コア部31とはんだペースト7とは、溶融したコーティング部32によって接続された状態が保たれる。従って、コア部31,はんだペースト7の溶融温度となると、それらが1つに凝集し、良好なはんだ接続部が形成される。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】半導体チップを挟む2枚の配線基板の間隔を一定に保持するとともに、該2枚の配線基板の接合位置を高精度に決めることのできる半導体装置及び半導体装置及び半導体装置の製造方法を提供する。

【解決手段】半導体チップが実装された第1配線基板10、及び第2の配線基板20に、それぞれ対向する第1の孔部11及び第2の孔部21が設けられ、それらの孔部に金属球30を設置して、前記第1及び第2の配線基板10、20と前記金属球30の接触部分を互いに接合した。

(もっと読む)

半導体装置の製造方法

【課題】半導体素子の破損を抑制すること。

【解決手段】上面に凹部18を備える基板10の前記凹部18内に第1半導体素子30を実装する工程と、前記第1半導体素子30の上面上に弾性体40を配置する工程と、第2半導体素子50の下面が前記弾性体40の上面に接するように前記第2半導体素子50の上面に荷重をかけて前記第2半導体素子50を前記基板10に接合する工程と、を含む半導体装置の製造方法。

(もっと読む)

電子デバイス

【課題】アウトガスによる影響を防止することで電子部品特性の低下を防止可能な、電子デバイスを提供する。

【解決手段】少なくとも1つの凹部又は少なくとも1つの凸部からなる立体形状17を有する接続電極33,34を有する基材3に電子部品1を実装する電子部品1の実装構造体2である。電子部品1は、所定の機能を有する機能片11と、機能片11に電気的に接続される導電部を含む被覆膜25,26により表面が覆われてなる第1の樹脂突起部24と、第1の樹脂突起部24により囲まれる領域の内側に設けられ、少なくとも表面に接着性を有する第2の樹脂突起部15と、を有している。第2の樹脂突起部15は、第1の樹脂突起部24の弾性変形により被覆膜25,26における導電部を接続電極33,34に導電接触させ、立体形状17と接続電極33、34に倣った状態に電子部品1を前記基材3に実装する。

(もっと読む)

1 - 20 / 91

[ Back to top ]