Fターム[5F044LL19]の内容

ボンディング (23,044) | フェイスダウンボンディング (4,630) | ハンダパッキング (4)

Fターム[5F044LL19]に分類される特許

1 - 4 / 4

電子部品

【課題】バンプを介して基板上に素子を搭載した電子部品において、素子をバンプに接合する際に生じる応力が素子に作用することを抑制し、電子部品の品質のばらつきを抑え、製造歩留まりを向上させる。

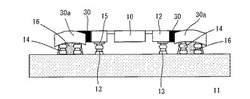

【解決手段】第1平面を有する基板11と、前記基板11の第1平面に固定されたバンプ14と、前記基板11の第1平面に非接触かつ相対すると共に、前記バンプ14に接着により固定され、かつ、前記パンプ14との接着領域の近傍にスリット30を有する素子12とを備える。

(もっと読む)

弾性波デバイス

【課題】信頼性の高い弾性波デバイスを提供すること。

【解決手段】本発明は、絶縁性基板11と、弾性波を励振する振動部22を有し、振動部22が絶縁性基板11と対向し、かつ振動部22が空隙51に露出するように、絶縁性基板11の上面に実装された弾性波デバイスチップ20と、振動部22を囲むように設けられ、絶縁性基板11と弾性波デバイスチップ20とを接合する接合部と、を具備し、接合部は、半田32と、半田32より高い融点を有しかつ絶縁性基板11の上面のコプラナリティより大きな厚さを有する金属層42と、を積層して形成されている弾性波デバイスである。

(もっと読む)

半導体素子の実装構造および半導体素子の実装方法

【課題】化合物半導体に適用可能で、かつ、小型化が可能で、かつ、気密封止型のシーリング構造を有する半導体素子の実装構造を提供する。

【解決手段】搭載した機能回路の配線層を利用して半導体素子基板1の外周部に少なくとも該機能回路を囲うシーリング構造21を形成し、かつ、実装基板6に、半導体素子基板1を収納するキャビティ7を設けるとともに、実装基板6の外周部に、配線層を利用して、シーリング構造21と鏡像対称な形状のシーリング構造5を形成し、半導体素子基板1のシーリング構造21と実装基板6のシーリング構造5とを、共晶温度が300℃以下の共晶合金による接合または表面活性化接合により接合する。また、半導体素子基板1上の機能回路の電極4と、実装基板6に設けられた電極15とを、共晶温度が300℃以下の共晶合金または表面活性化接合またはワイヤボンディングにより接合する。

(もっと読む)

電子部品及びその製造方法

【課題】

耐湿性に優れ、電極間の電気的接続及び振動部を含む封止領域への気密性を確実なものとし、さらに大型化が抑えられた電子部品を提供すること。

【解決手段】

圧電基板の一面に振動部及び第1の電極が設けられた圧電素子と第2の電極を備えた配線基板とを含む電子部品において、第1の電極及び第2の電極の一方側に設けられ、第1の電極及び第2の電極の他方側に接続されたバンプと、振動部を囲う環状の第1の金属層と、前記第1の金属層に沿って設けられ、第1の金属層と配線基板との間を封止して振動部の配置領域を気密空間とするバンプより固相線温度が低いはんだ材料と、を備えた電子部品を構成することで気密空間への透湿及びはんだ材料の外方への広がりが抑えられ、またバンプが溶融して広がるスペースを省くことができる。また電極間の電気的接続と配置領域の封止とを別工程にて行えるので高い気密性が得られる。

(もっと読む)

1 - 4 / 4

[ Back to top ]