Fターム[5F044QQ00]の内容

ボンディング (23,044) | ワイヤレスボンディング用半導体チップ (2,288)

Fターム[5F044QQ00]の下位に属するFターム

バンプ電極 (1,821)

パッド電極 (301)

チップの両面に電極があるもの (28)

ショート防止 (34)

識別、位置合せ用孔、マーク (28)

Fターム[5F044QQ00]に分類される特許

1 - 20 / 76

半導体装置

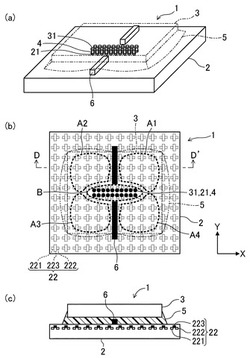

【課題】アンダーフィルの収縮が半導体チップの電気特性に及ぼす影響を低減できる半導体装置を提供する。

【解決手段】半導体装置1は、半導体チップ2とベース材3との積層構造を有する。半導体チップ2の表面上に電極21が形成されており、ベース材3の表面上に電極31が形成されている。半導体チップ2の前記表面とベース材3の前記表面とが対向すると共に電極21と電極31とが突起電極4を介して電気的に接続されている。半導体チップ2の前記表面とベース材3の前記表面とに挟まれた領域のうち、電極配置領域B以外の他の領域に位置する部分のアンダーフィル5に分断領域6が設けられている。

(もっと読む)

電子部品

【課題】バンプを介して基板上に素子を搭載した電子部品において、素子をバンプに接合する際に生じる応力が素子に作用することを抑制し、電子部品の品質のばらつきを抑え、製造歩留まりを向上させる。

【解決手段】第1平面を有する基板11と、前記基板11の第1平面に固定されたバンプ14と、前記基板11の第1平面に非接触かつ相対すると共に、前記バンプ14に接着により固定され、かつ、前記パンプ14との接着領域の近傍にスリット30を有する素子12とを備える。

(もっと読む)

パッケージ支持面にクリップを利用する高電圧III族窒化物整流器パッケージ

【課題】パッケージ支持面にクリップを利用する高電圧III族窒化物整流器パッケージの典型的な実施形態を提供する。

【解決手段】パッケージ支持面260に取り付け、III族窒化物トランジスタ230のソースにスタックされたダイオード220のアノードを有するIII族窒化物トランジスタ230と、III族窒化物トランジスタ230のゲートおよびダイオード220のアノードに結合した第1の導電性クリップ212bと、III族窒化物トランジスタ230のドレインに結合した第2の導電性クリップ212aとを含む。導電性クリップ212a、212bはパッケージ支持面260に結合され、表面実装性の平担部を露出する。

(もっと読む)

電子部品、電子機器、及びはんだペースト

【課題】電子部品をプリント配線板などにはんだ接続する際に、溶融したはんだによる電極間のショートの発生を防ぐことができるはんだペースト、電子部品、該電子部品を用いた電子機器の提供。

【解決手段】電極パッドを有する配線基板と、前記配線基板に実装され、複数の電極を有する部品と、前記部品を覆う封止樹脂と、前記配線基板内の配線を、外部の基板と接続する複数の端子とを有し、前記複数の電極が、前記電極パッドとはんだにより接続されており、前記はんだと前記封止樹脂との間に、前記はんだ側から、第1のヤング率を有する第1の樹脂層と、前記第1のヤング率よりも大きな値の第2のヤング率を有する第2の樹脂層とが順に形成されている電子部品である。

(もっと読む)

半導体チップ、半導体パッケージおよび半導体パッケージの製造方法

【課題】クラックの発生を抑制できる信頼性の高い半導体チップ、半導体パッケージ、および半導体パッケージの製造方法を提供する。

【解決手段】半導体チップ1は、回路面3に突起電極2を有する平板状のものであって、回路面3よりも面積の大きい底面4と、回路面3と底面4とを繋ぐ側面5とを備えている。回路面3と底面4との間の厚みDが100μm以下である。側面5は、底面4に連続して形成された垂直面6と、垂直面6に連続して形成されるとともに、回路面3に連続するように内方へ傾斜した傾斜面7とを有している。垂直面6の高さをdとした場合に、d/Dの値が0より大きく、かつ、1/2より小さく設定されている。傾斜面7は、凹状に湾曲した凹曲面に形成されている。

(もっと読む)

接続構造体及び接続構造体の製造方法

【課題】電極間の接続抵抗が低く、かつ耐熱衝撃特性が高い接続構造体を提供する。

【解決手段】本発明に係る接続構造体1は、第1の電極2bを上面2aに有する第1の接続対象部材2と、第2の電極4bを下面4aに有する第2の接続対象部材4と、第1の接続対象部材2の上面2aと第2の接続対象部材4の下面4aとの間に配置されており、かつ導電性粒子21を含む異方性導電材料により形成されている接続部3とを備える。導電性粒子21は、樹脂粒子22と、第1の導電層23と、第1の導電層23よりも融点が低い第2の導電層24とを有する。導電性粒子21における樹脂粒子22の中心を通る中心線に対して、導電性粒子21における第2の導電層24は、上下非対称に偏在しており、上記中心線に対して上側の領域又は下側の領域に第2の導電層24全体の70体積%以上、100体積%以下が存在する。

(もっと読む)

液状硬化性組成物

【課題】

硬化することにより長期信頼性に優れた硬化物が得られる液状硬化性組成物を提供する。

【解決手段】

(A)過酸化水素を酸化剤として用いた酸化反応により分子内に炭素−炭素二重結合を有する化合物の炭素−炭素二重結合をエポキシ化して得られる全塩素量が10質量ppm以下であるエポキシ化合物、(B)硬化剤および(C)充填材を含む液状硬化性組成物である。好ましくはエポキシ化合物はアリルエーテル結合を有する化合物の炭素−炭素二重結合を酸化して得られる2つ以上のグリシジル基を一分子中に有する室温で液状の化合物である。

(もっと読む)

半導体装置の製造方法

【課題】

チップの損傷及び反りを抑制し、優れた放熱性を有するフィリップチップ型の半導体装置を製造するための簡便かつ効果的な方法を提供すること。

【解決手段】

本発明による半導体装置の製造方法は、表面に回路が形成された半導体チップの裏面に硬化収縮性材料から構成される反り抑制層を設ける工程と、上記反り抑制層を有する半導体チップをフェースダウンで接着層を介して基板に実装する工程とを有することを特徴とする。

(もっと読む)

半導体装置

【課題】半導体チップが基板にフリップチップ実装されて構成された半導体装置において、搭載された素子の特性の変動量を均一にすることが可能な半導体装置を提供する。

【解決手段】上面31と、底面の中央部である第1の底面32と、底面の外周端部である第2の底面33とを有する半導体チップ3と、第1の底面32に形成された外部接続電極4とを備え、上面31から第2の底面33までの距離は、上面31から第1の底面32までの距離よりも短く、上面31から半導体チップ3の外周の一辺の中央における第2の底面33までの距離は、上面31から半導体チップ3の外周の一辺の端における第2の底面33までの距離よりも短い。

(もっと読む)

半導体装置およびその製造方法

【課題】外部基板との接合による、基板に形成された素子における不具合の発生を抑制する手段を提供する。

【解決手段】半導体装置100は、基板111と応力形成膜140とを備える。基板111の第1面の一端部分および他端部分には突起部130が形成される。基板111には、半導体素子112が形成される。応力形成膜140は、基板111の第1面の反対側の第2面に接するように形成される。応力形成膜140の形状は、外部基板200と突起部130との接合により生じる第1応力P10の少なくとも一部を相殺する第2応力P20を生じさせる形状である。

(もっと読む)

電子装置の製造方法

【課題】環境負荷が小さく低コストで、150℃以上の高温下で長時間使用しても接続信頼性を維持できる電子装置の製造方法を提供する。

【解決手段】電子装置のはんだ接続部1において、基板5の電極となるCu層上にNiめっき層3が形成され、はんだボールを構成し、かつ室温から200℃においてCu6Sn5相を含有するSn系はんだ8との間に化合物層2を有する。化合物層2はCu6Sn5相がNiめっき上に析出あるいは移動してバリア層を形成し、界面反応を抑制する。

(もっと読む)

半導体装置およびその製造方法

【課題】実装基板にうねりがあったり、実装基板のパッド電極に高低差があっても、半導体チップの電極を信頼性高く接続できるようにする。

【解決手段】回路基板1上に半導体チップ3がフェースダウン状態で搭載され、回路基板1上に形成されたパッド電極2と半導体チップ3上に形成された電極4とが接合されている。回路基板1と半導体チップ3との間の隙間にはアンダーフィルとしての樹脂5が充填されている。パッド電極2の頂上には高低差があるが、半導体チップ3がその高低差に追随して湾曲することにより、パッド電極2と電極4との接合は信頼性高く実現できる。

(もっと読む)

表示装置及び表示装置の製造方法

【課題】 異方性導電膜に含まれる導電性粒子密度を直接測定する手段がなかった。異方性導電膜の粒子密度バラツキがあっても判らなかった。

【解決手段】 ICチップ1の能動面に配線禁止領域10を設け、ICチップ1が実装される表示素子の透明基板9に配線禁止領域に対応するように透明な透視領域3を設ける。透視領域3を通して配線領域上に配置された導電性粒子7の数を測定することで、異方性導電膜に含まれる導電性粒子密度を検査することができる。

(もっと読む)

半導体装置の製造方法及び回路部材接続用接着シート

【課題】半導体素子を配線回路基板にフリップチップ実装する場合であっても、半導体素子の薄厚化を図るとともに、配線回路基板及び半導体素子間を良好に樹脂封止できる半導体装置の製造方法を提供する。

【解決手段】バンプ22とその上に設けられたはんだボール24とからなる突起電極を有する半導体ウェハ20面上に、粘接着剤層2及び弾性率が450MPa以下であるプラスチックシート1をこの順に備える接着シートを、粘接着剤層2が突起電極を埋めるように貼り付ける工程と、半導体ウェハ20の突起電極が形成されている側とは反対側の面を研磨して薄厚化する工程と、薄厚化した半導体ウェハ20及び粘接着剤層2を切断して粘接着剤付き半導体素子を得る工程と、熱圧着して配線回路基板と半導体素子とがはんだボール24を介して電気的に接続され、配線回路基板と半導体素子との間が粘接着剤2により封止された構造の半導体装置を得る工程と、を備える。

(もっと読む)

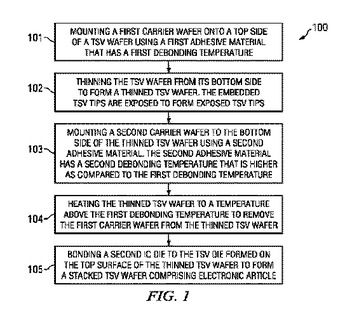

ICダイ又はウエハをTSVウエハに接合するためのデュアルキャリア

シリコン貫通ビア(TSV)ウエハを用いてスタックされた電子的部品を形成する方法が、第1ディボンデング温度を有する第1接着性材料(206)を用いてTSVウエハ(202)の上側に第1キャリアウエハ(205)を搭載することを含む。TSVウエハは、その下側から薄くされて薄くされたTSVウエハ(202’)を形成する。第1ディボンデング温度より高い第2ディボンデング温度を有する第2接着性材料(207)を用いて、TSVウエハ(202’)の下側に第2キャリアウエハ(215)が搭載される。薄くされたTSVウエハ(202’)はそれから第1キャリアウエハ(205)を取り除くため、前記第1ディボンデング温度を超える温度まで加熱される。スタックされた電子的部品を形成するため、少なくとも1つの個片化されたICダイが、薄くされたTSVウエハの上面上に形成されたTSVダイに結合される。

(もっと読む)

(もっと読む)

ダイシングテープ一体型半導体裏面用フィルム

【課題】半導体ウエハのダイシング工程から半導体チップのフリップチップボンディング工程にかけて利用することができるダイシングテープ一体型半導体裏面用フィルムを提供すること。

【解決手段】 基材上に粘着剤層を有するダイシングテープと、該粘着剤層上に設けられたフリップチップ型半導体裏面用フィルムとを有するダイシングテープ一体型半導体裏面用フィルムであって、フリップチップ型半導体裏面用フィルムが、黒色顔料を含有しているダイシングテープ一体型半導体裏面用フィルム。

(もっと読む)

異方性導電フィルム

【課題】水分による接着性の低下が抑制された、保存安定性に優れた異方性導電フィルムを提供する。

【解決手段】導電性粒子が絶縁性接着剤に分散し、フィルム状に成形されている異方性導電フィルムであって、ゼオライトを1〜20wt%含有する。該ゼオライトの平均細孔径は3〜5オングストロームであり、導電性粒子の平均粒子径はゼオライトの平均粒子径よりも大きい。

(もっと読む)

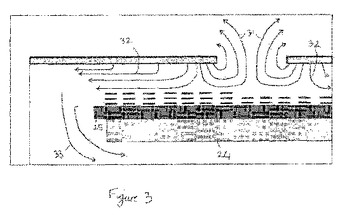

ピックアンドプレースマシン用プレースステーション

基板を支持するためのプレースステージを含むプレースステージ組立体と、基板における清浄環境をもたらすためのカバー部であって、載置動作が基板の制限された範囲に実行され得るカバー部の第1の面に第1の開口部を含むカバー部とを備え、プレースステージおよびカバー部は、相対移動によって、開口部が基板の上方に選択された相対位置を得ることが可能になるように取り付けられる、ピックアンドプレースマシン用のプレースステーション。  (もっと読む)

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】支持基板上に半導体チップをフェイスダウン実装した構成において、半導体チップの裏面上に板状材を水平に搭載可能な半導体装置を提供する。

【解決手段】半導体装置1-1は、支持基板3上に突起電極7を介して半導体チップ5がフェイスダウン実装され、これらの支持基板3−半導体チップ5間に樹脂9が充填された構成である。特に、半導体チップ5は、支持基板3側に対向して配置された実装面5aと反対側の裏面5bに、段差部Aを有している。この段差部Aは、半導体チップ5の裏面5bにおける周端縁を切り欠いて設けられている。

(もっと読む)

半導体装置及びその製造方法

【課題】半導体装置及びその製造方法を提供する。

【解決手段】接合面を有し、接合面には複数の半田付け部が設けられかつ絶縁層が被覆され、絶縁層には前記複数の半田付け部を露出するための開口が形成された基板と、基板上に結合されたチップであって、本体、複数のバンプ及び自己粘着性保護層を含み、自己粘着性保護層がチップ表面上に形成され前記複数のバンプを自己粘着性保護層から露出させ、かつ突出させているチップと、を備え、当該自己粘着性保護層は、感光性接着剤、熱硬化性接着剤及び誘電体材料からなり、チップは、自己粘着性保護層と基板との結合により複数のバンプが複数の半田付け部に電気的に接続され、開口の少なくとも一端を露出できるため、ディスペンス作業を別途行うことなくチップと基板とを結合することができ、製造工程や製造コストを大幅に低減させることができる利点を有している。

(もっと読む)

1 - 20 / 76

[ Back to top ]