Fターム[5F045AB01]の内容

気相成長(金属層を除く) (114,827) | 成長層の組成 (12,584) | 4族 (3,529)

Fターム[5F045AB01]の下位に属するFターム

Fターム[5F045AB01]に分類される特許

1 - 20 / 241

半導体装置、半導体装置の製造方法および薄膜

【課題】導電性または半導体性を示す、新規な環状シロキサン重合体を含む半導体装置を提供する。

【解決手段】この半導体装置は、中心金属に遷移金属を有する構造単位(A)と、隣り合う構造単位(A)の間に位置し、環状シロキサン骨格を含む構造単位(B)と、を含むプラズマ重合体からなる電荷輸送層を備えている。なお、中心金属に遷移金属を有する有機金属化合物と、環状シロキサン化合物と、を反応炉でプラズマ重合させることにより、当該電荷輸送層を形成する。

(もっと読む)

シード層の形成方法及びシリコン含有薄膜の成膜方法

【課題】 薄膜の面内均一性の更なる向上を可能とする、薄膜を形成するためのシード層の形成方法を提供すること。

【解決手段】 下地上に、薄膜のシードとなるシード層を形成するシード層の形成方法であって、アミノシラン系ガスを用いて、下地上に、アミノシラン系ガスに含まれた少なくともシリコンを吸着させる工程(ステップ11)と、ジシラン以上の高次シラン系ガスを用いて、アミノシラン系ガスに含まれた少なくともシリコンが吸着された下地上に、ジシラン以上の高次シラン系ガスに含まれた少なくともシリコンを堆積する工程(ステップ12)と、を具備する。

(もっと読む)

プラズマ処理装置及び方法

【課題】基材の表面近傍をごく短時間だけ均一に高温熱処理するに際して、あるいは、反応ガスによるプラズマまたはプラズマと反応ガス流を同時に基材へ照射して基材を低温プラズマ処理するに際して、基材の所望の被処理領域全体を短時間で処理することができるプラズマ処理装置及び方法を提供することを目的とする。

【解決手段】誘導結合型プラズマトーチユニットTにおいて、多重の渦形のスパイラルコイル3が第一石英板4に接合され、誘導結合型プラズマトーチユニットTの最下部にプラズマ噴出口8が設けられる。第二石英板5及び第三石英板6に囲まれた長尺チャンバ内部の空間7にガスを供給しつつ、スパイラルコイル3に高周波電力を供給して、長尺チャンバ内部の空間7にプラズマを発生させ、基材2に照射する。

(もっと読む)

半導体装置及びその製造方法

【課題】キャパシタの上部電極上に形成される充填膜の膜厚均一性を向上させる。

【解決手段】半導体基板1と、半導体基板1上に形成された下部電極14と、下部電極14上に形成された容量絶縁膜15と、容量絶縁膜15上に形成された上部電極16と、上部電極16の表面に形成された表面改質層と、表面改質層上に形成された充填膜18を有する半導体装置100。

(もっと読む)

薄膜の形成方法及び成膜装置

【課題】比較的低温でも埋め込み特性が良好で且つ表面ラフネスの精度も向上するアモルファス状態の不純物含有のシリコン膜のような薄膜を形成することが可能な薄膜の形成方法を提供する。

【解決手段】真空排気が可能になされた処理容器内で被処理体Wの表面にシード膜88と不純物含有のシリコン膜90を形成する薄膜の形成方法において、処理容器内へアミノシラン系ガスと高次シランの内の少なくともいずれか一方のガスよりなるシード膜用原料ガスを供給してシード膜を形成する第1ステップと、処理容器内へシラン系ガスと不純物含有ガスとを供給してアモルファス状態の前記不純物含有のシリコン膜を形成する第2ステップとを有する。

(もっと読む)

不揮発性半導体記憶装置、及びその製造方法

【課題】チャネル移動度を向上させた不揮発性半導体記憶装置、及びその製造方法を提供する。

【解決手段】不揮発性半導体記憶装置は、半導体基板20上に設けられたメモリトランジスタ40と選択トランジスタ50を有する。メモリトランジスタ40は、導電層41a〜41d、メモリゲート絶縁層43、柱状半導体層44、及び酸化層45を有する。導電層41は、メモリトランジスタ40のゲートとして機能する。メモリゲート絶縁層43は、導電層の側面に接する。半導体層44は、導電層と共にメモリゲート絶縁層43を一方の側面で挟み、半導体基板20に対して垂直方向に延び、メモリトランジスタ40のボディとして機能する。酸化層45は、半導体層44の他方の側面に接する。半導体層44は、シリコンゲルマニウムにて構成される。酸化層45は、酸化シリコンにて構成される。

(もっと読む)

基板処理方法および基板処理装置

【課題】シリコン酸化膜の除去後、シリコンゲルマニウム膜の形成までのQタイムを長くするとともに、シリコンゲルマニウム膜の形成におけるプリベイクの温度を低くする。

【解決手段】基板処理装置1では、酸化膜除去部4にて基板9の一の主面上のシリコン酸化膜が除去された後、シリル化処理部6にてシリル化材料を付与して、当該主面に対してシリル化処理が施される。これにより、シリコン酸化膜の除去後、シリコンゲルマニウム膜の形成までのQタイムを長くするとともに、シリコンゲルマニウム膜の形成におけるプリベイクの温度を低くすることができる。

(もっと読む)

基板処理装置

【課題】処理室へ供給されるガスを充分に加熱することにより、ヘイズやスリップに起因する成膜不良を抑制することができる技術を提供する。

【解決手段】本発明における特徴は、例えば、図2に示すように、処理室209の外壁205とインナーチューブ206の間にガス導入空間210を設け、このガス導入空間210内に誘導加熱するための加熱体207を設けている点にある。これにより、ガス供給部211から供給される原料ガスは、まず、処理室209の内部に導入される前に先立って、ガス導入空間210内に導入され、このガス導入空間210に設けられている加熱体207によって加熱される。

(もっと読む)

シリコン基板上に高電子移動度トランジスタを成長させた構造及びその方法

【課題】シリコン基板上に高電子移動度トランジスタを成長させた構造及びその方法の提供。

【解決手段】本シリコン基板上に高電子移動度トランジスタを成長させた構造及びその方法は、半導体産業において半導体装置製造に用いられる。本発明によると、UHVCVDシステムを使用してGeフィルムをSi基板上に成長させ、その後、高電子移動度トランジスタを該Geフィルム上に成長させることで、バッファ層の厚さとコストを低減する。該Geフィルムの機能は、Si基板上にMOCVDによりIII-V MHEMT構造を成長させるときに、シリコン酸化物の形成を防止することである。本発明においてMHEMTを使用する理由は、MHEMT構造中の変成バッファ層がGeとSi基板間の非常に大きな格子不整合度のために形成される貫通転位をブロックし得ることにある。

(もっと読む)

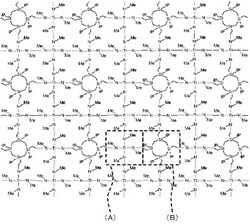

気相成長装置

【課題】結晶膜を基板の上に成長させる化学気相成長(CVD)の量産では、均一性を改良しながらバッチサイズを大きくする装置構造が課題である。装置の部品の洗浄交換周期を長くし、CVDガスの基板上での消費効率を上げて、排気系のポンプや排気配管への付着を減らしたい。さらに有機金属ガスをCVDガスとして用いるとき、気相で重合反応を起こし粒子ゴミを発生させるので、加熱空間を横切る流路を短くしたい。これらの要求を満たす装置の構造が課題である。

【解決手段】表面に基板を載せる複数の加熱されるサセプタを立てて放射状に配置させ、当該放射状配置のサセプタを回転させながら外周から熱分解CVDガスを供給して当該基板の上にCVD膜を成長せしめ、当該放射状配置サセプタの配置中心に加熱可能な排気管が配置されてあり、当該CVDガスを当該排気管から排気することで、課題を解決する結晶膜の気相成長装置が可能である。

(もっと読む)

基板処理装置及び半導体装置の製造方法

【課題】高温処理においても、サセプタ変形を抑制することができる基板処理技術を提供する。

【解決手段】基板が載置された載置体と、前記載置体が複数支持された載置体支持具と、前記載置体支持具が収容される反応管と、前記反応管の外側に設けられ、前記反応管内に収容された基板を加熱する加熱部とを備え、前記載置体の、前記基板と接触する面と前記載置体支持具と接触する面が、同じ粗さに表面加工されるように基板処理装置を構成する。

(もっと読む)

ヘテロエピタキシャル層を備えた半導体ウェハ及び前記ウェハの製造方法

【課題】バウの制御のためだけでなく、SiGeエピタキシャル層の品質を改善するために、特にSi基板上に堆積されたSiGe層のクロスハッチ及び表面ラフネスを低減するために、背面層によって形成された応力を用いる適切な解決策を提供する。

【解決手段】第1の面及び第2の面を有する基板10、前記基板の第1の面に堆積された完全に又は部分的に緩和されたヘテロエピタキシャル層20、及び前記基板の第2の面に堆積された応力相殺層30を有する、半導体ウェハ。

(もっと読む)

半導体製造装置におけるウエハステージおよびその使用方法

【課題】ウエハステージにおいて石英ガラスからなる当設部材が割れるのを防止する。

【解決手段】ウエハWを支持する支持ユニット2をウエハWの外周円上に配置したウエハステージであって、各支持ユニット2は、ウエハWの外周縁に接するセラミック質の当接部材3と、当接部材3が装着される金属製のベース部と、当接部材3をベース部に固定する固定具とを備える。ベース部には挿入孔40が形成され、当接部材3には挿入孔40に向かって上下に貫通する係合孔30が形成され、固定具は挿入孔40に嵌合する上下に延びる軸部54と係合孔30に係合する係合頭部53とが一体に形成されたピン5を備え、ピン5が永久磁石の磁力によって下方に向かって付勢されていることで当接部材を固定している。

(もっと読む)

新規な水素化シリコンゲルマニウム、その製造法および使用法

【課題】本発明は、新規水素化シリコンゲルマニウム化合物、それらの合成法、それらの成膜法、およびそれらの新規化合物を用いて作製された半導体構造を提供する。

【解決手段】これらの化合物は、式:(SiHn1)x(GeHn2)yによって定義される。式中、xは2,3または4であり;yは1,2または3であり;x+yは3,4または5であり;n1は、化合物中の各Si原子に関して独立に0,1,2または3であって原子価を満たし;n2は、化合物中の各Ge原子に関して独立に0,1,2または3であって原子価を満たし;但し、yが1のとき、n2は0ではなく;さらに、xが3、かつ、yが1のとき、n2は2または3であり;さらに、xが2、かつ、yが1のとき、n2は3である。

(もっと読む)

シリコン系薄膜の製造方法

【課題】 シリコン系薄膜の製造方法に関して、大面積の基板を用いた場合においても、高品質かつ均一な薄膜を得られる方法を提供することを目的とする。

【解決手段】 少なくとも、高周波電極と、該高周波電極と対向して配置される基板と、該高周波電極と対向して配置され、かつ、該基板を保持するホルダとを含み、プラズマCVD装置を使用するシリコン系薄膜の製造方法であって、

該高周波電極面と該ホルダ面との距離(E/H)、および該高周波電極面と該ホルダに保持された基板の面との距離(E/S)の差D=(E/S)−(E/H)が、

2mm以上4mm以下であり、かつ該距離(E/S)が、5mm以上10mm以下であることを特徴とするシリコン系薄膜の製造方法である。好ましくは該シリコン系薄膜が非晶質シリコン系薄膜であることを特徴とする。

(もっと読む)

熱処理装置の運転方法

【課題】ゲルマニウムを含む薄膜の成膜処理をした後に、ゲルマニウムが汚染物質となる薄膜を成膜処理する場合に、後の成膜処理におけるゲルマニウム汚染を抑える熱処理装置の運転方法を提供する。

【解決手段】被処理体Wを保持具25に保持させて反応容器2内に搬入し、熱処理を行う熱処理装置1の運転方法において、反応容器2内に処理ガスを供給すると共に反応容器2内を加熱して、被処理体Wにゲルマニウムを含む薄膜を成膜する工程と、反応容器2内に被処理体Wが搬入されていない状態クリーニングガスを供給して前記反応容器2内に成膜された薄膜を除去する工程と、酸化ガスと、水素ガスとを反応容器2内に供給すると共に加熱して活性化されたガスにより反応容器2内に存在するゲルマニウムを除去する工程と、反応容器2内に被処理体Wを搬入して処理ガスを供給すると共に加熱して、被処理体にゲルマニウムが汚染物質となる薄膜を成膜する工程、とを含む。

(もっと読む)

エピタキシャル構造体及びその製造方法

【課題】本発明は、エピタキシャル構造体及びその製造方法に関する。

【解決手段】本発明のエピタキシャル構造体の製造方法は、少なくとも一つのエピタキシャル成長面を有する基板を提供する第一ステップと、前記基板のエピタキシャル成長面の上に複数の空隙を含むカーボンナノチューブ層を懸架するように配置する第二ステップと、前記基板のエピタキシャル成長面にエピタキシャル層を成長させて、前記カーボンナノチューブ層を包む第三ステップと、を含む。

(もっと読む)

エピタキシャル構造体及びその製造方法

【課題】本発明は、エピタキシャル構造体及びその製造方法に関する。

【解決手段】本発明のエピタキシャル構造体の製造方法は、少なくとも一つのエピタキシャル成長面を有する基板を提供する第一ステップと、前記基板のエピタキシャル成長面に複数の空隙を含むカーボンナノチューブ層を配置する第二ステップと、前記基板のエピタキシャル成長面に真性半導体エピタキシャル層を成長させる第三ステップと、前記真性半導体エピタキシャル層の上に、ドープされた半導体エピタキシャル層を成長させる第四ステップと、を含む。

(もっと読む)

微結晶半導体膜、及び半導体装置の作製方法

【課題】結晶性の高い微結晶半導体膜の作製方法を提供することを課題とする。また、電気特性が良好な半導体装置を、生産性高く作製する方法を提供する。

【解決手段】第1の条件により、高い結晶性の混相粒を低い粒密度で有する種結晶を絶縁膜上に形成した後、種結晶上に、第2の条件により混相粒を成長させて混相粒の隙間を埋めるように第1の微結晶半導体膜を形成し、第1の微結晶半導体膜上に、第1の微結晶半導体膜に含まれる混相粒の隙間を広げず、且つ結晶性の高い微結晶半導体膜を成膜する第3の条件で第2の微結晶半導体膜を形成し、第2の微結晶半導体膜上に、第2の微結晶半導体膜に含まれる混相粒の隙間を埋めつつ、結晶成長を促す第4の条件で、第3の微結晶半導体膜を積層形成する。

(もっと読む)

CVDエッチングおよび堆積シーケンスにより形成されるCMOSトランジスタ接合領域

【課題】CMOSトランジスタのソース−ドレイン置換技術に関し、装置一式を利用して基板材料に窪みをエッチングして、その後、応力を有する異なる材料を堆積することに関し、大気に曝すことなく、エッチングとその後の堆積とを行う方法の提供。

【解決手段】エッチングおよびデポジションによりCMOSトランジスタの接合領域を形成する方法であって、

第1接合領域270を形成すべくゲート電極190の隣の基板120の第1箇所と、前記基板120に第2接合領域280を形成すべく前記ゲート電極190を介して前記第1箇所とは反対側に位置する前記基板120の第2箇所とを除去する工程と、前記第1接合領域270と前記第2接合領域280とに結晶質材料のエピタキシャル厚みを有する層を形成する工程とを含み、前記除去する工程と前記形成する工程は同一のチャンバ内で前記チャンバの封止を破ることなく行う。

(もっと読む)

1 - 20 / 241

[ Back to top ]