Fターム[5F045AD10]の内容

気相成長(金属層を除く) (114,827) | 成膜条件−成膜温度 (8,040) | 600≦T<700℃ (701)

Fターム[5F045AD10]に分類される特許

1 - 20 / 701

気化・堆積装置および方法

発光ダイオード

シリコンエピタキシャルウェーハの製造方法

【課題】エピタキシャル成長の際の裏面クモリやピンハローを抑制して、高品質なシリコンエピタキシャルウェーハを製造することができる方法を提供することを目的とする。

【解決手段】気相成長装置を用いて、サセプタのウェーハ載置面上にシリコン単結晶基板を載置して、該シリコン単結晶基板上にエピタキシャル成長させることによりシリコンエピタキシャルウェーハを製造する方法であって、サセプタとして、SiCにより表面をコートされた黒鉛製サセプタをチャンバー内に配設し、黒鉛製サセプタのウェーハ載置面上にポリシリコンのコートは行わずに、ウェーハ載置面上にリフトピンによりシリコン単結晶基板を載置して、シリコン単結晶基板上にエピタキシャル成長させることで、エピタキシャル成長においてシリコン単結晶基板の裏面のリフトピンの先端部に対向する領域に発生する面荒れを防止するシリコンエピタキシャルウェーハの製造方法。

(もっと読む)

基板処理装置、基板処理方法及び半導体装置の製造方法

【課題】膜厚の面間均一性を維持しつつ、膜厚の面内分布が中央凹の分布となることを抑止する。

【解決手段】複数枚の基板を処理する反応管と、反応管内を加熱するヒータと、反応管内で複数枚の基板を配列させて保持する保持具と、複数枚の基板が配列される基板配列領域に対応する領域に配置され、該領域の複数箇所から反応管内に水素含有ガスを供給する第1ノズルと、基板配列領域に対応する領域に配置され、該領域の複数箇所から前記反応管内に酸素含有ガスを供給する第2ノズルと、反応管内を排気する排気口と、反応管内の圧力が大気圧よりも低い圧力となるように制御する圧力制御器と、を有し、第1ノズルには複数枚の基板の一枚一枚に対応しないように複数の第1ガス噴出孔が設けられ、第2ノズルには少なくとも複数枚の基板の一枚一枚に対応するように少なくとも複数枚の基板の枚数と同数の第2ガス噴出孔が設けられる。

(もっと読む)

光半導体素子及びその製造方法

【課題】高い光利得を得ながら閾値電流値を低減することができる光半導体素子及びその製造方法を提供する。

【解決手段】基板の上方に形成された複数の量子ドット層12と、複数の量子ドット層12間に位置する中間層と、が設けられている。量子ドット層12に含まれる量子ドット12aの組成が、InxGa1-xAsySb1-y(0<x≦1、0<y≦1)で表わされる。中間層には、組成がInaGa1-aAsbP1-b(0<a<1、0<b<1)で表わされ、厚さが10nm以上40nm以下のInGaAsP層13、15と、InGaAsP層13、15の底面から10nm以上40nm未満の高さに位置し、厚さが0.3nm以上2nm以下のInP層14と、が含まれている。

(もっと読む)

III/V半導体

【課題】SiあるいはGaP技術をベースとする集積回路にモノリシックに集積化される、新しいIII/V半導体を用いた、発光ダイオードおよびレーザダイオードの半導体構造及び製造方法、あるいはまた、モジュレータ構造および検出器構造への使用法を提供する。

【解決手段】ドープされたSiあるいはドープされたGaPをベースとするキャリア層A、およびそこに配設されたIII/V半導体Dを備え、組成GaxInyNaAsbPcSbdを有するモノリシック集積回路構造であって、ここで、x=70−100モル−%、y=0−30モル−%、a=0.5−15モル−%、b=67.5−99.5モル−%、c=0−32.0モル−%およびd=0−15モル−%、xとyの合計は、常に100モル−%であり、a、b、cおよびdの合計は、常に100モル−%であり、そして、一方のxとyの合計と他方のaないしdの合計の比率は、実質的に1:1である。

(もっと読む)

III−V族化合物半導体層を含む半導体素子及びその製造方法

【課題】III−V族化合物半導体層を含む半導体素子及びその製造方法を提供する。

【解決手段】III−V族物質を含む半導体素子及びその製造方法に係り、該半導体素子は、溝を含むシリコン基板30と、溝周囲の基板上に形成されたハードマスク32と、溝を充填する、ハードマスク上に形成された第1物質層34と、第1物質層上に形成された上部物質層36、及び上部物質層上に形成された素子層と、を含み、該第1物質層は、III−V族物質層であり、該上部物質層は、第1物質層の一部でもあり、該上部物質層は、第1物質層と同一物質または異なる物質であってもよい。

(もっと読む)

プラズマ処理装置

【課題】導電性の筒状部材を真空容器内に配置すると共に、筒状部材での微小放電を抑制するプラズマ処理装置を提供する。

【解決手段】内周面にアルマイト層31aが形成されたアルミニウムからなる筒状部材31を、金属製の真空容器12の内壁面に沿って配置すると共に、真空容器12の内部の支持台21、22上に処理対象の基板Wを静電吸着して、プラズマ処理を行うプラズマ処理装置において、真空容器12の内壁面の全周に渡って形成され、当該内壁面から突設された段差部12aと、段差部12aの上面の全周に渡って配置された弾性変形可能な金属製のチューブリング32とを有し、チューブリング32を介して、筒状部材31を段差部12a上に載置した。

(もっと読む)

半導体装置の製造方法、基板処理方法、基板処理装置およびプログラム

【課題】低温領域において、フッ化水素に対する耐性の高い窒化膜を形成する。

【解決手段】基板に対して原料ガスを供給する工程と、基板に対してプラズマ励起させた水素含有ガスを供給する工程と、基板に対してプラズマ励起または熱励起させた窒化ガスを供給する工程と、基板に対してプラズマ励起させた窒素ガスおよびプラズマ励起させた希ガスのうち少なくともいずれかを供給する工程と、を含むサイクルを所定回数行うことで、基板上に窒化膜を形成する工程を有する。

(もっと読む)

半導体装置の製造方法

【課題】本発明は、基板に元々付着していた不純物及び成長炉内の不純物を低減することができる半導体装置の製造方法を提供することを目的とする。

【解決手段】本発明に係る半導体装置の製造方法は、基板を成長炉内に搬入する搬入工程と、該基板の上と該成長炉の内壁に、該基板表面と該成長炉内の不純物を吸収する不純物吸収層を形成する吸収層形成工程と、該不純物吸収層と、該基板の一部とをエッチングすることで該基板を薄化基板にするエッチング工程と、該薄化基板の上にバッファ層を形成するバッファ層形成工程と、該バッファ層の上に半導体層を形成する半導体層形成工程と、を備えたことを特徴とする。

(もっと読む)

InGaNを含む半導体層の成膜を行う気相成長方法および気相成長装置

【課題】InGaNを含む半導体の形成で、高品質・高In組成のInGaNを含む半導体の形成を可能とする。

【解決手段】

気相成長装置を用いて、基板上に少なくともInGaNを含む半導体薄膜を形成する気相成長方法であって、前記気相成長装置内で第一のN源とIn源とを反応させ、InN源を生成する第1のステップと、前記気相成長装置内で、第一のN源とは異なる第二のN源とGa源とを反応させ、GaN源を生成する第2のステップと、前記第1のステップで生成された前記InN源と、前記第2のステップで生成された前記GaN源とを前記基板上で反応させ、前記基板上に薄膜を形成する第3のステップとを有する気相成長方法を提供する。

(もっと読む)

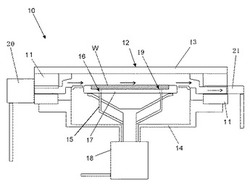

成膜装置及びその運用方法

【課題】処理容器内の処理空間に接する石英製の部材の表面に対するカーボン膜の密着性を向上させてパーティクルの発生を抑制することができる成膜装置の運用方法を提供する。

【解決手段】石英製の処理容器8内で保持手段22に保持された複数の被処理体Wの表面にカーボン膜を成膜する成膜工程を行うようにした成膜装置の運用方法において、処理容器内の処理空間に接する石英製の部材の表面にカーボン膜の密着性を向上させる密着膜70を形成する密着膜形成工程を行うようにする。これにより、処理容器内の処理空間に接する石英製の部材の表面に対するカーボン膜の密着性を向上させてパーティクルの発生を抑制する。

(もっと読む)

結晶積層構造体及びその製造方法

【課題】Ga2O3基板上の窒化物半導体層の上面の転位密度が低い結晶積層構造体、及びその製造方法を提供する。

【解決手段】一実施の形態において、Ga2O3基板2と、Ga2O3基板2上のAlxGayInzN(0≦x≦1、0≦y≦1、0≦z≦1、x+y+z=1)結晶からなるバッファ層3と、バッファ層3上の、酸素を不純物として含むAlxGayInzN(0≦x≦1、0≦y≦1、0≦z≦1、x+y+z=1)結晶からなる窒化物半導体層4と、を含む結晶積層構造体1を提供する。窒化物半導体層4のGa2O3基板2側の200nm以上の厚さの領域4aの酸素濃度は、1.0×1018/cm3以上である。

(もっと読む)

半導体製造装置及び製造方法

【課題】LEDまたはSiCデバイスのコスト低減のために、GaN、AlNまたはSiCバファー膜を大量に堆積できる装置、及び、GaNまたはSiCエピタキシャル層のストレスの低減法、基板形成方法を提供する。

【解決手段】縦型ホットウォールタイプのクリーニング用プラズマ手段つき、減圧CVDおよびリモートプラズマCVD装置によりデバイスのコストを低減する。基板のデバイス形成領域の周辺に深い溝を形成することで、GaNまたはSiCエピタキシャル層のストレスを低減する。さらに基板表面を異方性、等方性パターンをエッチングにより形成する基板形成する。LEDデバイス基板に関しては、その表面にSiO2パターンを形成し、マイクロチャネルエピタキシーによって良好なエピタキシャル膜を形成し、欠陥の少ない良好な膜を得るようにする。

(もっと読む)

半導体装置の製造方法、クリーニング方法および基板処理装置

【課題】クリーニングガスによる腐食反応を低減する。

【解決手段】CVD装置の処理炉10におけるマニホールド17と排気管20とクリーニングガス導入ノズル51と原料ガス導入ノズル31とに第一加熱源61と第二加熱源62と第三加熱源63と第四加熱源64とを敷設し、加熱源61〜64は温度制御部60に接続する。温度制御部60はマニホールド17と排気管20とクリーニングガス導入ノズル51と原料ガス導入ノズル31との温度をクリーニングガスが多層吸着しない程度の温度となるように制御する。クリーニングガスによる腐食反応を低減できるので、マニホールド17と排気管20とクリーニングガス導入ノズル51と原料ガス導入ノズル31の定期的交換の頻度を減少でき、CVD装置のメンテナンス性能を向上できる。

(もっと読む)

薄膜の形成方法及び成膜装置

【課題】比較的低温でも埋め込み特性が良好で且つ表面ラフネスの精度も向上するアモルファス状態の不純物含有のシリコン膜のような薄膜を形成することが可能な薄膜の形成方法を提供する。

【解決手段】真空排気が可能になされた処理容器内で被処理体Wの表面にシード膜88と不純物含有のシリコン膜90を形成する薄膜の形成方法において、処理容器内へアミノシラン系ガスと高次シランの内の少なくともいずれか一方のガスよりなるシード膜用原料ガスを供給してシード膜を形成する第1ステップと、処理容器内へシラン系ガスと不純物含有ガスとを供給してアモルファス状態の前記不純物含有のシリコン膜を形成する第2ステップとを有する。

(もっと読む)

基板処理装置及び半導体装置の製造方法

【課題】炉口部近傍に於ける基板温度の面内均一性を図ることで基板の処理枚数を増大させ、基板の処理効率を向上させる基板処理装置及び半導体装置の製造方法を提供する。

【解決手段】複数枚の基板13を保持する基板保持具5と、該基板保持具が搬入される処理炉1と、該処理炉に設けられ基板を加熱する加熱部2と、前記処理炉内に処理ガスを供給するガス供給部8,11と、前記処理炉内を排気する排気部12と、前記加熱部と前記ガス供給部と前記排気部とを制御する制御部とを具備し、前記基板保持具の下部にはダミー基板13bが保持されると共に、前記基板保持具の下端にボートキャップ6が設けられ、少なくともダミー基板と前記ボートキャップとの間に伝熱板34が設けられた。

(もっと読む)

半導体装置の製造方法および基板処理装置

【課題】異なるガスを交互に流して成膜して、スループットが向上できるようにする。

【解決手段】反応炉20、真空ポンプ26に接続された排気配管40、成膜に寄与する第1のガスを供給する第1供給配管41、第2のガスを供給する第2供給配管38、第1、第2供給配管の供給及び排気配管40の排気を制御するバルブ22〜25、第1供給配管41に設けられたガス溜り21、制御手段29を備える縦型半導体製造装置を使用して、制御手段によって、炉20の排気を止めた状態で第1のガスを炉20に供給することにより、炉20を昇圧状態として基板Wを第1のガスに晒す。ポンプ26で炉20を排気しつつ第2のガスを第2供給配管38を介して炉20に供給することにより、基板を第2のガスに晒す。

(もっと読む)

窒化物半導体基板及びその製造方法、並びにそれを用いた窒化物半導体発光素子

【課題】動作特性に優れた窒化物半導体発光素子を容易に得られる窒化物半導体基板を実現できるようにする。

【解決手段】窒化物半導体基板101は、基板110の主面上に形成された複数の成長阻害領域となるマスク膜120と、基板の主面におけるマスク膜から露出する領域の上に形成された複数の第1の窒化物半導体層111と、各第1の窒化物半導体層111の側面上にのみ成長により形成された複数の第2の窒化物半導体層112と、複数の第1の窒化物半導体層111及び複数の第2の窒化物半導体層112を覆うように成長により形成された第3の窒化物半導体層113とを有している。複数の第2の窒化物半導体層は、成長阻害領域の上において互いに隣り合う半導体層同士が接合しておらず、第3の窒化物半導体層は、第2の窒化物半導体層同士が互いに隣り合う領域において接合している。

(もっと読む)

化合物半導体装置及びその製造方法

【課題】電流コラプスを抑制しながらノーマリオフ動作を実現することができる化合物半導体装置及びその製造方法を提供する。

【解決手段】化合物半導体装置の一態様には、基板1と、基板1上方に形成された化合物半導体積層構造7と、化合物半導体積層構造上方に形成されたゲート電極11g、ソース電極11s及びドレイン電極11dと、が設けられている。化合物半導体積層構造7には、電子走行層3と、電子走行層3上方に形成された電子供給層5を含む窒化物半導体層と、が設けられている。窒化物半導体層の表面のIn組成は、平面視でゲート電極11gとソース電極11sとの間に位置する領域及びゲート電極11gとドレイン電極11dとの間に位置する領域において、ゲート電極11gの下方よりも低くなっている。

(もっと読む)

1 - 20 / 701

[ Back to top ]