Fターム[5F045AD15]の内容

気相成長(金属層を除く) (114,827) | 成膜条件−成膜温度 (8,040) | 1100≦T<1200℃ (776)

Fターム[5F045AD15]に分類される特許

1 - 20 / 776

発光ダイオード

発光ダイオード

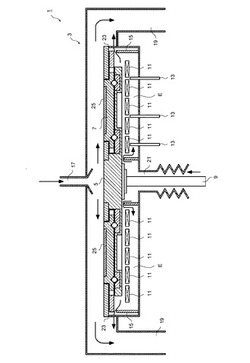

気相成長装置の抵抗加熱ヒータのパージ方法、気相成長装置

【課題】抵抗加熱ヒータとしてSiCヒータを用いてGaN薄膜を気相成長させる気相成長装置において、SiCヒータが窒化しないパージ方法、該パージ方法を適用した気相成長装置を提供する。

【解決手段】本発明に係る気相成長装置1における抵抗加熱ヒータのパージ方法は、基板25の加熱手段としてSiCヒータ11を用い、SiCヒータ11によって基板25の温度を1000℃以上に加熱して基板25に窒化物系化合物半導体膜を形成する気相成長装置におけるSiCヒータ11のパージ方法であって、SiCヒータ11をパージするパージガスとして、アルゴン、キセノン、またはこれらの混合ガスのいずれかを用いることを特徴とするものである。

(もっと読む)

シリコンエピタキシャルウェーハの製造方法

【課題】エピタキシャル成長の際の裏面クモリ及びピンハローを抑制して、高品質なシリコンエピタキシャルウェーハを製造することができる方法を提供することを目的とする。

【解決手段】チャンバー内に配設されたサセプタのウェーハ載置面上にシリコン単結晶基板を載置して、該シリコン単結晶基板上にエピタキシャル成長させることによりシリコンエピタキシャルウェーハを製造する方法であって、前記シリコン単結晶基板を載置する前に、前記チャンバー内にシリコン原料ガスを流入させながら、50秒を超えて300秒以下の時間で、前記サセプタのウェーハ載置面上にポリシリコン膜を被覆し、その後前記サセプタのウェーハ載置面上に前記シリコン単結晶基板を載置してエピタキシャル成長させるシリコンエピタキシャルウェーハの製造方法。

(もっと読む)

窒化物半導体層を成長させるためのバッファ層構造を有する基板とその製造方法

【課題】窒化物半導体デバイス用の半導体積層構造を成長させるために改善されたバッファ層構造を有する基板を提供する。

【解決手段】窒化物半導体層を成長させるためのバッファ層構造を有する基板は、Si単結晶基板の(111)主面上に形成された窒化ケイ素層、この窒化ケイ素層上に堆積されたAlN結晶層、およびこのAlN層上に堆積された複数のAlxGa1−xN(1>x>0)結晶層を含み、これら複数のAlxGa1−xN結晶層においてはその下層に比べて上層ほど小さなAl組成比xを有しており、複数のAlxGa1−xN層結晶中の一層は非晶質と結晶質が混在するAlN中間層を含んでいる。

(もっと読む)

半導体発光素子

【課題】キャリア密度に疎密を設けて全体として発光効率を向上させた半導体発光素子を提供する。

【解決手段】半導体発光素子10では、半導体発光層15は第1導電型の第1半導体層12と第2導電型の第2半導体層14の間に設けられている。網目状の第1電極16は、半導体発光層15と反対側の第1半導体層12上に設けられている。ドット状の第2電極18aは、半導体発光層15と反対側の第2半導体層14上に、第2半導体層14の表面に対して平行な平面視で第1電極16の網目の中心と重なるように設けられている。

(もっと読む)

スループットを改善しウェハダメージを低減するサセプタ

【課題】内部スペースを有する加熱されたチャンバー内において半導体ウェハを支持するサセプタに関する。

【解決手段】当該サセプタ10は、上面24、および当該上面24と反対の下面26を有する本体20を備える。当該サセプタ10は、当該上面24から当該本体20に仮想の中央軸22に沿って下方に延びる凹部を有する。当該凹部はその中に半導体ウェハ12を受容することができる大きさおよび形状に形成されている。当該サセプタ10は、当該本体20を貫通し凹部から下面26まで延びる複数のリフトピン開口部を有する。複数のリフトピン開口部のそれぞれは、ウェハを凹部に対して選択的に上昇または下降させるため、リフトピンを受容することができる大きさに形成されている。サセプタ10は、本体20から中央軸22に沿って凹部から下面26まで延びる中央開口部を有する。

(もっと読む)

成膜装置

【課題】サセプタからの熱逃げが抑制され、かつサセプタ支持部材の熱による破損を防止できる成膜装置を提供する。

【解決手段】

ヒーター23によってサセプタ21を加熱し、原料ガス導入部13から真空槽11内に原料ガスを導入し、サセプタ21の板部21aの表面に配置された基板51に薄膜を形成する成膜装置10であって、サセプタ21の筒部21bの端部とサセプタ支持部材31との間には、サセプタ21とは別の材質である熱抵抗部材22が配置されており、サセプタ21の熱が熱抵抗部材22で遮られてサセプタ支持部材31に伝わりづらくなっている。

(もっと読む)

結晶積層構造体及びその製造方法

【課題】Ga2O3基板上の窒化物半導体層の上面の転位密度が低い結晶積層構造体、及びその製造方法を提供する。

【解決手段】一実施の形態において、Ga2O3基板2と、Ga2O3基板2上のAlxGayInzN(0≦x≦1、0≦y≦1、0≦z≦1、x+y+z=1)結晶からなるバッファ層3と、バッファ層3上の、酸素を不純物として含むAlxGayInzN(0≦x≦1、0≦y≦1、0≦z≦1、x+y+z=1)結晶からなる窒化物半導体層4と、を含む結晶積層構造体1を提供する。窒化物半導体層4のGa2O3基板2側の200nm以上の厚さの領域4aの酸素濃度は、1.0×1018/cm3以上である。

(もっと読む)

エピタキシャルウエーハの製造方法

【課題】 本発明は、気相成長前の昇温時間を短縮でき、ウォールデポの付着を少なくできるエピタキシャルウエーハの製造方法を提供することを目的とする。

【解決手段】 チャンバー内にウェーハを載置するサセプタを具備するコールドウォールタイプの気相成長装置を用いて、前記サセプタ上に載置されたウェーハの主表面にエピタキシャル層を気相成長させてエピタキシャルウエーハを製造する方法であって、

前記気相成長前の昇温時に、前記サセプタを前記チャンバー内壁に近づけ、該チャンバー内壁の温度を上昇させた後に、前記サセプタをもとの位置に戻し、その後、前記気相成長を行い、エピタキシャルウエーハを製造することを特徴とするエピタキシャルウエーハの製造方法。

(もっと読む)

窒化物半導体ウェーハ、窒化物半導体装置及び窒化物半導体結晶の成長方法

【課題】シリコン基板上に形成した、転位及びクラックの少ない窒化物半導体ウェーハ、窒化物半導体装置及び窒化物半導体結晶の成長方法を提供する。

【解決手段】実施形態によれば、シリコン基板と、その上に順次設けられた、下側歪緩和層、中間層、上側歪緩和層及び機能層と、を有する窒化物半導体ウェーハが提供される。中間層は、第1下側層と、第1ドープ層と、第1上側層と、を含む。第1下側層は、下側歪緩和層の上に設けられ下側歪緩和層の格子定数よりも大きい格子定数を有する。第1ドープ層は、第1下側層の上に設けられ第1下側層の格子定数以上の格子定数を有し1×1018cm−3以上1×1021cm−3未満の濃度であり第1下側層よりも高い濃度で不純物を含有する。第1上側層は、第1ドープ層の上に設けられ第1ドープ層の格子定数以上で第1下側層の格子定数よりも大きい格子定数を有する。

(もっと読む)

炭化珪素基板、半導体装置及び配線基板

【課題】電子素子等のデバイスを実装するには、炭化珪素基板の高周波損失が大きく、実際には電子素子を炭化珪素基板に実装できなかった。

【解決手段】20GHzにおける高周波損失が2.0dB/mm以下の炭化珪素基板であれば、電子素子を実装して十分に動作させることができることを見出し、2.0dB/mm以上の高周波損失特性を有する炭化珪素基板を2000℃以上で加熱する。この熱処理により20GHzにおける高周波損失を2.0dB/mm以下にすることができた。また、ヒーターに窒素を流さないで、CVDにより炭化珪素基板を作製することによって高周波損失を2.0dB/mm以下にすることができた。

(もっと読む)

エピタキシャルウェーハの製造方法及びエピタキシャルウェーハ

【課題】より急峻且つより安定したSRプロファイルを有するエピタキシャルウェーハを製造することのできる技術を提供する。

【解決手段】不純物を含有するシリコン単結晶の基板Sの直上に、基板Sよりも不純物濃度が低い第1層を気相成長させる第1成長工程(1st Growth工程)と、第1層よりも上に第2層を気相成長させる第2成長工程(2nd Growth工程)とを有するエピタキシャルウェーハの製造方法であって、第1成長工程において、強制的に排気を行って常圧AP以下の第1圧力RPの下で気相成長させ、第2成長工程において、第1圧力RPより高い第2圧力APの下で気相成長させるようにする。

(もっと読む)

半導体装置の製造方法及び半導体装置

【課題】オン抵抗を増加させることなく、ノーマリーオフとなる半導体装置を提供する。

【解決手段】基板11の上に、第1の半導体層14、第2の半導体層15及びp型の不純物元素が含まれている半導体キャップ層16を順次形成する工程と、前記半導体キャップ層を形成した後、開口部を有する誘電体層21を形成する工程と、前記開口部において露出している前記半導体キャップ層の上に、p型の不純物元素が含まれている第3の半導体層17を形成する工程と、前記第3の半導体層の上にゲート電極31を形成する工程と、を有することを特徴とする半導体装置の製造方法により上記課題を解決する。

(もっと読む)

化合物半導体装置及びその製造方法

【課題】ノーマリオフ動作を実現しながら良好な伝導性能を得ることができる化合物半導体装置及びその製造方法を提供する。

【解決手段】化合物半導体装置の一態様には、基板1と、基板1上方に形成された電子走行層3及び電子供給層5と、電子供給層5上方に形成されたゲート電極11g、ソース電極11s及びドレイン電極11dと、電子供給層5とゲート電極11gとの間に形成されたp型半導体層8と、電子供給層5とp型半導体層8との間に形成され、電子供給層5よりもバンドギャップが大きい正孔障壁層6と、が設けられている。

(もっと読む)

化合物半導体装置及びその製造方法

【課題】耐圧をより向上することができる化合物半導体装置及びその製造方法を提供する。

【解決手段】化合物半導体装置の一態様には、基板1と、基板1の上方に形成された化合物半導体積層構造8と、基板1と化合物半導体積層構造8との間に形成された非晶質性絶縁膜2と、が設けられている。

(もっと読む)

化合物半導体装置及びその製造方法

【課題】電流コラプスを抑制しながらノーマリオフ動作を実現することができる化合物半導体装置及びその製造方法を提供する。

【解決手段】化合物半導体装置の一態様には、基板1と、基板1上方に形成された化合物半導体積層構造7と、化合物半導体積層構造上方に形成されたゲート電極11g、ソース電極11s及びドレイン電極11dと、が設けられている。化合物半導体積層構造7には、電子走行層3と、電子走行層3上方に形成された電子供給層5を含む窒化物半導体層と、が設けられている。窒化物半導体層の表面のIn組成は、平面視でゲート電極11gとソース電極11sとの間に位置する領域及びゲート電極11gとドレイン電極11dとの間に位置する領域において、ゲート電極11gの下方よりも低くなっている。

(もっと読む)

半導体装置

【課題】格子整合したバッファ層、及び高い平坦性を有する接合界面を得ることが可能な半導体装置を提供すること。

【解決手段】本発明は、n−GaNからなる基板10と、基板10上に設けられ、InxAl1−xN(0.15≦x≦0.2)からなる第1バッファ層12と、第1バッファ層12上に設けられ、厚さ1nm以上10nm以下のAlNからなるスペーサ層14と、スペーサ層14上に設けられ、GaNからなるチャネル層16と、チャネル層16上に設けられ、窒化物半導体からなる電子供給層18と、を具備する半導体装置である。

(もっと読む)

窒化物半導体層を成長させるためのバッファ層構造を有する基板の製造方法

【課題】窒化物半導体デバイス用の半導体積層構造を成長させるために改善されたバッファ層構造を有する基板を製造する方法を提供する。

【解決手段】窒化物半導体層を成長させるためのバッファ層構造を有する基板の製造方法は、Si単結晶基板(1)の(111)主面上において600℃以上900℃以下の範囲内の基板温度で第1のAlNバッファ層(2a)を堆積させ、この第1のAlNバッファ層上において900℃を超える基板温度で第2のAlNバッファ層(2b)を堆積させることを含む。

(もっと読む)

半導体基板の製造方法

【課題】シリコンウェハ等のベース基板上方に窒化物半導体からなる半導体結晶層を形成する場合に、当該半導体結晶層の転位密度を低減する。

【解決手段】ベース基板をエピタキシャル結晶成長装置の成長室に設置した後、ベース基板の上に、接着層、バッファ層および活性層をエピタキシャル成長法により順次形成する層形成工程を有し、接着層形成工程が、第1結晶層を形成する工程と第2結晶層を形成する工程と、を有し、第1結晶層の形成後であって第2結晶層の形成前の第1の段階、および、第2結晶層の形成後であってバッファ層の形成前の第2の段階、からなる群から選択された少なくとも1つの段階において、3族原料ガスの供給を停止するとともに成長室の内部を、アンモニアを含むガスの雰囲気に一定時間だけ維持する雰囲気維持工程を有する半導体基板の製造方法を提供する。

(もっと読む)

1 - 20 / 776

[ Back to top ]