Fターム[5F045AE23]の内容

気相成長(金属層を除く) (114,827) | 成膜条件−成膜時の圧力 (3,707) | 減圧(圧力が明示されていない) (3,333) | 7.6≦P<76Torr(0.01≦P<0.1気圧 10.13≦P<101.3hPa) (552)

Fターム[5F045AE23]に分類される特許

1 - 20 / 552

加熱装置及びこれを用いた半導体気相成長装置

太陽電池の製造装置、太陽電池、及び太陽電池の製造方法

成膜装置

半導体装置およびその製造方法

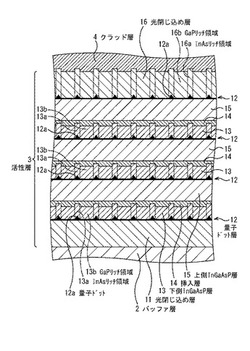

光半導体素子及びその製造方法

【課題】高い光利得を得ながら閾値電流値を低減することができる光半導体素子及びその製造方法を提供する。

【解決手段】基板の上方に形成された複数の量子ドット層12と、複数の量子ドット層12間に位置する中間層と、が設けられている。量子ドット層12に含まれる量子ドット12aの組成が、InxGa1-xAsySb1-y(0<x≦1、0<y≦1)で表わされる。中間層には、組成がInaGa1-aAsbP1-b(0<a<1、0<b<1)で表わされ、厚さが10nm以上40nm以下のInGaAsP層13、15と、InGaAsP層13、15の底面から10nm以上40nm未満の高さに位置し、厚さが0.3nm以上2nm以下のInP層14と、が含まれている。

(もっと読む)

成膜装置

【課題】

従来に比べて製造が容易であり、かつ基板に向けて原料ガスを均一に供給することのできる成膜装置を提供する。

【解決手段】

本発明に係る薄膜を形成する成膜装置は、基板4を配置している第一電極3と、基板4に対向しかつ高周波電圧が印加される第二電極2とを備えており、第二電極2は、基板4に対向する面にシャワー板9を有しているとともに、シャワー板9の基板4に対向する面に一枚のメッシュ板10を有しており、シャワー板9は、原料ガスを通過させる複数の孔9aを有しており、メッシュ板10は、シャワー板9の孔9aを通過した原料ガス5を通過させるためのメッシュ構造を有し、メッシュ板10と基板4との間にプラズマが発生する空間を設けたことを特徴とする。

(もっと読む)

半導体装置の製造方法、基板処理方法、基板処理装置およびプログラム

【課題】低温領域において適正な特性を有するSiC系の膜を形成できる半導体装置の製造方法、基板処理方法,基板処理装置およびプログラムを提供する。

【解決手段】基板を処理室内に収容する工程と、加熱された処理室内へ有機シリコン系ガスを供給して基板上にシリコンおよび炭素を含む膜を形成する工程と、を有し、シリコンおよび炭素を含む膜を形成する工程は、処理室内へ有機シリコン系ガスを供給して、有機シリコン系ガスを処理室内に封じ込める工程と、有機シリコン系ガスを処理室内に封じ込めた状態を維持する工程と、処理室内を排気する工程と、を含むサイクルを所定回数行う。

(もっと読む)

III/V半導体

【課題】SiあるいはGaP技術をベースとする集積回路にモノリシックに集積化される、新しいIII/V半導体を用いた、発光ダイオードおよびレーザダイオードの半導体構造及び製造方法、あるいはまた、モジュレータ構造および検出器構造への使用法を提供する。

【解決手段】ドープされたSiあるいはドープされたGaPをベースとするキャリア層A、およびそこに配設されたIII/V半導体Dを備え、組成GaxInyNaAsbPcSbdを有するモノリシック集積回路構造であって、ここで、x=70−100モル−%、y=0−30モル−%、a=0.5−15モル−%、b=67.5−99.5モル−%、c=0−32.0モル−%およびd=0−15モル−%、xとyの合計は、常に100モル−%であり、a、b、cおよびdの合計は、常に100モル−%であり、そして、一方のxとyの合計と他方のaないしdの合計の比率は、実質的に1:1である。

(もっと読む)

半導体装置の製造方法

【課題】本発明は、基板に元々付着していた不純物及び成長炉内の不純物を低減することができる半導体装置の製造方法を提供することを目的とする。

【解決手段】本発明に係る半導体装置の製造方法は、基板を成長炉内に搬入する搬入工程と、該基板の上と該成長炉の内壁に、該基板表面と該成長炉内の不純物を吸収する不純物吸収層を形成する吸収層形成工程と、該不純物吸収層と、該基板の一部とをエッチングすることで該基板を薄化基板にするエッチング工程と、該薄化基板の上にバッファ層を形成するバッファ層形成工程と、該バッファ層の上に半導体層を形成する半導体層形成工程と、を備えたことを特徴とする。

(もっと読む)

半導体装置の製造方法、クリーニング方法および基板処理装置

【課題】クリーニングガスによる腐食反応を低減する。

【解決手段】CVD装置の処理炉10におけるマニホールド17と排気管20とクリーニングガス導入ノズル51と原料ガス導入ノズル31とに第一加熱源61と第二加熱源62と第三加熱源63と第四加熱源64とを敷設し、加熱源61〜64は温度制御部60に接続する。温度制御部60はマニホールド17と排気管20とクリーニングガス導入ノズル51と原料ガス導入ノズル31との温度をクリーニングガスが多層吸着しない程度の温度となるように制御する。クリーニングガスによる腐食反応を低減できるので、マニホールド17と排気管20とクリーニングガス導入ノズル51と原料ガス導入ノズル31の定期的交換の頻度を減少でき、CVD装置のメンテナンス性能を向上できる。

(もっと読む)

薄膜の形成方法及び成膜装置

【課題】比較的低温でも埋め込み特性が良好で且つ表面ラフネスの精度も向上するアモルファス状態の不純物含有のシリコン膜のような薄膜を形成することが可能な薄膜の形成方法を提供する。

【解決手段】真空排気が可能になされた処理容器内で被処理体Wの表面にシード膜88と不純物含有のシリコン膜90を形成する薄膜の形成方法において、処理容器内へアミノシラン系ガスと高次シランの内の少なくともいずれか一方のガスよりなるシード膜用原料ガスを供給してシード膜を形成する第1ステップと、処理容器内へシラン系ガスと不純物含有ガスとを供給してアモルファス状態の前記不純物含有のシリコン膜を形成する第2ステップとを有する。

(もっと読む)

炭化珪素基板、半導体装置及び配線基板

【課題】電子素子等のデバイスを実装するには、炭化珪素基板の高周波損失が大きく、実際には電子素子を炭化珪素基板に実装できなかった。

【解決手段】20GHzにおける高周波損失が2.0dB/mm以下の炭化珪素基板であれば、電子素子を実装して十分に動作させることができることを見出し、2.0dB/mm以上の高周波損失特性を有する炭化珪素基板を2000℃以上で加熱する。この熱処理により20GHzにおける高周波損失を2.0dB/mm以下にすることができた。また、ヒーターに窒素を流さないで、CVDにより炭化珪素基板を作製することによって高周波損失を2.0dB/mm以下にすることができた。

(もっと読む)

半導体装置の製造方法及び半導体装置

【課題】オン抵抗を増加させることなく、ノーマリーオフとなる半導体装置を提供する。

【解決手段】基板11の上に、第1の半導体層14、第2の半導体層15及びp型の不純物元素が含まれている半導体キャップ層16を順次形成する工程と、前記半導体キャップ層を形成した後、開口部を有する誘電体層21を形成する工程と、前記開口部において露出している前記半導体キャップ層の上に、p型の不純物元素が含まれている第3の半導体層17を形成する工程と、前記第3の半導体層の上にゲート電極31を形成する工程と、を有することを特徴とする半導体装置の製造方法により上記課題を解決する。

(もっと読む)

化合物半導体装置及びその製造方法

【課題】ノーマリオフ動作を実現しながら良好な伝導性能を得ることができる化合物半導体装置及びその製造方法を提供する。

【解決手段】化合物半導体装置の一態様には、基板1と、基板1上方に形成された電子走行層3及び電子供給層5と、電子供給層5上方に形成されたゲート電極11g、ソース電極11s及びドレイン電極11dと、電子供給層5とゲート電極11gとの間に形成されたp型半導体層8と、電子供給層5とp型半導体層8との間に形成され、電子供給層5よりもバンドギャップが大きい正孔障壁層6と、が設けられている。

(もっと読む)

シリコン酸化膜の形成方法およびその形成装置

【課題】ボイドやシームの発生を抑制することができるシリコン酸化膜の形成方法およびその形成装置を提供する。

【解決手段】シリコン酸化膜の形成方法は、半導体ウエハ10にシリコンプリカーサと過酸化水素とを含む成膜用ガスを供給して、半導体ウエハ10の溝を埋め込むようにシリコン酸化膜を成膜する。制御部100は、反応管2内に複数の半導体ウエハ10を収容し、反応管2内を113Pa〜6650Paに設定する。また、制御部100は、過酸化水素の流量をシリコンプリカーサの流量の3倍〜20倍に設定する。

(もっと読む)

化合物半導体装置及びその製造方法

【課題】電流コラプスを抑制しながらノーマリオフ動作を実現することができる化合物半導体装置及びその製造方法を提供する。

【解決手段】化合物半導体装置の一態様には、基板1と、基板1上方に形成された化合物半導体積層構造7と、化合物半導体積層構造上方に形成されたゲート電極11g、ソース電極11s及びドレイン電極11dと、が設けられている。化合物半導体積層構造7には、電子走行層3と、電子走行層3上方に形成された電子供給層5を含む窒化物半導体層と、が設けられている。窒化物半導体層の表面のIn組成は、平面視でゲート電極11gとソース電極11sとの間に位置する領域及びゲート電極11gとドレイン電極11dとの間に位置する領域において、ゲート電極11gの下方よりも低くなっている。

(もっと読む)

化合物半導体装置及びその製造方法

【課題】耐圧をより向上することができる化合物半導体装置及びその製造方法を提供する。

【解決手段】化合物半導体装置の一態様には、基板1と、基板1の上方に形成された化合物半導体積層構造8と、基板1と化合物半導体積層構造8との間に形成された非晶質性絶縁膜2と、が設けられている。

(もっと読む)

半導体基板および半導体基板の製造方法

【課題】シリコンウェハ等のベース基板上方に窒化物半導体からなる半導体結晶層を形成する場合に、当該半導体結晶層の転位密度を低減する。

【解決手段】ベース基板、接着層、バッファ層および活性層を有し、前記ベース基板、前記接着層、前記バッファ層および前記活性層がこの順に位置し、前記ベース基板の前記接着層と接する領域にSiが存在し、前記接着層、前記バッファ層および前記活性層が、窒化物半導体からなる半導体基板であって、前記バッファ層が、第1結晶層と第2結晶層が交互に複数積層された積層構造体であり、前記第1結晶層が、AlmGa1−mN、(但し0≦m≦1)で表される結晶からなり、前記第2結晶層が、AlnGa1−nN、(但し0≦n≦1、m>n)で表される結晶からなり、前記第1結晶層の格子緩和度が、前記第2結晶層の格子緩和度より大きい半導体基板を提供する。

(もっと読む)

半導体基板の製造方法

【課題】シリコンウェハ等のベース基板上方に窒化物半導体からなる半導体結晶層を形成する場合に、当該半導体結晶層の転位密度を低減する。

【解決手段】ベース基板、接着層、バッファ層および活性層がこの順に位置し、前記ベース基板の前記接着層と接する領域にSiが存在し、前記接着層、前記バッファ層および前記活性層が、窒化物半導体からなる半導体基板の製造方法であって、前記ベース基板をエピタキシャル結晶成長装置の成長室に設置した後に、前記ベース基板の温度を1000℃以上に維持しつつ前記ベース基板の表面をアンモニアガスとキャリアガスとの混合ガスに暴露するアンモニアガス暴露工程と、前記アンモニアガス暴露工程の後に、前記ベース基板の上に、前記接着層、前記バッファ層および前記活性層をエピタキシャル成長法により順次形成する層形成工程と、を有する半導体基板の製造方法を提供する。

(もっと読む)

半導体装置の製造方法、及び基板処理装置

【課題】基板に形成された高いアスペクト比の素子分離溝でも、空洞の発生を抑制して当該溝中にシリコン絶縁膜を埋め込むこと。

【解決手段】高いアスペクト比の素子分離溝が形成された基板を処理室に搬入する基板搬入工程と、前記処理室を第一ガスであるヘキサメチルジシラザン(HMDS)含有ガス雰囲気にするシリコン含有ガス雰囲気工程と、前記処理室を第二ガスであるパージガス雰囲気にする第一パージガス雰囲気工程と、前記処理室を第三ガスである酸素ガスであってプラズマ状態の酸素含有ガス雰囲気にする酸素含有ガス雰囲気工程と、前記処理室を第二ガスであるパージガス雰囲気にする第二パージガス雰囲気工程と、前記シリコン含有ガス雰囲気工程、前記第一パージガス雰囲気工程、前記酸素含有ガス雰囲気工程、及び前記第二パージガス雰囲気工程を繰り返す工程と、を有する半導体装置の製造方法、及びそれを実現する基板処理装置である。

(もっと読む)

1 - 20 / 552

[ Back to top ]