Fターム[5F045AF12]の内容

気相成長(金属層を除く) (114,827) | 被成膜面の組成、基板の特徴、ダミー基板、マスク (7,328) | 基板の形状、構造、大きさ、厚み等 (845) | 基板表面の状態(面粗さ、ステップ等) (699)

Fターム[5F045AF12]の下位に属するFターム

結晶方位(面方位)オリフラ、ノッチ (341)

膜形成の核を被成膜面上に有するもの (67)

Fターム[5F045AF12]に分類される特許

1 - 20 / 291

発光ダイオード

基板の製造方法

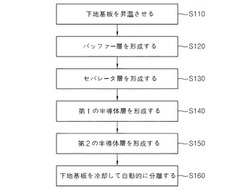

【課題】基板の製造方法の提供。

【解決手段】下地基板を反応炉内に搬入するステップと、下地基板の上にバッファー層を形成するステップと、バッファー層の上にセパレータ層を形成するステップと、セパレータ層の上に少なくとも二つの温度で半導体層を形成するステップと、下地基板を反応炉から搬出して自然冷却によってセパレータ層を中心に下地基板と半導体層を分離するステップとを含む基板の製造方法。

(もっと読む)

窒化物半導体成長用基板及びその製造方法、窒化物半導体エピタキシャル基板、並びに窒化物半導体素子

【課題】低転位密度の窒化物半導体を成長することが可能な窒化物半導体成長用基板及びその製造方法、並びに窒化物半導体成長用基板を用いて作製される窒化物半導体エピタキシャル基板及び窒化物半導体素子を提供する。

【解決手段】サファイア基板のC面である主面に、前記主面に対して90°未満で傾斜した側面を有する錐状または錐台状の凸部が格子状に配置して形成されており、前記主面からの前記凸部の高さが0.5μm以上3μm以下で、隣接する前記凸部間の距離が1μm

以上6μm以下であって、前記凸部の前記側面の表面粗さRMSが10nm以下である窒化物半導体成長用基板である。

(もっと読む)

半導体製造装置及び製造方法

【課題】LEDまたはSiCデバイスのコスト低減のために、GaN、AlNまたはSiCバファー膜を大量に堆積できる装置、及び、GaNまたはSiCエピタキシャル層のストレスの低減法、基板形成方法を提供する。

【解決手段】縦型ホットウォールタイプのクリーニング用プラズマ手段つき、減圧CVDおよびリモートプラズマCVD装置によりデバイスのコストを低減する。基板のデバイス形成領域の周辺に深い溝を形成することで、GaNまたはSiCエピタキシャル層のストレスを低減する。さらに基板表面を異方性、等方性パターンをエッチングにより形成する基板形成する。LEDデバイス基板に関しては、その表面にSiO2パターンを形成し、マイクロチャネルエピタキシーによって良好なエピタキシャル膜を形成し、欠陥の少ない良好な膜を得るようにする。

(もっと読む)

窒化物半導体構造の製造方法

【課題】平坦な表面を有し、結晶性の高い窒化物半導体下地層を、反りを抑えて、大きな成長速度で成長させることができる窒化物半導体構造の製造方法を提供する。

【解決手段】第3の窒化物半導体下地層を形成する工程において、第3の窒化物半導体下地層の成長時に単位時間当たりに供給されるV族原料ガスのモル量と単位時間当たりに供給されるIII族原料ガスのモル量との比であるV/III比を700以下とし、第3の窒化物半導体下地層の成長時の圧力を26.6kPa以上とし、第3の窒化物半導体下地層の成長速度を2.5μm/時以上とする、窒化物半導体構造の製造方法である。

(もっと読む)

GaN系化合物半導体の成長方法及び成長層付き基板

【目的】

GaN系化合物半導体成長層に生じる歪が低減されるとともに、当該結晶成長層にダメージを与えることなくSi基板から結晶成長層を容易に分離することが可能なGaN系化合物半導体の成長方法及び成長層付き基板を提供する。

【解決手段】

Si基板上にコラム状結晶層を成長する工程と、上記コラム状結晶層上に島状成長又は網目状成長の窒化アルミニウム(AlN)結晶層であるバッファ層を成長する工程と、上記バッファ層上にGaN系化合物結晶を成長する工程と、を有する。

(もっと読む)

SiCエピタキシャルウエハおよびそれを用いたSiC半導体素子

【課題】高品質かつ高信頼性の素子を作製できるSiCエピタキシャルウエハ、およびそれを用いて得られるSiC半導体素子を提供すること

【解決手段】4°以下のオフ角を有するSiC基板2と、SiC基板2の主面4に形成され、その表面10に0.5nm以上の高さのステップバンチング9が形成されたSiCエピタキシャル層3とを含むSiCエピタキシャルウエハ1において、ステップバンチング9の線密度を40cm−1以下にする。

(もっと読む)

窒化物半導体テンプレート及び発光ダイオード

【課題】低抵抗(表面比抵抗が20Ω/□以下)であり、結晶性が良好(XRD半値幅が50秒以上100秒以下)な窒化物半導体テンプレート、及びそれを用いた発光ダイオードを提供する。

【解決手段】窒化物半導体テンプレート10は、基板11と、基板11上にO(酸素)が添加されたO添加層としてOドープGaN層13を形成し、OドープGaN層13上にSiが添加されたSi添加層としてのSiドープGaN層14を形成してなるIII族窒化物半導体層22とを備え、III族窒化物半導体層の全体の膜厚が4μm以上10μm以下であり、SiドープGaN層14におけるSiの平均キャリア濃度が1×1018cm-3以上5×1018cm-3以下である。

(もっと読む)

ダイヤモンド複合体

【課題】単結晶ダイヤモンドと多結晶ダイヤモンドの双方の利点を活かしながら、更に板状の構造を可能にするために、多結晶ダイヤモンドの研磨の困難性も回避し、研磨が容易なダイヤモンド複合体を提供すること。

【解決手段】少なくとも2種類の結晶性の異なる結晶からなる構造の複合体であり、その内の第一の結晶は高圧合成法により合成した単結晶ダイヤモンドか、あるいは気相合成法により合成した単結晶ダイヤモンドであり、第二の結晶は欠陥を面内に周期的なパターン形状で含む気相合成法により合成したダイヤモンドであり、該第一の結晶及び第二の結晶はいずれも、主面が平行になるように層状に形成されていることを特徴とするダイヤモンド複合体。

(もっと読む)

SiCエピタキシャルウェハ及びその製造方法

【課題】積層欠陥の面密度が低減されたSiCエピタキシャルウェハ及びその製造方法を提供する。

【解決手段】本発明のSiCエピタキシャルウェハの製造方法は、オフ角を有するSiC単結晶基板の成長面に存在する基底面転位(BPD)のうち、SiC単結晶基板上に形成された、所定膜厚のSiCエピタキシャル膜において積層欠陥になる比率を決定する工程と、比率に基づいて、使用するSiC単結晶基板の成長面におけるBPDの面密度の上限を決定する工程と、上限以下のSiC単結晶基板を用いて、比率を決定する工程において用いたエピタキシャル膜の成長条件と同じ条件で、SiC単結晶基板上にSiCエピタキシャル膜を形成する工程と、を有することを特徴とする。

(もっと読む)

半導体発光素子、及びその製造方法

【課題】転位密度の低減を図ることができる半導体発光素子、及びその製造方法を提供することである。

【解決手段】実施形態に係る半導体発光素子は、基板と、前記基板の第1の主面の側に設けられた第1の半導体層と、前記第1の半導体層の上に設けられた発光層と、前記発光層の上に設けられた第2の半導体層と、を備えている。そして、前記基板の第1の主面には、頂部に凹部を有する突起部が複数設けられている。

(もっと読む)

基板処理方法および基板処理装置

【課題】シリコン酸化膜の除去後、シリコンゲルマニウム膜の形成までのQタイムを長くするとともに、シリコンゲルマニウム膜の形成におけるプリベイクの温度を低くする。

【解決手段】基板処理装置1では、酸化膜除去部4にて基板9の一の主面上のシリコン酸化膜が除去された後、シリル化処理部6にてシリル化材料を付与して、当該主面に対してシリル化処理が施される。これにより、シリコン酸化膜の除去後、シリコンゲルマニウム膜の形成までのQタイムを長くするとともに、シリコンゲルマニウム膜の形成におけるプリベイクの温度を低くすることができる。

(もっと読む)

半導体装置を形成するための方法

【課題】 半導体装置の形成のための方法が提供される。

【解決手段】 本方法は、プロセスチャンバ内の基板ホルダ上に基板を準備し、前記基板が、上部表面と側壁表面を持つ立ち上がり構造を含み;前記プロセスチャンバ内にプロセスガスを流し、前記プロセスガスが炭化水素ガス、酸素含有ガス、及び場合によりアルゴン又はヘリウムを含む。本方法はさらに、プロセスチャンバ内のプロセスガス圧力を少なくとも1トールに維持し、マイクロ波プラズマ源を用いてプロセスガスからプラズマを形成し、及び基板をプラズマに暴露して共形アモルファスカーボンフィルムを前記立ち上がり構造の表面上に堆積させることを含む。

(もっと読む)

六角棒状GaN系半導体結晶およびその製造方法

【課題】六角棒状GaN系半導体結晶の新規な製造方法を提供する。

【解決手段】GaN系半導体からなり、m面である表面を有する下地結晶10の前記表面上に、前記下地結晶10のc軸に沿って延びる複数のストライプ22を含むマスク20を形成する工程と、前記マスク22が形成された前記表面の上にGaN系半導体結晶30をエピタキシャル成長させる工程と、を含む六角棒状GaN系半導体結晶の製造方法において、GaN系半導体結晶30は下地結晶10の露出面15から成長し始め、マスク20と略同じ厚さのGaN系半導体結晶膜40がまず形成される。更にGaN系半導体結晶30を成長させ続けると、GaN系半導体結晶膜40の上に六角棒状GaN系半導体結晶30が形成される。

(もっと読む)

窒化物半導体基板の製造方法

【課題】簡易かつ効果的に、窒化物半導体の絶縁破壊電圧低下が低減された窒化物半導体基板の製造方法を提供する。

【解決手段】シリコン単結晶基板の一主面上に窒化ケイ素層を形成する工程と、前記窒化ケイ素層上に窒化物半導体からなる中間層を形成する工程と、前記中間層上に窒化物半導体からなる活性層を形成する工程と、を含む窒化物半導体基板の製造方法であって、前記窒化ケイ素層を形成する工程は、窒素ガスが90vol%以上100vol%以下で残部は前記窒素ガス以外の不活性ガスからなるガス雰囲気にて室温から900℃以上1000℃以下の到達温度まで昇温する第1ステップと、前記ガス雰囲気と前記到達温度のままで所定時間保持する第2ステップと、その後還元性ガス含有雰囲気に切り替えて所定時間保持する第3ステップと、からなることを特徴とする窒化物半導体基板の製造方法。

(もっと読む)

半導体発光素子の製造方法

【課題】簡単な工程で光抽出効率を向上させた半導体発光素子の製造方法を提供する。

【解決手段】本発明の半導体発光素子の製造方法は、互いに対向する第1及び第2の主面を有する基板を設ける段階と、基板の第1の主面に柱状を有する複数の凸部を形成する段階と、凸部が形成された第1の主面上に第1の導電型半導体層、活性層、及び第2の導電型半導体層を含む発光積層体を形成する段階と、発光積層体のうちの凸部の周囲の溝部に対応する領域に形成された部分を除去して複数の発光構造物を形成する段階と、基板上に形成された複数の発光構造物から個別素子が得られるように溝部に沿って基板を分離する段階と、を有する。

(もっと読む)

窒化ガリウム基板、発光素子、電界効果トランジスタ及びエピタキシャル膜の製造方法

【課題】特定の一部の領域にのみ加工歪みが存在する場合であっても、短時間で容易に歪みを評価することのできる方法による評価の結果合格した窒化ガリウム基板、その窒化ガリウム基板を含む発光素子もしくは電界効果トランジスタ、及びそのガリウム基板上に結晶を成長させるエピタキシャル膜の製造方法を提供する。

【解決手段】本発明の一態様によれば、窒化ガリウム基板1のバンドギャップに対応する波長のフォトルミネッセンスピーク強度を、窒化ガリウム基板1の表面の測定範囲3内において1mm×1mmの正方形の測定領域2ごとに測定したときの、全測定領域2におけるフォトルミネッセンスピーク強度の最小値が平均値の45%以上であり、測定領域2は測定範囲3内に隙間無く連続する、窒化ガリウム基板1が提供される。

(もっと読む)

半極性(Al,In,Ga,B)NまたはIII族窒化物の結晶

【課題】故意にミスカットした基板を用いることにより、半極性(Al,In,Ga、B)NまたはIII族窒化物および該結晶の成長方向に垂直な表面からなる結晶である。

【解決手段】具体的には、結晶は、(Al,In,Ga,B)NまたはIII族窒化物および該結晶の成長方向に垂直な表面からなる結晶であって、該表面は少なくとも幅10μmであり、半極性方位を有し、 該結晶はx線回折により測定される半値全幅(FWHM)が0.55°未満であるロッキング・カーブにより特徴づけられる結晶品質を有することを特徴とする結晶を提供する。

(もっと読む)

半導体発光素子の製造方法及び半導体発光素子用ウェーハ

【課題】成長用基板の剥離の際の半導体層の損傷を抑制した半導体発光素子の製造方法及び半導体発光素子用ウェーハを提供する。

【解決手段】実施形態によれば、凹凸が設けられた主面を有する第1基板の主面上に、発光層を含む窒化物半導体層を形成する工程と、窒化物半導体層と第2基板とを接合する工程と、第1基板を介して窒化物半導体層に光を照射して第1基板を窒化物半導体層から分離する工程と、を含む半導体発光素子の製造方法が提供される。窒化物半導体層を形成する工程は、凹凸の凹部の内壁面上に窒化物半導体層の少なくとも一部と同じ材料を含む薄膜を形成しつつ、凹部の内側の空間内に空洞を残すことを含む。分離する工程は、薄膜に光の少なくとも一部を吸収させて、窒化物半導体層のうちで凹部に対向する部分に照射される光の強度を、窒化物半導体層のうちで凹凸の凸部に対向する部分に照射される光の強度よりも低くすることを含む。

(もっと読む)

窒化物半導体発光素子およびその製造方法

【課題】静電耐圧が高い窒化物半導体発光素子を歩留まりが高く製造する窒化物半導体発光素子の製造方法を提供する。

【解決手段】本発明の窒化物半導体発光素子は、成長用基板と、該成長用基板上に形成されたn型窒化物半導体層と、該n型窒化物半導体層上に形成された発光層と、該発光層上に形成されたp型窒化物半導体層とを有し、n型窒化物半導体層の発光層と接する側の表面から基板に向けて略垂直に延び、直径が2nm〜200nmであるパイプ穴を5000個/cm2以下有することを特徴とする。

(もっと読む)

1 - 20 / 291

[ Back to top ]