Fターム[5F045CA00]の内容

気相成長(金属層を除く) (114,827) | 半導体素子等への用途 (4,120)

Fターム[5F045CA00]の下位に属するFターム

バイポーラトランジスタ (218)

MISトランジスタ(TFTを除く) (459)

MESトランジスタ (82)

HEMT(高移動度トランジスタ) (427)

発光素子 (1,898)

受光素子(太陽電池など) (638)

TFT(薄膜トランジスタ) (329)

感光ドラム(電子写真用感光体) (44)

ホール素子 (2)

インパットダイオード、ガンダイオード (9)

Fターム[5F045CA00]に分類される特許

1 - 14 / 14

炭化ケイ素単結晶基板

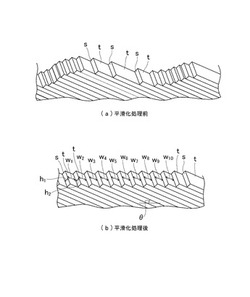

【課題】優れた特性の炭化ケイ素半導体素子を作製することが可能な、ステップテラス構造を持った炭化ケイ素単結晶基板を提供する。

【解決手段】炭化ケイ素単結晶の(0001)面に対して傾いた主面を有する炭化ケイ素単結晶基板であって、前記主面はステップsとテラスtとのステップテラス構造を有し、前記ステップテラス構造における前記ステップsの平均高さhが0.25nm以上3nm

以下であり、前記主面の(0001)面に対する傾斜角をθとするとき、前記主面内のいずれかの場所において、前記ステップsに沿う方向に対して垂直な方向に、前記ステップsと前記テラスtとが連続する10対の前記ステップテラス構造におけるテラス幅W1〜W10のうち90%以上が、W0=h/tanθで求まる平均テラス幅W0との相対誤差が10%以内にある。

(もっと読む)

光導波路素子の製造方法

【課題】選択成長において、露出しているコア層の端面の酸化を抑制し、選択成長前にハリゲン系ガスを用いる必要をなくし、端面の酸化に起因する異常成長を抑制する。

【解決手段】半導体基板の上に、Alを含まない化合物半導体からなる第1のコア層20を形成する。半導体基板の上に形成すべき導波路の導波方向に関する一部分である第1の領域A1に接する第2の領域A2の第1のコア層を除去し、第1の領域と第2の領域との境界に第1のコア層の端面を露出させる。第1のコア層が除去された第2の領域に、Alを含む化合物半導体からなる第2のコア層30を形成する。第1の領域を基準として第2の領域とは反対側に配置され、第1の領域に接する第3の領域A3内の第1のコア層を除去し、第1の領域と第3の領域との境界に第1のコア層の端面を露出させる。第1のコア層が除去された第3の領域に、Alを含む化合物半導体からなる第3のコア層35を形成する。

(もっと読む)

半導体装置及びその製造方法

【課題】 窒化アルミニウムあるいは窒化アルミニウムガリウムを含む窒化物半導体層を用い、緩やかに傾斜したフィールドプレートの形成が容易に形成ができ、電界集中を緩和して高耐圧化が実現できる窒化物半導体装置及びその製造方法を提供する。

【解決手段】 窒化アルミニウムあるいは窒化アルミニウムガリウムを含む窒化物半導体層に形成した側壁が斜めに傾斜した凹部内に、ゲート電極を形成する。側壁が斜めの凹部は、アルミニウムを含む窒化物半導体層の結晶性を劣化させながら成長させ、その後、結晶性の違いに応じてエッチングレートが異なるエッチング液を使用してエッチングして形成する。あるいはアルミニウムの組成比を変化させて形成することも可能である。

(もっと読む)

窒化物半導体基板

【課題】ノッチ角部への残留物を減らし、窒化物半導体基板上への結晶成長歩留を向上できる窒化物半導体基板を提供する。

【解決手段】円形の窒化物半導体基板本体2の外周に結晶方位と表裏面とを特定するノッチ3を形成する窒化物半導体基板1において、窒化物半導体基板本体2の外周に、複数の辺からなるノッチ3が形成され、そのノッチ3の結晶方位を示す方位辺4が結晶方位と±0.3°以内で一致するように形成され、かつ、表裏面を特定する表裏判別辺6と方位辺4との角度θが90°よりも大きくなるように形成され、かつ、各辺の交点の曲率半径が0.1mm以上となるように形成されているものである。

(もっと読む)

III族窒化物半導体基板の製造方法

【課題】精度のよいオリフラおよびインフラを有するIII族窒化物半導体基板を簡単に、かつ短時間で製造できるIII族窒化物半導体基板の製造方法を提供する。

【解決手段】サファイア基板2上に第一の層3、金属膜4を順次形成した後、第一の層3中に空隙6を発生させて下地基板7とし、その下地基板7上に第二の層8を形成し、第二の層8を、III族窒化物半導体基板11とすべく下地基板7から剥離して形成するIII族窒化物半導体基板11の製造方法において、第一の層3中に空隙6を発生させる際に、空隙割合が過多となる部分Cを形成し、その後、第二の層8を形成して、その第二の層8に空隙割合が過多となる部分と対応する部分にピット列12を形成し、その剥離後のIII族窒化物半導体基板11にピット列12を境界にしてオリフラ9およびインフラ10を形成するものである。

(もっと読む)

III−V族化合物半導体の結晶成長方法と結晶成長装置

【課題】 III-V族化合物半導体の結晶成長方法において、半導体下地層と半導体層の界面に高濃度なn型領域が形成されることを抑制する技術を提供すること。

【解決手段】 シリコンをエッチング可能なエッチング材を利用して半導体下地層の表面を洗浄する工程と、洗浄後の半導体下地層をアルコールに浸漬する工程と、浸漬された状態で半導体下地層をガス置換室に搬入する工程と、ガス置換室内を大気から置換ガスに置換する工程と、ガス置換室に連結する反応室に液体から取り出した半導体下地層を搬入する工程と、反応室内で半導体下地層の表面に前記半導体層を結晶成長させる工程を備えている。置換ガスは、シリコン濃度が0.2ppm以下である。

(もっと読む)

窒化物半導体装置の製造方法

【課題】 電流コラプスの抑制と高耐圧化が実現できると共に、微結晶構造の窒化物半導体層を緩やかに傾斜した形状に形成し、電界集中を緩和することができる窒化物半導体装置の製造方法を提供する。

【解決手段】 アルミニウムを含まない高絶縁性の第2の窒化物半導体層に形成した側壁が斜めに傾斜した凹部内に、ゲート電極を形成する。側壁が斜めの凹部は、第2の窒化物半導体装置の成長温度を徐々に低くしながら成長させ、その後、成長温度に応じてエッチングレートが異なるエッチング液を使用してエッチングして形成する。

(もっと読む)

成膜装置及び成膜方法

【課題】面内の良好な電気的特性を備える膜を形成することが可能な成膜装置及び成膜方法を提供する。

【解決手段】成膜装置100は基板11が載置される陽極102と、陽極102との間でプラズマを発生させる陰極103と、ステージ104と、ステージ104内に設置された冷却部201と、を備える。冷却部201の冷却ヘッド部201aのステージ104と対向する面に、凹部201cが形成されることにより、冷却ヘッド部201aの周縁部のみがステージ104に当接する。これにより基板11は周辺領域から冷却され、基板の中心領域から周辺領域へと熱流を生じさせることができ、基板11内に温度勾配を生じさせることができる。

(もっと読む)

化学蒸着装置及び半導体デバイスの製造方法

【課題】発熱体4と基板ホルダー5間を遮蔽及び開口するためのシャッター7を備えた化学蒸着装置において、シャッター7の開閉制御を最適化して成膜開始初期の膜質の劣悪性を解消する。

【解決手段】前記シャッター7が遮蔽位置にある状態で前記発熱体4への通電を開始し、前記発熱体4を所定温度まで発熱させた後、原料ガスの供給を開始すると共に、排気速度を制御して、処理容器1内を所定の圧力とし、その後前記シャッター7を開口位置へ移動させる制御部8を設ける。

(もっと読む)

クラックおよび/または表面欠陥密度が減少したエピタキシャル熱電膜を堆積させる方法および関連する装置

基板の結晶方位によって画定された面に対して約5°から約45°のオフカット角でオフカットされた成長表面を備える基板が設けられる。この成長表面上に、熱電膜がエピタキシャル成長される。熱電膜の結晶方位は、成長表面に対して約5°から約30°の角度で傾斜しているとよい。熱電膜のエピタキシャル成長の前に、基板の成長表面は、基板から突出する複数のメサを画定するように、パターン化されてもよい。関連する方法および熱電素子も検討されている。  (もっと読む)

(もっと読む)

炭化珪素半導体エピタキシャル基板の製造方法。

【課題】基底面転位欠陥の少ない炭化珪素半導体エピタキシャル基板を製造する方法を提供する。

【解決手段】本発明の、炭化珪素半導体エピタキシャル基板の製造方法は、オフセット角が2°以上10°以下であり、二乗平均粗さが0.1nm以下である表面10aを有する炭化珪素単結晶基板10を用意する工程と、化学気相堆積法により、炭化珪素からなるエピタキシャル層11を前記炭化珪素単結晶基板上に成長させる工程とを包含し、前記成長したエピタキシャル層の表面の二乗平均粗さRq(nm)がエピタキシャル層11の成長速度をV(μm/h)として、Rq(nm)<0.007×V(μm/h)+0.074の関係を満足するように、前記エピタキシャル層の成長条件を設定する。

(もっと読む)

有機金属化学気相成長法によるPrMnO3/CaMnO3超格子構造を有するPrxCa1−xMnO3薄膜の形成方法

【課題】 MOCVD法によるPMO/CMO超格子構造を有するPrxCa1−xMnO3薄膜の形成方法を提供する。

【解決手段】 MOCVD法によるPMO/CMO超格子構造を有するPrxCa1−xMnO3薄膜の形成方法は、有機金属化合物と溶媒を準備する工程と、有機金属化合物と溶媒を混合してPMO前駆体及びCMO前駆体を形成する工程を備え、PMO前駆体及びCMO前駆体は、MOCVD反応室の気化器に注入される。PMO前駆体とCMO前駆体を交互にMOCVD反応室の気化器に注入することによりナノサイズのPCMO薄膜または結晶質のPCMO薄膜を形成するために堆積パラメータが選択される。選択された堆積パラメータは、PCMO薄膜の特定部分において所望のPr:Ca濃度比を有するPCMO薄膜種を堆積するために維持される。得られたPCMO薄膜は選択された温度で選択された時間アニーリングされる。

(もっと読む)

炭化珪素薄膜の成膜方法

【課題】 モノシラン(SiH4)、ジシラン(Si2H6)等の特殊高圧ガスに比べて安全性に優れたモノメチルシラン(SiH3CH3)等の有機シランを用いて、高品質の炭化珪素薄膜を得ることができる炭化珪素薄膜の成膜方法を提供する。

【解決手段】 シリコン基板の表面にCVD法によりSiC薄膜を成膜する方法であり、シリコン基板が載置された反応装置内にプロパン(C3H8)ガスを導入する第1工程(I)と、反応装置内にプロパン(C3H8)ガスとヘキサメチルジシラン(HMDS)とを導入する第2工程(II)と、反応装置内にヘキサメチルジシラン(HMDS)を導入する第3工程(III)とを有することを特徴とする。

(もっと読む)

PrxCa1−xMnO3薄膜製造のための低温MOCVD処理

【課題】 PCMOスイッチング薄膜を有する抵抗性ランダムアクセスメモリ装置の製造方法を提供する。

【解決手段】 PCMO前駆体を準備する工程(#12)と、基板を準備する工程(#14)と、前記基板をMOCVD反応室内に戴置する工程(#16)と、前記PCMO前駆体を前記MOCVD反応室内に導入してPCMO薄膜を前記基板上に堆積させる工程(#18)と、MOCVD気化器を240〜280℃の温度範囲に維持し、且つ、前記MOCVD反応室を300〜400℃の温度範囲に維持する工程(#20)と、前記PCMO薄膜を担持した基板を前記MOCVD反応室から取り出す工程(#24)と、前記抵抗性ランダムアクセスメモリ装置を完成させる工程(#26)を有する。

(もっと読む)

1 - 14 / 14

[ Back to top ]