Fターム[5F045DA00]の内容

気相成長(金属層を除く) (114,827) | 半導体成長層の構造 (3,415)

Fターム[5F045DA00]の下位に属するFターム

ヘテロ構造A/B

半導体成長層の形状、構造 (2,125)

半導体成長層の組成 (445)

結晶構造(微結晶・柱状晶・粒径等) (195)

半導体成長層の物性 (649)

Fターム[5F045DA00]に分類される特許

1 - 1 / 1

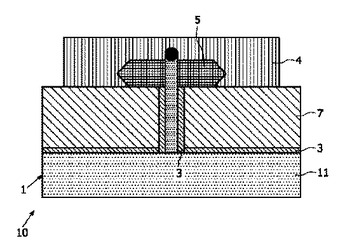

半導体デバイスを製造する方法及びそのような方法で得られる半導体デバイス

本発明は、少なくとも1つの半導体素子を備える半導体本体(1)を備える半導体デバイス(10)を製造する方法に関し、半導体本体(1)の上には、メサ形状半導体領域(2)が形成され、マスキング層(3)が、メサ形状半導体領域(2)の上に蒸着され、その頂部でメサ形状半導体領域(2)の側面と境界を接するマスキング層(3)の一部(3A)が取り除かれ、導電性接続領域(4)が、結果として得られる構造の上に形成され、メサ形状半導体領域(2)のための接点を形成する。本発明によれば、マスキング層(3)の部分(3A)の除去後、導電性接続領域(4)の形成前に、メサ形状半導体領域(2)が、マスキング層(3)の部分(3A)の除去によって自由にされるメサ形状半導体領域(2)の側面で追加的半導体領域(5)によって広げられる。このようにして、極めて低い接触抵抗を有するデバイス(10)が簡単な方法で得られる。好ましくは、メサ形状半導体領域(2)は、VLSのようなさらなるエピタキシアル成長プロセスによってナノワイヤによって形成される。追加的領域(5)は、例えば、MOVPEによって得られ得る。

(もっと読む)

(もっと読む)

1 - 1 / 1

[ Back to top ]