Fターム[5F045DA52]の内容

気相成長(金属層を除く) (114,827) | 半導体成長層の構造 (3,415) | 半導体成長層の形状、構造 (2,125) | 多層成長層 (2,091)

Fターム[5F045DA52]の下位に属するFターム

バッファ層・中間層・遷移層を有するもの (1,084)

超格子(歪超格子、変調ドープ超格子を含む) (99)

量子井戸 (345)

量子細線・量子箱 (31)

Fターム[5F045DA52]に分類される特許

1 - 20 / 532

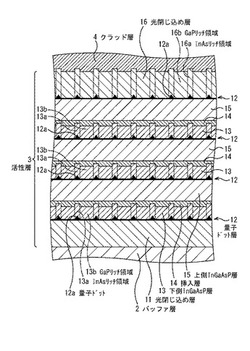

光半導体素子及びその製造方法

【課題】高い光利得を得ながら閾値電流値を低減することができる光半導体素子及びその製造方法を提供する。

【解決手段】基板の上方に形成された複数の量子ドット層12と、複数の量子ドット層12間に位置する中間層と、が設けられている。量子ドット層12に含まれる量子ドット12aの組成が、InxGa1-xAsySb1-y(0<x≦1、0<y≦1)で表わされる。中間層には、組成がInaGa1-aAsbP1-b(0<a<1、0<b<1)で表わされ、厚さが10nm以上40nm以下のInGaAsP層13、15と、InGaAsP層13、15の底面から10nm以上40nm未満の高さに位置し、厚さが0.3nm以上2nm以下のInP層14と、が含まれている。

(もっと読む)

半導体装置とその製造方法

【課題】 寄生ダイオードを介したリーク電流を抑えること。

【解決手段】 半導体装置1は、c面を表面とする窒化物半導体の半導体層13と、厚みが減少する厚み減少部14aを有する窒化物半導体のp型の埋込み層14と、を備える。埋込み層14では、厚み減少部14aの内部に酸素濃度がピークとなる部分が存在しており、そのピーク部分と厚み減少部14aの傾斜面の間のp型不純物の濃度が酸素濃度よりも高い部分が存在する。

(もっと読む)

シリコン膜の形成方法及び半導体装置の製造方法

【課題】狭スペースへのシリコン膜の埋め込み性の向上を図る。

【解決手段】実施形態によれば、シリコン膜の形成方法は、凹部20の開口側からボトム側に向けてくぼんだくぼみ40を有するアンドープの第1のシリコン膜32を凹部20に形成する工程を含む。また、前記シリコン膜の形成方法は、凹部20内の第1のシリコン膜32の一部を塩素を含むガスを用いてエッチングし、第1のシリコン膜32に凹部20のボトム側よりも開口側で幅が広い隙間41を形成する工程を含む。また、前記シリコン膜の形成方法は、隙間41に面する第1のシリコン膜32の内壁に不純物を添加する工程を含む。また、前記シリコン膜の形成方法は、不純物の添加後、隙間41を埋める第2のシリコン膜33を形成する工程を含む。

(もっと読む)

窒化物半導体素子、窒化物半導体装置、窒化物半導体ウェハおよび窒化物半導体素子の製造方法

【課題】窒化物半導体層に加わるダメージを抑制しながら、窒化物半導体層と電極との間でオーミック接触を得ることが可能な窒化物半導体素子を提供する。

【解決手段】この発光素子(窒化物半導体素子)1は、主面10aを有する基板10と、n型層20a、n型コンタクト層20bおよびp型層20dを含む半導体層20と、を備える。主面10aはm面に対してa軸方向に所定のオフ角度を有する。半導体層20は、傾斜領域21と非傾斜領域22とを含む。傾斜領域21において、n型層20aおよびn型コンタクト層20bの所定領域上にn電極40が形成されている。

(もっと読む)

化合物半導体装置及びその製造方法

【課題】比較的簡素な構成で電流コラプスの発生を抑制し、デバイス特性の劣化を抑えた信頼性の高い高耐圧のAlGaN/GaN・HEMTを実現する。

【解決手段】SiC基板1上に化合物半導体積層構造2を備えたAlGaN/GaN・HEMTにおいて、3層のキャップ層2eを用いることに加え、キャップ層2eのドレイン電極5の近傍(ゲート電極6とドレイン電極5との間で、ドレイン電極5の隣接箇所)に高濃度n型部位2eAを形成し、高濃度n型部位2eAでは、そのキャリア濃度が電子供給層2dのキャリア濃度よりも高く、そのエネルギー準位がフェルミエネルギーよりも低い。

(もっと読む)

気相成長装置の清浄度評価方法

【課題】 本発明は、気相成長装置内の汚染不純物の種類によってモニタウエーハの導電型を使い分ける必要なく、高感度で正確に清浄度を評価することのできる気相成長装置の清浄度評価方法を提供することを目的とする。

【解決手段】 気相成長装置の清浄度を評価する方法であって、

前記気相成長装置を用いて、シリコンウエーハ上に導電型がP型のエピタキシャル層とN型のエピタキシャル層を順不同で連続して成長させたモニタウエーハを製造して、該モニタウエーハのライフタイム値を測定し、

前記モニタウエーハのライフタイム値から前記気相成長装置の清浄度を評価することを特徴とする気相成長装置の清浄度評価方法。

(もっと読む)

有機金属化学気相成長法および装置

【課題】基板のゆがみや破損を防止する有機金属化学気相成長(MOCVD)法および装置を提供する。

【解決手段】有機金属化学気相成長(MOCVD)法は、第1表面に金属系材料層が配置された基板を提供することと、金属系材料層が基板とベースの間に介するように基板をチャンバー内のベースの上に配置することと、第1表面の反対側にある基板の第2表面にMOCVDプロセスを行うこととを含む。金属系材料層と基板の間の熱伝導率の差は、1W/m℃〜20W/m℃の範囲内であり、金属系材料層と基板の熱膨張係数は、同一等級である。

(もっと読む)

半導体装置の製造方法

【課題】結晶性の優れた炭化シリコン膜を形成することができる炭化シリコンからなる半導体装置の製造方法を提供する。

【解決手段】基板1上に、絶縁膜2を介してシリコン膜3が形成された半導体基板を用意し、炭化シリコン膜6形成予定領域を選択的に被覆するマスク膜5を形成する。このマスク膜5で被覆されない領域のシリコン膜3を酸化し、酸化シリコン膜4を形成する。マスク膜5を除去し、シリコン膜3を露出させ、露出したシリコン膜3を炭化し、炭化シリコン膜6を形成する。その後、炭化シリコン膜6上に炭化シリコンのエピタキシャル成長膜8を形成する。

(もっと読む)

窒化物半導体構造の製造方法

【課題】平坦な表面を有し、結晶性の高い窒化物半導体下地層を、反りを抑えて、大きな成長速度で成長させることができる窒化物半導体構造の製造方法を提供する。

【解決手段】第3の窒化物半導体下地層を形成する工程において、第3の窒化物半導体下地層の成長時に単位時間当たりに供給されるV族原料ガスのモル量と単位時間当たりに供給されるIII族原料ガスのモル量との比であるV/III比を700以下とし、第3の窒化物半導体下地層の成長時の圧力を26.6kPa以上とし、第3の窒化物半導体下地層の成長速度を2.5μm/時以上とする、窒化物半導体構造の製造方法である。

(もっと読む)

窒化物半導体装置およびその製造方法

【課題】GaNを用いた窒化物半導体装置において、電流が流れる経路に、再結晶成長などによる界面が存在することがない状態で、十分な耐圧が得られるようにする。

【解決手段】GaNからなるチャネル層(第2半導体層)101と、チャネル層101の一方の面であるN極性面に形成された第1障壁層(第1半導体層)102と、チャネル層101の他方の面であるIII族極性面に形成された第2障壁層(第3半導体層)103とを備える。第1障壁層102および第2障壁層103は、例えば、AlGaNから構成されている。また、ドレイン電極(第1電極)104が、第1障壁層102の上に形成され、ゲート電極105が、ドレイン電極104に対向して第2障壁層103の上に形成されている。ソース電極(第2電極)106は、ゲート電極105と離間して第2障壁層103の上に形成されている。

(もっと読む)

電界効果トランジスタおよびその製造方法

【課題】GaNを用いた縦型の電界効果トランジスタにおいて、素子の作製にコストの上昇を招くことなく、ドレイン電流密度を大きくできるようにする。

【解決手段】GaNからなるチャネル層101と、GaNより大きなバンドギャップエネルギーを有してアルミニウムを含む窒化物半導体から構成されてチャネル層101の一方の面に形成された障壁層102を備える。ここで、チャネル層101の一方の面は、N極性面とされ、他方の面はIII族極性面とされていればよい。また、チャネル層101の他方の面に形成されたドレイン電極103と、ドレイン電極103に対向して障壁層102の上に形成されたゲート電極104と、ゲート電極104と離間して障壁層102の上に形成されたソース電極105とを備える。

(もっと読む)

炭化珪素半導体装置およびその製造方法

【課題】閾値電圧のばらつきを低減できる炭化珪素半導体装置を提供する。

【解決手段】炭化珪素半導体装置10は、基板11と、基板11上に設けられ、主表面13Aと、主表面13Aと交差する厚さ方向とを有する炭化珪素層4とを含む。炭化珪素層4は、チャネル層7と、ソース領域15と、ドレイン領域17と、ソース領域15とドレイン領域17との間において、ゲート領域16Rとを含む。ゲート領域16Rはチャネル層7に対して、第1の導電型と異なる第2の導電型を有するようにエピタキシャル成長されている。

(もっと読む)

半導体装置

【課題】電子走行層にFeが入り込むことを抑制し、半導体層等にクラックの発生が抑制される電界効果型トランジスタを提供する。

【解決手段】基板11の上に形成された半導体材料に高抵抗となる不純物元素がドープされた高抵抗層14と、高抵抗層14の上に形成された多層中間層15と、多層中間層15の上に半導体材料により形成された電子走行層16と、電子走行層の上に半導体材料により形成された電子供給層17と、を有し、多層中間層15は、GaN層とAlN層とが交互に積層された多層膜により形成されていることを特徴とする半導体装置。

(もっと読む)

トランジスタ用エピタキシャルウェハの製造方法

【課題】成長時間を短縮してスループットを向上することが可能なトランジスタ用エピタキシャルウェハの製造方法を提供する。

【解決手段】基板2上に、電子供給層6,10及びチャネル層8を有する高電子移動度トランジスタ構造層3を形成する工程と、高電子移動度トランジスタ構造層3上に、コレクタ層14、ベース層15、エミッタ層16及びノンアロイ層18を有するヘテロバイポーラトランジスタ構造層4を形成する工程と、を有するトランジスタ用エピタキシャルウェハの製造方法において、ヘテロバイポーラトランジスタ構造層4を、気相成長法により成長温度400℃以上600℃以下で、かつ、一定の成長温度で成長するようにした。

(もっと読む)

成膜装置

【課題】基板の一面と他面にそれぞれ機能膜を効率よく成膜することが可能な成膜装置を提供する。

【解決手段】キャリア35はフレーム41を備えている。フレーム41は、支持した基板Wの一面Wa側、および他面Wb側をそれぞれ露出させる開口(開口部)41a,41bがそれぞれ形成されている。フレーム41の一端には、キャリア35をアノードとして機能させるためのアノード接点43が設けられている。キャリア35は、第一成膜室(プロセス室)や第二成膜室(プロセス室)において、アノード接点43を介して接地側に電気的に接続され、アノードして機能する。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】ドレイン−ソース間のリーク電流が少なく、かつ、ノーマリーオフの半導体装置を提供する。

【解決手段】基板11の上に形成された不純物元素を含む第1の半導体層13と、第1の半導体層13の上に形成された第2の半導体層16と、第2の半導体層16の上に形成された第3の半導体層17と、第3の半導体層17の上に形成されたゲート電極21、ソース電極22及びドレイン電極23と、を有し、第2の半導体層16において、ゲート電極21の直下には、第1の半導体層13と接し、第1の半導体層13に含まれる不純物元素が拡散している不純物拡散領域15が形成されており、不純物元素は、不純物拡散領域がp型となる元素であることを特徴とする半導体装置。

(もっと読む)

窒化物電子デバイス、窒化物電子デバイスを作製する方法

【課題】リーク特性のばらつき幅を低減可能な、窒化物電子デバイスを作製する方法を提供する。

【解決手段】テトラメチルアンモニウムヒドロキシドを含む第1溶液を用いた処理を行って半導体積層53bに第1処理面65fを処理装置10dで形成する。第1溶液による処理温度は、摂氏50度以上摂氏100度以下である。第1溶液の濃度は5パーセント以上であり、50パーセント以下である。第1処理工程に引き続き第2処理工程を行う。第2処理工程では、テトラメチルアンモニウムヒドロキシド処理の後に、フッ化水素酸及び過酸化水素を含む第2溶液を用いた処理を半導体積層53bに行って半導体積層53bに第2処理面65gを処理装置10eで形成する。第2処理工程の後において、半導体積層53bの処理面65gのドナー性不純物の濃度は5×1017cm−3以下である。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】不純物濃度の均一性および結晶性に優れたn型ダイヤモンド半導体層を有する半導体装置およびその製造方法を提供する。

【解決手段】実施の形態の半導体装置は、(100)面から<011>±10度方向に10度以上40度以下の範囲で傾斜する面を備えるダイヤモンド基板と、上記面上に形成され、リン(P)を含有するn型ダイヤモンド半導体層と、を備える。実施の形態の半導体装置の製造方法は、(100)面から<011>±10度方向に10度以上40度以下の範囲で傾斜する面を備えるダイヤモンド基板を準備し、上記面上に、エピタキシャル成長により、リン(P)を含有するn型ダイヤモンド半導体層を形成する。

(もっと読む)

半導体結晶基板、半導体結晶基板の製造方法、半導体装置の製造方法、電源装置及び増幅器

【課題】基板の外周部においてクラックの発生が抑制される半導体結晶基板を提供する。

【解決手段】半導体結晶基板110と、基板110の表面に窒化物により形成された保護層120と、を有し、保護層120は、基板110の外周部となる周辺領域120aはアモルファス状態であり、基板110の周辺領域よりも内側の内部領域120bは結晶化している。

(もっと読む)

堆積膜形成方法

【課題】膜厚や膜特性の均一性に優れた堆積膜を歩留まり良く形成する方法。

【解決手段】底部材および蓋部材ならびに底部材および蓋部材から絶縁されている壁部材からなる反応容器の中に基体および基体を保持している基体ホルダを入れ、基体ホルダの一端と底部材とを電気的に接続し、基体ホルダの他端と蓋部材とを電気的に接続する工程(i)と、蓋部材、基体ホルダおよび底部材からなる電気が伝わる経路の電気抵抗値を測定する工程(ii)とをこの順に有し、電気抵抗値が所定値以下である場合、底部材および蓋部材を反応容器の外部で電気的に接続し、反応容器に堆積膜形成用原料ガスを導入し、反応容器に導入された堆積膜形成用原料ガスを励起させて励起種を生成して基体上に堆積膜を形成する工程(iii)に進み、電気抵抗値が所定値を超える場合、工程(iii)に進まない。

(もっと読む)

1 - 20 / 532

[ Back to top ]