Fターム[5F045DA57]の内容

気相成長(金属層を除く) (114,827) | 半導体成長層の構造 (3,415) | 半導体成長層の組成 (445)

Fターム[5F045DA57]の下位に属するFターム

組成が傾斜(勾配)を有するもの (84)

不純物濃度 (218)

Fターム[5F045DA57]に分類される特許

1 - 20 / 143

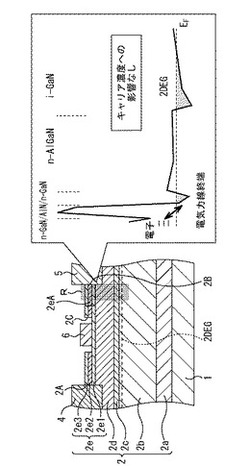

化合物半導体装置及びその製造方法

【課題】比較的簡素な構成で電流コラプスの発生を抑制し、デバイス特性の劣化を抑えた信頼性の高い高耐圧のAlGaN/GaN・HEMTを実現する。

【解決手段】SiC基板1上に化合物半導体積層構造2を備えたAlGaN/GaN・HEMTにおいて、3層のキャップ層2eを用いることに加え、キャップ層2eのドレイン電極5の近傍(ゲート電極6とドレイン電極5との間で、ドレイン電極5の隣接箇所)に高濃度n型部位2eAを形成し、高濃度n型部位2eAでは、そのキャリア濃度が電子供給層2dのキャリア濃度よりも高く、そのエネルギー準位がフェルミエネルギーよりも低い。

(もっと読む)

半導体発光素子及びその製造方法

【課題】電気的特性がより向上した酸化亜鉛系透明導電性薄膜を有する半導体発光素子及びその製造方法を提供する。

【解決手段】本発明の半導体発光素子は、3族元素がドープされた酸化亜鉛系透明導電性薄膜を有し、前記3族元素の濃度は、前記酸化亜鉛系透明導電性薄膜の厚さ方向に複数の周期を有する波形ように濃度の濃淡が変化することを特徴とする。

(もっと読む)

炭化珪素半導体装置およびその製造方法

【課題】閾値電圧のばらつきを低減できる炭化珪素半導体装置を提供する。

【解決手段】炭化珪素半導体装置10は、基板11と、基板11上に設けられ、主表面13Aと、主表面13Aと交差する厚さ方向とを有する炭化珪素層4とを含む。炭化珪素層4は、チャネル層7と、ソース領域15と、ドレイン領域17と、ソース領域15とドレイン領域17との間において、ゲート領域16Rとを含む。ゲート領域16Rはチャネル層7に対して、第1の導電型と異なる第2の導電型を有するようにエピタキシャル成長されている。

(もっと読む)

半導体装置

【課題】格子整合したバッファ層、及び高い平坦性を有する接合界面を得ることが可能な半導体装置を提供すること。

【解決手段】本発明は、n−GaNからなる基板10と、基板10上に設けられ、InxAl1−xN(0.15≦x≦0.2)からなる第1バッファ層12と、第1バッファ層12上に設けられ、厚さ1nm以上10nm以下のAlNからなるスペーサ層14と、スペーサ層14上に設けられ、GaNからなるチャネル層16と、チャネル層16上に設けられ、窒化物半導体からなる電子供給層18と、を具備する半導体装置である。

(もっと読む)

窒化物半導体層を成長させるためのバッファ層構造を有する基板

【課題】窒化物半導体デバイス用の半導体積層構造を成長させるために改善されたバッファ層構造を有する基板を提供する。

【解決手段】窒化物半導体層を成長させるためのバッファ層構造を有する基板であって、Si単結晶基板の(111)主面に形成された窒化ケイ素層を有し、この窒化ケイ素層上に順次積層されたAl層とAlN結晶層またはAlGaN結晶層とを有し、AlN結晶層またはAlGaN結晶層の表面は(0001)の面方位とIII族元素極性の表面を有している。

(もっと読む)

窒化物半導体素子および窒化物半導体素子の製造方法

【課題】シリコン基板上に形成したクラックおよび転位が少ない高品位の窒化物半導体素子の製造方法を提供する。

【解決手段】実施態様によれば、シリコン基板上に下地層と積層中間層と機能層とが形成された後に、前記シリコン基板が除去された窒化物半導体素子が提供される。前記窒化物半導体素子は、前記下地層と、前記積層中間層と、前記積層中間層と、を備える。前記下地層は、AlNバッファ層とGaN下地層とを含む。前記積層中間層は、前記下地層と前記機能層との間に設けられる。前記積層中間層は、AlN中間層と、AlGaN中間層と、GaN中間層と、を含む。前記AlGaN中間層は、前記AlN中間層に接する第1ステップ層を含む。前記第1ステップ層におけるAl組成比は、前記AlN中間層から前記第1ステップ層に向かう方向において、ステップ状に減少している。

(もっと読む)

半導体装置の製造方法

【課題】ヒ素(As)を高濃度にドーピングした状態でエクステンション領域のエピタキシャル成長膜表面に凹凸を発生させることなく、平滑な面に形成することを可能とする。

【解決手段】半導体基板11上にゲート絶縁膜12を介してゲート電極13を備え、前記ゲート電極13の両側の前記半導体基板11上に形成された不純物を含有してなるエクステンション領域17、18を備えた半導体装置1であって、前記エクステンション領域17、18は、シリコンゲルマニウムにヒ素を含む状態でエピタキシャル成長されたエピタキシャル成長膜からなり、このエピタキシャル成長膜は、ヒ素をドーピングしながらシリコンとゲルマニウムとを前記半導体基板11上に選択的にエピタキシャル成長させて形成される。

(もっと読む)

半導体基板および電子デバイス

【課題】窒化物半導体からなる活性層にn型不純物原子をドーピングした場合であっても、活性層に発生する転位を減少することができる技術、あるいは、活性層の結晶破壊を抑制することができる技術を提供する。

【解決手段】ベース基板と、第1結晶層と第2結晶層とが交互に複数積層された積層構造体と、第3結晶層とを有し、前記ベース基板、前記積層構造体および前記第3結晶層が、前記ベース基板、前記積層構造体、前記第3結晶層の順に位置し、前記第1結晶層が、AlxGa1−xN、(但し0≦x≦1)からなり、前記第2結晶層が、AlyGa1−yN、(但し0≦y≦1、x≠y)からなり、前記第3結晶層が、AlzGa1−zN、(但し0≦z≦1)からなり、前記第1結晶層、前記第2結晶層および前記第3結晶層にシリコン原子を含む半導体基板を提供する。

(もっと読む)

p型化合物半導体層の形成方法

【課題】p型化合物半導体層の形成の際に、p型不純物と水素の結合を遮断するp型化合物半導体層の形成方法を、提供する。

【解決手段】

p型化合物半導体層の形成方法が開示される。この方法では、反応チェンバ内に、III族元素のソースガス、p型不純物のソースガス、及び水素を含有する窒素のソースガスを供給し、p型化合物半導体層を成長させる。また、p型化合物半導体層の成長が完了した後、III族元素のソースガス及びp型不純物のソースガスの供給を中断し、基板の温度が400〜900℃である間に、水素を含有する窒素のソースガスの供給を中断及び排出し、冷却ガスで常温まで冷却させる。これにより、基板の温度を冷却させる過程で、p型化合物半導体層に含まれたp型不純物に水素が結合することを防ぐことができる。

(もっと読む)

窒化物半導体基板及びその製造方法

【課題】より高いしきい値電圧と電流コラプス改善を両立できる、ノーマリーオフ型の高耐圧デバイスに好適な窒化物半導体基板及びその製造方法を提供する。

【解決手段】基板1と、前記基板1の一主面上に形成されるバッファー層2と、前記バッファー層2上に形成される中間層3と、前記中間層3上に形成される電子走行層4と、前記電子走行層4上に形成される電子供給層5とを含む窒化物半導体基板10において、前記中間層3を厚さ200nm以上1500nm以下、炭素濃度5×1016atoms/cm3以上1×1018atoms/cm3以下のAlxGa1-xN(0.05≦x≦0.24)とし、前記電子走行層4が厚さ5nm以上200nm以下のAlyGa1-yN(0≦y≦0.04)とする。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】窒化物半導体装置の、ソース・ドレイン間のオン抵抗を低減する。

【解決手段】ソース・ドレイン間を走行する窒化物半導体層と下地となる窒化物半導体層の間に、両窒化物半導体層より電子親和力が大きく、下地となる窒化物半導体よりも格子定数の大きい材料を形成する。その結果、ゲート電圧の印加によりゲート絶縁膜の下方に形成されるチャネルと、ゲート部以外で形成される二次元電子ガスを、深さ方向において近づけることができ、オン抵抗の低減が可能となる。

(もっと読む)

化合物半導体装置及びその製造方法

【課題】絶縁破壊耐性に優れた化合物半導体積層構造を備えて基板の絶縁破壊の十分な抑止を実現し、ピンチオフ状態とする際にもリーク電流が極めて少ない信頼性の高い化合物半導体装置を実現する。

【解決手段】Si基板1上に形成された化合物半導体積層構造2は、その厚みが10μm以下であって、AlNからなる厚い第1のバッファ層を有しており、III族元素(Ga,Al)の総原子数のうち、Al原子の比率が50%以上とされ、換言すれば、V族元素のNとの化学結合(Ga−N,Al−N)の総数のうち、Al−Nが50%以上とされる。

(もっと読む)

窒化物半導体素子、窒化物半導体ウェーハ及び窒化物半導体層の製造方法

【課題】シリコン基板上に形成される、低転位密度で結晶品質が優れた窒化物半導体素子、窒化物半導体ウェーハ及び窒化物半導体層の製造方法を提供する。

【解決手段】実施形態によれば、下地層と、機能層と、を備えた窒化物半導体層が提供される。下地層は、シリコン基板の上に形成されたAl含有窒化物半導体層の上に形成され、不純物濃度が低く、GaNを含む。機能層は、下地層の上に設けられる。機能層は、下地層の不純物濃度よりも高い不純物濃度を有し第1導電形のGaNを含む第1半導体層を含む。Al含有窒化物半導体層は、多層構造体を含む。多層構造体は、Alを含む窒化物半導体を含む複数の第2層と、複数の第2層の間に設けられ第2層におけるAl組成比よりも低いAl組成比を有する窒化物半導体を含む第1層と、を含む。下地層の厚さは、第1層の厚さよりも厚く、第1半導体層の厚さよりも薄い。

(もっと読む)

半導体装置

【課題】高周波数動作が可能な半導体装置を提供すること。

【解決手段】本発明は、基板10上に設けられたGaN電子走行層14と、GaN電子走行層14上に設けられたAlNスペーサ層16と、AlNスペーサ層16上に設けられたInAlN電子供給層18と、InAlN電子供給層18上に設けられたゲート電極24とゲート電極24を挟むソース電極26およびドレイン電極28と、を備え、AlNスペーサ層16の膜厚が、0.5nm以上1.25nm以下の半導体装置である。

(もっと読む)

半導体素子及びその製造方法

【課題】転位密度を低減させるバッファ層を有する半導体素子を提供する。

【解決手段】基板と、基板の上方に形成されたバッファ領域と、バッファ領域上に形成された活性層と、活性層上に形成された少なくとも2つの電極とを備え、バッファ領域は、第1の格子定数を有する第1半導体層と、第1の格子定数と異なる第2の格子定数を有する第2半導体層と、第1の格子定数と第2の格子定数との間の第3の格子定数を有する第3半導体層とが順に積層した複合層を少なくとも一層有する半導体素子。

(もっと読む)

半導体素子及びその製造方法

【課題】厚膜化が可能で、反りが小さく、かつリーク電流が小さい半導体素子を提供する。

【解決手段】基板と、基板の上方に形成された第1のバッファ領域と、第1のバッファ領域上に形成された第2のバッファ領域と、第2のバッファ領域上に形成された活性層と、活性層上に形成された少なくとも2つの電極とを備え、第1のバッファ領域は、第1半導体層と、第2半導体層とが順に積層した複合層を少なくとも一層有し、第2のバッファ領域は、第3半導体層と、第4半導体層と、第5半導体層とが順に積層した複合層を少なくとも一層有し、第4半導体層の格子定数は、第3半導体層と第5半導体層の間の格子定数を有する半導体素子。

(もっと読む)

半導体装置およびその製造方法

【課題】電子移動度の低下が抑制され、かつ二次元電子ガスの閉じ込めが高められた半導体装置およびその製造方法を提供する。

【解決手段】AlaInbGa1-(a+b)N(0≦a,b≦1、0≦a+b≦1)から成り、第2の窒化物半導体層3よりもバンドギャップが大きい第1の窒化物半導体層2、AlcIndGa1-(c+d)N(0≦c,d≦1、0≦c+d≦1)から成る第2の窒化物半導体層3、IneGa1-eN(0<e≦1)から成り、第2の窒化物半導体層3よりもバンドギャップが小さいバックバリア層4、AlfIngGa1-(f+g)N(0≦f,g≦1、0≦f+g≦1)から成り、第2の窒化物半導体層3とバンドギャップが等しいチャネル層5、AlhIniGa1-(h+i)N(0≦h,i≦1、0≦h+i≦1)から成り、チャネル層5よりもバンドギャップが大きいバリア層6を、この順に基板1に積層する。

(もっと読む)

III−V族化合物半導体エピタキシャルウェハ

【課題】オン抵抗の低いストッパー層を有するIII−V族化合物半導体エピタキシャルウェハを提供する。

【解決手段】単結晶基板8上に、GaAs層、AlGaAs層からなるバッファ層9、n型不純物を含有するAlGaAs層又はInGaP層若しくはSiプレナードープ層からなる電子供給層10、InGaAs層からなるチャネル層12、ノンドープ又は低濃度n型不純物を含有するGaAs層又はAlGaAs層からなるショットキー層14、ノンドープ又は低濃度n型不純物を含有するInGaP層からなるストッパー層15、n型不純物を含有するGaAs層からなるキャップ層16を積層したHEMT構造18を有するIII−V族化合物半導体エピタキシャルウェハ17において、ストッパー層15におけるInGaP中のAsが占めるV族原子分率が15%以下であるものである。

(もっと読む)

III族窒化物半導体電子デバイス、エピタキシャル基板、及びIII族窒化物半導体電子デバイスを作製する方法

【課題】チャネル層及びバリア層のAl組成差を増大させてトランジスタ特性を改善可能な構造を有するIII族窒化物半導体電子デバイスを提供する。

【解決手段】第1の半導体層13は、歪みを含む。第1の半導体層13の歪んだAlYGa1−YNの格子定数d(13)は、無歪みのAlYGa1−YNに固有の格子定数d0(13)とAlXGa1−XNの格子定数d(21)との間の中間値を有する。歪んだAlYGa1−YNの格子定数d(13)と無歪みのAlZGa1−ZNに固有の格子定数d0(15)との差△1は、格子定数d0(15)と格子定数d0(13)との差△2より小さくなる。差分(△2−△1)に応じて、歪んだAlYGa1−YN上に成長可能な歪んだAlZGa1−ZNのAl組成を増加でき、AlYGa1−YNとAlZGa1−ZNのAl組成差を0.5以上にできる。

(もっと読む)

III族窒化物半導体電子デバイス、エピタキシャル基板、及びIII族窒化物半導体電子デバイスを作製する方法

【課題】半導体積層内の電流経路からゲート電極を隔てる半導体層を厚くできるIII族窒化物半導体電子デバイスを提供する。

【解決手段】第2の半導体層15は第1の半導体層13上に設けられる。ゲート電極17は第2の半導体層15の上に設けられる。第1の半導体層13は、AlXGa1−XN(0<X≦1)からなる半導体表面21aの上に設けられる。第2のIII族窒化物半導体材料のバンドギャップE15は第1のIII族窒化物半導体材料のバンドギャップE13より大きい。第1の半導体層13の第1のIII族窒化物半導体材料はAlXGa1−XNと異なり、第1の半導体層13は歪みを内包する。また、第2の半導体層15の厚さT15は、無歪みの第1のIII族窒化物半導体材料の組成と、第2のIII族窒化物半導体の組成により規定される臨界膜厚より大きい。また、第1の半導体層13は、歪みを内包すると共に、半導体表面21aのAlXGa1−XNの上において格子緩和している。

(もっと読む)

1 - 20 / 143

[ Back to top ]