Fターム[5F045HA02]の内容

気相成長(金属層を除く) (114,827) | 他プロセスとの組合せ (2,158) | 前処理(膜形成が後) (762) | エッチング (407)

Fターム[5F045HA02]の下位に属するFターム

Fターム[5F045HA02]に分類される特許

1 - 20 / 44

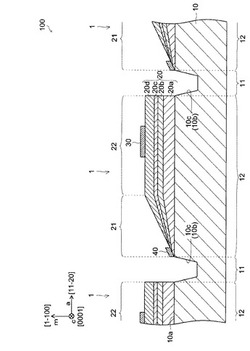

窒化物半導体素子、窒化物半導体装置、窒化物半導体ウェハおよび窒化物半導体素子の製造方法

【課題】窒化物半導体層に加わるダメージを抑制しながら、窒化物半導体層と電極との間でオーミック接触を得ることが可能な窒化物半導体素子を提供する。

【解決手段】この発光素子(窒化物半導体素子)1は、主面10aを有する基板10と、n型層20a、n型コンタクト層20bおよびp型層20dを含む半導体層20と、を備える。主面10aはm面に対してa軸方向に所定のオフ角度を有する。半導体層20は、傾斜領域21と非傾斜領域22とを含む。傾斜領域21において、n型層20aおよびn型コンタクト層20bの所定領域上にn電極40が形成されている。

(もっと読む)

結晶積層構造体及びその製造方法、並びに半導体素子

【課題】Ga2O3基板と窒化物半導体層の間の電気抵抗が低い結晶積層構造体及びその製造方法、並びにその結晶積層構造体を含む低電圧駆動の半導体素子を提供する。

【解決手段】一実施の形態においては、Ga2O3基板2と、Ga2O3基板2上のAlxGayInzN(0≦x≦1、0≦y≦1、0≦z≦1、x+y+z=1)結晶からなるバッファ層3と、バッファ層3上の、AlxGayInzN(0≦x≦1、0≦y≦1、0≦z≦1、x+y+z=1)結晶からなる窒化物半導体層4と、を含み、Ga2O3基板2の表面の窒化物半導体層4の直下の領域をバッファ層3が被覆する割合が10%以上、100%未満であり、窒化物半導体層4の一部がGa2O3基板2の表面に接触する、結晶積層構造体1を提供する。

(もっと読む)

半導体ウェーハの洗浄装置及び洗浄方法

【課題】洗浄後の半導体ウェーハ上にエピタキシャル層を形成した際の表面のエピ欠陥を低減することが可能な半導体ウェーハの洗浄装置及び洗浄方法を提供する。

【解決手段】複数の半導体ウェーハ1を所定間隔をもって起立状態でX方向に整列させて収容する反応処理槽10と、反応処理槽10の底面に設けられ、反応処理槽10にフッ化水素ガスを供給するガス供給口11とを備え、ガス供給口11は、フッ化水素ガスに含まれるミスト成分を除去するフィルタ12を有する。フィルタ12によってミスト成分が除去されたフッ化水素ガスにより半導体ウェーハ1の洗浄を行なうため、洗浄後に半導体ウェーハ1上にエピタキシャル層を形成した場合の表面のエピ欠陥を低減することができる。

(もっと読む)

エピタキシャルウェーハの製造方法

【課題】 本発明は、エピタキシャル成長工程前のエッチング工程においてエッチング量の面内均一性を改善することのできるエピタキシャルウェーハの製造方法を提供することを目的とする。

【解決手段】 シリコン単結晶基板の表面をエッチングするエッチング工程後、前記シリコン単結晶基板の表面に原料ガスを用いてエピタキシャル層を気相成長させるエピタキシャル成長工程を行うエピタキシャルウェーハの製造方法であって、前記エッチング工程において、エッチングガスとキャリアガスに前記原料ガスを含めたガスで前記シリコン単結晶基板の表面をエッチングすることを特徴とするエピタキシャルウェーハの製造方法。

(もっと読む)

半導体装置の製造方法

【課題】 半導体ウエハの表面に膜を成長させる技術であって、半導体装置を効率よく製造することが可能な技術を提供する。

【解決手段】 半導体装置の製造方法であって、チャンバ内に配置された半導体ウエハの表面に膜を成長させる動作と、チャンバ内に配置された半導体ウエハと前記膜とをエッチング可能なエッチングガスをチャンバ内に導入する動作とを実行可能な半導体製造装置のチャンバ内に半導体ウエハを搬入する搬入工程と、チャンバ内に前記エッチングガスを導入する第1エッチング工程と、チャンバ内の半導体ウエハの表面に膜を成長させる第1成膜工程と、チャンバから半導体ウエハを搬出するとともに、チャンバに別の半導体ウエハを搬入する入れ換え工程と、チャンバ内に前記エッチングガスを導入する第2エッチング工程と、チャンバ内の半導体ウエハの表面に膜を成長させる第2成膜工程を有する。

(もっと読む)

半導体基板、半導体装置及びその製造方法

【課題】異種材料の基板上に形成した平坦かつ薄い半導体基板であって、異種材料の基板からの剥離が容易な半導体基板、半導体装置及びそれらの製造方法を提供すること。

【解決手段】本発明によると、第1の面に所定の間隔で配置した複数の半球状の凸部を有する基板と、前記基板の第1の面に形成した第1の半導体層と、を有することを特徴とする半導体基板が提供される。また、前記複数の半球状の凸部の表面積の合計と前記第1の面との比は1以上である。

(もっと読む)

複数の非極性発光セルを有する発光素子

【課題】複数の非極性発光セルを有する発光素子及びその製造方法を提供すること。

【解決手段】この方法は、上部表面がr面、a面またはm面を有するサファイアまたは炭化珪素の第1の基板を用意することを含む。第1の基板は、その上部表面上にストライプ状の成長防止パターンを有し、また成長防止パターン間に側壁がc面であるリセス領域を有する。リセス領域を有する基板上に窒化物半導体層が成長され、窒化物半導体層をパターニングし、互いに分離された発光セルが形成される。これにより、優れた結晶品質の非極性発光セルを有する発光素子が提供される。

(もっと読む)

エピタキシャルウェーハの製造方法

【課題】面取り部の形状を再成形するとともに、裏面クラウンを完全に除去し、平坦性に優れた、パーティクルのほとんど無いエピタキシャルウェーハを製造することができる方法を提供することを目的とする。

【解決手段】表裏の主面と該主面の外周の面取り部とからなるシリコン単結晶基板上にエピタキシャル層を成長させることによりエピタキシャルウェーハを製造する方法において、前記シリコン単結晶基板の前記裏面側の主面全面と前記裏面側の面取り部に裏面酸化膜を形成する工程と、該裏面酸化膜を形成したシリコン単結晶基板の表面側の主面上に、40μm以上の膜厚のエピタキシャル層を成長させる工程と、該エピタキシャル層表面に保護酸化膜を形成する工程と、該保護酸化膜を形成したシリコン単結晶基板の面取り部を研削及び研磨する工程と、その後、前記保護酸化膜を除去して、仕上げの洗浄を行う工程とを含むエピタキシャルウェーハの製造方法。

(もっと読む)

化合物半導体層の形成方法

【課題】工程数の増大及び工程の長時間化が抑制された、転位の少ない化合物半導体層をエピタキシャル成長できる化合物半導体層の形成方法を提供する。

【解決手段】第1の化合物半導体層の主面を酸化して、主面、及び主面から第1の化合物半導体層内部に延伸する転位に沿った第1の化合物半導体層内部の転位領域に、酸化膜を形成するステップと、転位領域に形成された酸化膜を除去せずに、主面に形成された酸化膜を除去するステップと、転位領域に形成された酸化膜の主面に露出した部分を覆うように、主面上に第2の化合物半導体層をエピタキシャル成長させるステップとを含む。

(もっと読む)

炭化ケイ素単結晶基板

【課題】優れた特性の炭化ケイ素半導体素子を作製することが可能な、ステップテラス構造を持った炭化ケイ素単結晶基板を提供する。

【解決手段】炭化ケイ素単結晶の(0001)面に対して傾いた主面を有する炭化ケイ素単結晶基板であって、前記主面はステップsとテラスtとのステップテラス構造を有し、前記ステップテラス構造における前記ステップsの平均高さhが0.25nm以上3nm

以下であり、前記主面の(0001)面に対する傾斜角をθとするとき、前記主面内のいずれかの場所において、前記ステップsに沿う方向に対して垂直な方向に、前記ステップsと前記テラスtとが連続する10対の前記ステップテラス構造におけるテラス幅W1〜W10のうち90%以上が、W0=h/tanθで求まる平均テラス幅W0との相対誤差が10%以内にある。

(もっと読む)

半導体成膜用基板の製造方法

【課題】表面に凹凸部を設けた半導体成膜用基板の、真の製造効率を向上させるための製造方法を提供すること。

【解決手段】基板の表面に部分的にマスクを形成する工程と、ドライエッチング法を用いて前記基板の表面の前記マスクに覆われていない部分をエッチング除去して凹部を形成する工程とを、この順に行うことにより、基板の表面に凹凸部を設ける。凹部を形成する工程においては、少なくとも最後に基板のエッチング速度をマスクのエッチング速度の半分〜2倍とすることによりデポジションを抑制しながらエッチングを行ったところでエッチングを終了する。半導体の成膜に適さない不良基板の発生が抑えられるので、基板の真の製造効率が改善される。

(もっと読む)

エピタキシャルウエハの製造方法

【課題】 半導体ウエハの端面に角張った形状の結晶層を成長させることなく、半導体ウエハ上に厚い単結晶層を成長させることができる技術を提供する。

【解決手段】 半導体ウエハ10上に単結晶層30が形成されたエピタキシャルウエハの製造方法であって、平坦な上面12と、平坦な下面14と、上面12と下面14を接続する端面16を有する半導体ウエハ10の端面16上に、アモルファス層20を形成するアモルファス層形成工程と、アモルファス層形成工程後に、半導体ウエハ10の上面12上に、80μm以上の厚みを有する単結晶層30を気相成長させる単結晶層形成工程を有する。

(もっと読む)

シリコンウェーハ及びエピタキシャルウェーハ、並びにそれらの製造方法

【課題】シリコンウェーハにおける微細ダメージの直接的な抑制によって、ミリセックアニールによる熱応力にも耐えうる機械的強度を有するシリコンウェーハ及びエピタキシャルウェーハ、並びにそれらの製造方法を提供する。

【解決手段】本発明のシリコンウェーハの製造方法は、両面を鏡面研磨したシリコンウェーハ(10)の端面を含む表面全体に、膜厚が10nm以上の酸化膜(20)を形成する工程と、該酸化膜(20)を除去して表面に存在する微細ダメージを低減する工程とを含む。また、本発明のエピタキシャルウェーハの製造方法は、両面を鏡面研磨したシリコンウェーハ(10)の端面を含む表面全体に、膜厚が8nm以上の酸化膜(20)を形成する工程と、該酸化膜(20)を除去して表面に存在する微細ダメージを低減する工程と、酸化膜(20)を除去したシリコンウェーハの表面に、エピタキシャル層(30)を形成する工程とを含む。

(もっと読む)

半導体装置の製造方法

【課題】パターン付きウェーハの金属及び有機物の汚染を非破壊で短時間で測定し、処理条件を適正化して後続のウェーハの処理を行う高生産性の半導体装置の製造方法を提供する。

【解決手段】第1基板11の第1主面11a上に、導電膜及び誘電膜の少なくともいずれかを含み第1パターンを有する第1層21を形成し、前記第1層が形成された前記第1主面に対向して設けられた探針30と、前記第1基板と、の間の相対位置を前記第1主面に平行な平面内で変化させ、前記探針に発生する電気信号を検出し、前記電気信号に基づいて設定された条件を用いて、第2基板の第2主面上に、導電膜及び誘電膜の少なくともいずれかを含み第2パターンを有する第2層を形成することを特徴とする半導体装置の製造方法が提供される。

(もっと読む)

インジウムリン基板の製造方法、エピタキシャルウエハの製造方法、インジウムリン基板およびエピタキシャルウエハ

【課題】電気特性の悪化を抑制するとともに、PL特性の悪化を抑制することができるInP基板の製造方法、エピタキシャルウエハの製造方法、InP基板およびエピタキシャルウエハを提供する。

【解決手段】InP基板の製造方法は、以下の工程(ステップ)を備えている。InPインゴットを準備するS1。このインゴットは、InPからなっていてもよく、Fe、S、Sn、およびZnからなる群より選ばれた少なくとも一種の物質よりなるドーパントを含んでいてもよい。次に、準備したインゴットからInP基板をスライス加工した後S2、InP基板を、研磨剤、化学研磨液などを用いて研磨しS3、InP基板を準備する。次に、研磨したInP基板を前処理するS4。前処理により、研磨剤、化学研磨液などを除去する。続いてInP基板を硫酸過水で洗浄しS5、この後、InP基板をリン酸で洗浄するS6。

(もっと読む)

炭化珪素半導体装置の製造方法

【課題】製造工程の途中でエピ膜厚を測定できる手段を提供する。

【解決手段】半導体基板1の表面にn型エピ層2を成膜すると、第1、第2の溝4a、4bの外側ではn型エピ層2が成膜されるが、これらの間となる突出部5の上にはn型エピ層2が成膜されない。このため、これらの高さの差、つまり段差を測定することにより、n型エピ層2を測定することができる。すなわち、これら各部において、測定装置から測定対象の最表面までの距離を求め、その差を測定することにより、半導体基板1の表面に成長したn型エピ層2の膜厚を測定することが可能となる。

(もっと読む)

エピタキシャルウェハの製造方法、欠陥除去方法およびエピタキシャルウェハ

【課題】膜厚分布が均一なエピタキシャル膜を有するとともに、平坦度に優れたエピタキシャルウェハを簡単な工程で製造することのできるエピタキシャルウェハの製造方法およびエピタキシャルウェハを提供すること。

【解決手段】CZ法により得られたシリコン単結晶インゴットを薄円板状に切り出してウェハを得る(ステップS1)。次に、ウェハの表面を研削(ラッピング)して平面化する(ステップS2)。次に、エッチングによる化学研磨を行った(ステップS3)後、ウェハの両面を粗研磨する(ステップS4)。粗研磨終了後、気相エッチングを行い(ステップS5)、その後、エピタキシャル膜を形成する(ステップS6)。そして、エピタキシャル膜が形成されたウェハに対して仕上げ研磨を行い(ステップS7)、最終洗浄を行った(ステップS8)後、終了する。

(もっと読む)

半導体発光素子用テンプレート基板、半導体発光素子用テンプレート基板の製造方法、半導体発光素子の製造方法及び半導体発光素子

【課題】光取り出し効率に優れた半導体発光素子を高い収率で製造が可能な半導体発光素子用テンプレート基板とその製造方法等を提供する。

【解決手段】表面に複数の凸部102が形成された基板101と、基板101の複数の凸部102が形成された面上に成膜されたIII族窒化物半導体からなるバッファ層12と、を少なくとも有し、凸部102が形成された基板101の表面の、均一な形状に形成されていない凸部102が占める面積の割合を示す不良面積率が10%以下である半導体発光素子用テンプレート基板I0。

(もっと読む)

半導体製造方法と装置

【課題】部分的に絶縁膜が形成されているシリコン基板上を単結晶で覆うことができる半導体装置の製造方法及び基板処理装置を提供する。

【解決手段】部分的に絶縁膜が形成されたSi基板10上に、a−Si膜14を成膜する(図1(b))。このSi基板10を熱処理すると、基板のSi結晶を種としてa−Siが固相Epi化される(図1(c))。基板の厚さ方向に対して充分にEpi結晶化された範囲を保護するようにレジスト膜18を形成し(図1(d))、エッチング処理を行い(図1(e))、その後、アッシング処理によってレジスト膜18を剥離し、このSi基板10上に再度a−Si膜を成膜する(図1(f))。再度、上記熱処理を行うことで、a−Siが固相Epi化される(図1(g))。

(もっと読む)

III族窒化物結晶基板ならびに発光デバイスおよびその製造方法

【課題】発光デバイスに好適に用いられるIII族窒化物結晶基板ならびにその基板を含む発光デバイスおよびその発光デバイスの製造方法を提供することを目的とする。

【解決手段】本III族窒化物結晶基板は、面積が10cm2以上の主面を有し、主面の外周からの距離が5mm以下の外周領域を除く主領域において、総転位密度が1×104cm-2以上5×105cm-2以下であり、総転位密度に対する螺旋転位密度の比が0.5以上である。

(もっと読む)

1 - 20 / 44

[ Back to top ]