Fターム[5F046EA12]の内容

半導体の露光(電子、イオン線露光を除く) (57,085) | 位置合わせマーク (981) | 断面形状、断面構造、材質 (301) | マークが凹部 (81)

Fターム[5F046EA12]に分類される特許

1 - 20 / 81

基板作製方法

【課題】アライメントマークが形成された基板を作製するにあたって、光によるアライメントマークの検出を可能としつつ、アライメントマークを形成する時間を短縮させる。

【解決手段】基板に対してアライメントマークを形成する際の基板作製方法において、前記基板を覆うようにレジスト層を形成する工程と、前記レジスト層にエネルギービームを照射することにより、所定のパターンの描画又は露光を行う露光工程と、前記描画又は露光されたレジスト層を現像し、凹凸からなるレジストパターンを形成するレジストパターン形成工程と、前記レジストパターン形成工程後、前記レジストパターンを有する部分における基板の少なくとも一部に対してウェットエッチングを行い、前記一部におけるレジストパターンの凹部よりも大きく、且つ、光を用いて検出可能な大きさを有するアライメントマークを前記基板上に形成するアライメントマーク形成工程と、を有する。

(もっと読む)

半導体装置の製造方法

【課題】より視認が容易なアライメントマークを簡素な工程で形成することが可能な、半導体装置の製造方法を提供する。

【解決手段】半導体基板SUBの主表面上に、主表面に対して段差を有するパターンMKが形成される工程と、パターンMK上に、半導体材料を含む第1の半導体層PS1が形成される工程と、第1の半導体層PS1上に、半導体材料を含む第2の半導体層PS2が形成される工程と、第2の半導体層PS2上にレジストパターンRSが形成される工程とを備えている。レジストパターンRSが形成される工程において、パターンMKが位置合わせマークとして用いられる。

(もっと読む)

アライメントマーク基板、素子、および素子の製造方法

【課題】透明導電部をパターン状に形成し、これに対応するようにパターン状の機能層を積層する際に、精度良くアライメントすることが可能なアライメントマーク付き基板を提供する。

【解決手段】基板11と、上記基板11上に形成され、表面に凹部状に形成されたアライメント用凹部13を有するアライメントマーク層12と、を有することを特徴とするアライメントマーク基板10で、アライメントマーク層12上に透明電極または透明半導体等の透明導電部21を形成し、さらに透明導電部21上に機能層22を形成する際に、アライメント用凹部13を基準とすることにより上記透明導電部21が透明なものであっても正確にアライメントすることができる。

(もっと読む)

ワイドギャップ半導体基板およびワイドギャップ半導体装置の製造方法

【課題】ワイドギャップ半導体基板の位置検出を、可視光を用いて高精度に行う。

【解決手段】一実施形態によれば、ナローギャップ半導体基板(例えばSi基板2)の主面の所定の位置に彫り込み型のアライメントマーク4が形成されたナローギャップ半導体基板のその主面上にワイドギャップ半導体層(例えばGaN層19)をエピタキシャル成長したことにより、基板位置決め用のアライメントマークが予め埋め込まれているワイドギャップ半導体基板を提供する。

(もっと読む)

半導体装置の製造方法

【課題】アライメントマーク形成工程時のエピタキシャル層の侵食を低減させる手段を提供すること。

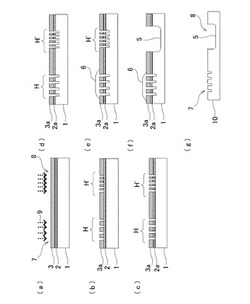

【解決手段】異方性エッチングすることにより、アライメントマークの段差21の側壁にのみ珪素系膜22を形成する。段差21の側壁に珪素系膜22が形成されることにより、エピタキシャル層30がアライメントマーク領域A全体に積層された場合であっても、側壁においてエピタキシャル層30の成長を抑制させることができ、段差21は順テーパー形状を維持することが可能となる。

(もっと読む)

半導体装置の製造方法

【課題】スーパジャンクション構造と後の工程との位置合わせをとる必要があるため、通常、スーパジャンクション構造の形成前に、半導体基板を掘り込んでリセス部を形成して、このリセス部等をアライメントマークとして使用する。そして、後のスーパジャンクション構造形成工程中に、このアライメントマークが損傷を受けないように、アライメントマーク上を酸化シリコン膜等の絶縁膜で被覆している。しかしながら、このようにしても、被覆酸化膜を貫通して、損傷がシリコン基板に至り、アライメントマークを破壊することがあることが、本願発明者等により、明らかにされた。

【解決手段】本願発明は、スーパジャンクション構造を有する半導体装置の製造方法において、スーパジャンクション構造と後の工程との位置合わせのためのアライメントマークを、スーパジャンクション構造の形成後に、作製するものである。

(もっと読む)

半導体基板及び半導体基板の製造方法

【課題】半導体基板のアライメントマークを繰り返し使用する。

【解決手段】ベース基板にアライメントマークを形成する段階と、アライメントマークを形成する段階の後に、ベース基板上のアライメントマークを含む領域に、結晶成長を阻害する阻害層を形成する段階と、アライメントマークの位置を基準とする開口を形成すべき位置を示す情報に基づいて、阻害層におけるアライメントマークが設けられていない領域に、ベース基板を露出する開口を形成する段階と、開口内に半導体結晶を成長させる段階とを備える半導体基板の製造方法を提供する。

(もっと読む)

炭化珪素半導体装置の製造方法

【課題】製造工程が増加したり複雑化したりすることなく、SiC半導体基板とマスクとの位置合わせを高精度に行うことができるSiC半導体装置の製造方法を提供する。

【解決手段】アライメントマーク形成領域R1に、開口部の形状が、オフ方向に対して対称であり、かつオフ方向の最も下流側に位置する部分に頂点を有する多角形状とされており、アライメントマークとなるトレンチ12を形成するトレンチ形成工程と、トレンチ形成工程を行った後、SiC半導体基板10に対して、エピタキシャル層13を成長させるエピタキシャル層成長工程、または熱処理する熱処理工程の少なくともいずれか一方を行う工程と、エピタキシャル層成長工程または熱処理工程の少なくともいずれか一方の工程を行った後、アライメントマークを基準としたマスク合わせによってSiC半導体基板10にマスクを配置する工程と、を含むSiC半導体装置の製造方法とする。

(もっと読む)

インプリント・リソグラフィの散乱計測アラインメント

【課題】インプリント・リソグラフィによって基板上にパターンを形成するシステムを提供する。

【解決手段】インプリント・ヘッド3100はインプリント・ヘッド支持体3910に取り付けられている。インプリント・ヘッド3910はインプリント・ヘッドが常に固定位置に留まるように取り付けられている。使用中、X−Y面に沿ったすべての動きはモーション・ステージ3600によって基板に対して実行される。システム3900は硬化液を基板上に分配する液体分配システムも備える。液体分配システムは、インプリント・ヘッド3100に結合される。インプリント・リソグラフィは液体を基板上に分配するプロセスである。テンプレートが液体に接触され、液体が硬化される。硬化した液体はテンプレート内に形成されるパターンのインプリントを含む。一実施形態では、基板上に予め形成された層に対するテンプレートの整列は散乱計測を用いて行われる。

(もっと読む)

半導体素子及びその製造方法

【課題】リングゲートにサイドスペーサが形成されている場合においても小径のビアホールを形成可能とする半導体素子及びその製造方法を提供する。

【解決手段】半導体素子30は、第1アライメントマーク2を有する半導体基板1と、半導体基板1上に形成されて中央開口部を有するリング状のゲート6と、ゲート6の内周面に形成されたサイドスペーサ8と、半導体基板1上に第1のアライメントマーク2,ゲート6,及びサイドスペーサ8を覆って形成されて第1アライメントマーク2に対応する位置に第2アライメントマーク11を有する第1絶縁膜10と、第1絶縁膜10を貫通すると共にゲート6の中央開口部を通って半導体基板1に接続するコンタクト部17と、第1絶縁膜10上に第2アライメントマーク11を覆って形成された第2絶縁膜19と、コンタクト部17に接続する配線層23と、を備える。

(もっと読む)

半導体装置の製造方法

【課題】半導体素子構造を構成する半導体層の成長用基板として、該半導体層と同種の半導体材料を用いる場合に、半導体層を成長した後の露光時に認識可能なアライメントマークを形成できるようにする。

【解決手段】アライメントマーク検出用光源に対して透明な材料からなる基板101の上に、該基板101と異なる屈折率を有する材料からなる第2のアライメントマーク120を形成する。続いて、基板101の上に、活性層105を含むGaN系エピタキシャル層を第2のアライメントマーク120を埋め込むように成長する。続いて、第2のアライメントマーク120を参照しながら、GaN系エピタキシャル層に対する露光の位置合わせを行う。

(もっと読む)

位置検出方法

【課題】アライメントマークを用いて基板とフォトマスクとの位置合わせを行う時の検出精度を向上させることができる位置検出方法を提供する。

【解決手段】内側が段差によって外側と区切られたアライメントマークが形成された基板上に、レジストを塗布し、基板にアライメント検出光を照射し、アライメントマークの内側の中央部と端部との、レジストの塗布膜厚の差異に起因する反射光の強度変化を観察することにより、アライメントマークの位置を検出する方法において、反射光の強度が、アライメントマークの内側の端部に比較してアライメントマークの内側の中央部の方が強くなる様に、レジストの塗布膜厚を調整する。

(もっと読む)

アラインメントマーク配置及びアラインメントマーク構造

【課題】アラインメントコントラスト及び正確性を改善するための新しい解決策を提供する。

【解決手段】

アラインメントマーク配置は、基板上にある複数の互いに平行な第一ストライプを含み、各第一ストライプは第一サイズを有する第一アラインメントパターンと、第一アラインメントパターンの真上に設けられ、第一アラインメントパターンと重なる複数の互いに平行な第二ストライプを含み、各第二ストライプは、第一アラインメントパターンの各第一ストライプの第一サイズより大きい第二サイズを有する第二アラインメントパターンとを含む。

(もっと読む)

重ね合わせ測定マーク及びパターン形成方法

【課題】重ね合わせ測定の精度を向上できる重ね合わせ測定マークを提供する。

【解決手段】第1パターンと第2パターンの重ね合わせ測定のためのマークにおいて、プラグ用ホールの開口パターンからなる第1パターンが形成された層間絶縁膜に該プラグ用ホールと同時に形成された第1ホールの開口パターンからなる第1マークと、前記層間絶縁膜に第1ホールと同時に形成され、前記プラグ用ホールの開口サイズと同程度で且つ第1ホールの開口サイズより小さい開口サイズを有する第2ホールの開口パターンからなる第2マークと、前記層間絶縁膜上の導電膜上に形成されたレジスト膜をパターニングして第2パターンと同時に形成されたレジストパターンからなる第3マークを含む構成とする。

(もっと読む)

荷電粒子ビーム描画方法、荷電粒子ビーム描画用の基準マークの位置検出方法及び荷電粒子ビーム描画装置

【課題】試料に形成された段差を有する基準マークのエッジラフネスの影響を受けることなく、基準マークの位置を再現性良く検出することが可能な荷電粒子ビーム描画方法、荷電粒子ビーム描画用の基準マークの位置検出方法及び荷電粒子ビーム描画装置を提供する。

【解決手段】ステージをXY方向に動かして該ステージに載置された試料Mに形成された段差を有する基準マークFM’に対して光てこ式の高さ測定器の投光光を走査し、その反射光の強度の変化を検出し、その反射光の強度が変化したときのステージのXY位置を検出し、検出したXY位置を基準マークFM’の位置Cとして検出し、検出した基準マークFM’の位置Cから試料Mに存在する位相欠陥Dの位置を特定し、特定した位相欠陥Dの位置との関係で描画位置を決定する。

(もっと読む)

埋込拡散シリコンエピタキシャルウェーハの製造方法

【課題】シリコン単結晶基板の主裏面に欠陥がない埋込拡散シリコンエピタキシャルウェーハの製造方法を提供する。

【解決手段】シリコン単結晶基板1の主表面に積層された第1シリコンエピタキシャル層3にアライメントマーク7を形成する第1の工程と、アライメントマーク7が形成された第1のシリコンエピタキシャル層3に不純物拡散層13a,20aを形成する第2の工程と、不純物拡散層13a,20aが形成された第1のシリコンエピタキシャル層3の上に第2シリコンエピタキシャル層3aを積層する第3の工程と、第2の工程と第3の工程を所定回数繰り返す第4の工程とを有する。そして、アライメントマーク7の形成終了時にシリコン単結晶基板1の主裏面側に形成されている主裏面側酸化膜42をデフォーカス防止用酸化膜として、埋込拡散シリコンエピタキシャルウェーハ100を製造する。

(もっと読む)

アライメントマークの検出方法及び装置

【課題】アライメント顕微鏡の撮像素子に写し出されるワークマークの見え方が異なったとしても、ワークマークを正しく検出することができるようにすること。

【解決手段】アライメント顕微鏡10を使って、ワークWの表面画像を受像し、ワークマークWAMとして登録すべき見え方(形状や明暗や色調)の異なる複数のパターンを、ワークマークWAM1〜nとして制御部11の記憶部11bに登録する。ワークマークを検出する際には、このワークマークWAM1〜nを使って、検索領域内のパターンを検索し、比較・評価部11cで、登録されているワークマークWAM1〜nと検索領域内のパターンとを比較して一致度のスコアを求め、スコアが例えば一定値を越えていると、このパターンをワークW上のワークマークWAMと判定する。このワークマークWAMを使って位置合わせ制御部11eはマスクMとワークWの位置合せを行う。

(もっと読む)

パターニング方法

【課題】基板の表裏に片面ずつリソグラフィパターンをパターニングするときに、基板の表裏両面で相互に正確に位置合わせされたリソグラフィパターンを設けるパターニング方法を提供する。

【解決手段】まず、ガラス基板21の端に、ガラス基板21の表面21a,21bに対して垂直な切り欠き22を設ける。次に、アライメントマーク33,34が切り欠き22に合致するように第1マスク31をガラス基板21に位置合わせして配置し、ガラス基板21のオモテ面21aに第1マスクパターン32に応じたリソグラフィパターンをパターニングする。そして、ガラス基板21を裏返し、ウラ面21bを上方に露呈させ、アライメントマーク43,44が切り欠き22に合致するように第2マスク32をガラス基板21に位置合わせして配置し、ガラス基板21のウラ面21bに第2マスクパターン42に応じたリソグラフィパターンをパターニングする。

(もっと読む)

半導体装置の製造方法

【課題】 従来の半導体装置の製造方法では、製造工程を煩雑とせず、遮光性の膜に対するアライメントマークを形成することが困難であるという問題があった。

【解決手段】 本発明の半導体装置の製造方法では、基板3、エピタキシャル層4に溝部9、分離用トレンチ16を形成する工程を利用し、スクライブライン領域2にアライメントマーク形成用の溝部15を形成する。溝部15内には、HTO膜19、多結晶シリコン膜20を堆積し、加工することで、アライメントマークとしての凹部24、25を形成する。この製造方法により、製造工程を簡略化し、アライメントマークを形成できる。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】アライメント精度を高める。

【解決手段】半導体装置100は、基板102と、基板102上に形成され、金属膜により構成されたアライメントマーク110と、アライメントマーク110上に形成され、アライメントマーク110の表面全体を覆うカバー絶縁膜104と、カバー絶縁膜104上に形成され、平面視において、アライメントマーク110上で開口するとともに端面108aがアライメントマーク110の端面110aと一致する開口部108が形成されたポリイミド膜106とを含む。

(もっと読む)

1 - 20 / 81

[ Back to top ]