Fターム[5F046EA20]の内容

半導体の露光(電子、イオン線露光を除く) (57,085) | 位置合わせマーク (981) | 断面形状、断面構造、材質 (301) | マークが結晶面で構成されているもの (10)

Fターム[5F046EA20]に分類される特許

1 - 10 / 10

炭化珪素半導体装置の製造方法

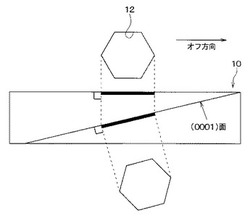

【課題】製造工程が増加したり複雑化したりすることなく、SiC半導体基板とマスクとの位置合わせを高精度に行うことができるSiC半導体装置の製造方法を提供する。

【解決手段】アライメントマーク形成領域R1に、開口部の形状が、オフ方向に対して対称であり、かつオフ方向の最も下流側に位置する部分に頂点を有する多角形状とされており、アライメントマークとなるトレンチ12を形成するトレンチ形成工程と、トレンチ形成工程を行った後、SiC半導体基板10に対して、エピタキシャル層13を成長させるエピタキシャル層成長工程、または熱処理する熱処理工程の少なくともいずれか一方を行う工程と、エピタキシャル層成長工程または熱処理工程の少なくともいずれか一方の工程を行った後、アライメントマークを基準としたマスク合わせによってSiC半導体基板10にマスクを配置する工程と、を含むSiC半導体装置の製造方法とする。

(もっと読む)

エピタキシャルウェーハおよびその製造方法

【課題】エピタキシャル膜成膜後にもレーザー干渉によるアライメント検出を可能とし、レーザー干渉によるアライメント可能な信号強度を得られるアライメントマークの最適寸法を提供する。

【解決手段】断面形状が方向性を有するビームで走査するアライメントマークMの形成された表面にエピタキシャル層を成膜したウェーハであって、アライメントマークは、複数の矩形状マークが断続的に配されて前記ビーム走査方向と略直交する方向に延在する直線状マークとされ、直線状マークにおける矩形状マークが、エピタキシャル膜の表面からビーム走査した際に、回折光強度が識別可能な形状で配置されてなる。

(もっと読む)

合せマークおよびその製造方法

【課題】合せマークの検出時における位置の特定を容易にする手段を提供する。

【解決手段】合せマークが、シリコン基板と、シリコン基板のおもて面に形成された凹部と、凹部のシリコン基板のおもて面との角部から離間して形成されたエピタキシャル層と、凹部の内面とエピタキシャル層のまでの間の前記シリコン基板のおもて面とに形成された酸化膜と、酸化膜上に形成された多結晶シリコン層とを備える。

(もっと読む)

半導体装置の製造方法

【課題】 精度の高いマスクのアライメントを行うことができる半導体装置の製造方法を実現する。

【解決手段】 半導体基板10の基板面10aに第1アライメントマーク11を形成し、第1アライメントマーク11の上方にその形状に対応した第2アライメントマーク13が形成されるエピタキシャル層12を基板面10a上に形成する。続いて、KOH溶液を用いてエピタキシャル層12をエッチングすることにより、第2アライメントマーク13が基板面10aである(110)面と異なる方位の(111)面に沿って優先的にエッチングされるので、エピタキシャル層12の表面と第2アライメントマーク13との境界を明確にすることができる。これにより、露光装置により第2アライメントマーク13の位置及び形状を正確に認識することができ、精度の高いマスクのアライメントを行うことができる。

(もっと読む)

半導体装置の製造方法

【課題】本発明は、SiCを基板に用いた半導体装置において、製造工程の重ね合わせに用いるアライメントマークが、製造工程中の活性化アニール処理やエピタキシャル成長などの熱処理工程で非対称に変形することを防止することができる半導体装置の製造方法を提供することを目的とする。

【解決手段】本発明は、SiCを基板に用いた半導体装置を製造する方法であって、SiC基板1の{0001}面に、アライメントマーク2を形成する工程と、アライメントマーク2に基づき、転写マスクとSiC基板1との位置合わせを行いSiC基板1上に所定のパターンを形成する工程とを備える。

(もっと読む)

半導体装置の製造方法

【課題】高温アニール後でも高精度なマスク合わせができるアライメントマークを提供する。

【解決手段】基板1の主面に、段差パターン2をなす溝部を形成する。そして、溝部を覆うようにカーボン膜3を形成してアライメントマーク10を形成する。カーボン膜3は耐熱性であるため、カーボン膜3により溝部を覆うことで、高温アニール後に溝部の形状が崩れるのを防ぐことができる。溝部形状の崩れが抑制されることで、高温アニール後も高精度のマスク合わせができる。

(もっと読む)

アライメントマーク及びその形成方法、半導体装置及びその製造方法

【課題】エピタキシャル成膜工程や高温アニール工程を経ても、位置合わせ精度の低下が抑制されるアライメントマークを提供する。

【解決手段】アライメントマーク14を、断面形状が階段状の段差パターンにより形成する。段差パターンは、基板2の主面を掘り下げて形成された第1段差パターン11と、基板2の主面を掘り下げた第1段差パターン11の下方に、第1段差パターン11に連続して更に基板2の主面を掘り下げて形成された第2段差パターン13と、を有している。そして、第1段差パターン11の側壁部17と、第2段差パターン13の側壁部18とが、同一の角度で形成され、かつ同一の結晶方位を有するように形成する。

(もっと読む)

半導体装置の製造方法

【課題】チップ領域に素子形成用パターンを形成するとき、スクライブ領域に整列キーのキャッピング層を形成する半導体装置の製造方法を提供する。

【解決手段】半導体基板200のチップ領域201にアクティブ領域を限定する素子分離膜241を形成し、スクライブ領域205に半導体基板200の表面に対して段差を有する整列キー245を形成するステップと、半導体基板200上に少なくとも一つの素子形成層を形成するステップと、素子形成層を変形させて、チップ領域201の半導体基板200上に素子形成用パターン251を形成し、スクライブ領域205の半導体基板200上に整列キー245をキャッピングするキャッピング層255を形成するステップと、を含む。

(もっと読む)

位置合わせ装置への2次元フォトニック結晶の応用

【課題】スクライブ・レーンのスペースを減少させることを可能にし、基板のスペースのより効率の良い使用を可能にする位置調整用マークを提供すること。

【解決手段】本発明は基板で使用するための位置調整用マークに関し、この位置調整用マークは、構造体の周期的な2次元配列からなり、構造体の間隔は位置合わせビームよりも小さいが、露光ビームよりも大きい。

(もっと読む)

チップ部品のパターニング処理方法及びチップ製品の製造方法

【課題】 個々に分離されたチップ部品に対してもパターニング処理を容易に行うことの

できるチップ部品のパターニング処理方法及びこれを用いたチップ製品の製造方法を提供

する。

【解決手段】 本発明のチップ部品12Aのパターニング処理方法は、露光装置を用いて

チップ部品に対するパターニング処理を行う方法であって、前記露光装置に対応し、表面

に凹部11a〜11dを備えた支持基板10が用意され、前記凹部に前記チップ部品が収

容され位置決めされた状態で、前記露光装置により前記支持基板のアライメントが行われ

るアライメント工程と、前記露光装置により前記チップ部品の表面に塗布された感光性材

料15に露光処理が施される露光工程とを有することを特徴とする。

(もっと読む)

1 - 10 / 10

[ Back to top ]