Fターム[5F047AB00]の内容

ダイボンディング (10,903) | 支持体の構造 (201)

Fターム[5F047AB00]の下位に属するFターム

Fターム[5F047AB00]に分類される特許

1 - 16 / 16

半導体装置

半導体装置、その製造方法及びそれを備えた実装体

【課題】半導体素子を実装する際に、位置ずれが生じることを防ぎ、信頼性が高い半導体装置が得られるようにする。

【解決手段】

半導体装置は、第1の面14a及び該第1の面14aと反対側の第2の面14bを有する基板14と、基板14の第1の面14aに固着された半導体素子11と、基板14の第1の面14aから第2の面14bまでを貫通するように形成された第1の透明樹脂部15と、基板14の第2の面14b側における第1の透明樹脂部15の上に形成されたアライメントパターン17とを備えている。

(もっと読む)

半導体装置

【課題】電子部品中の電気的接合部の接合層に関し、鉛成分を含有せず先行技術よりもより高い接合強度・破壊靱性が得られる接合材を接合層として有する半導体装置を提供する。

【解決手段】本発明に係る半導体装置は、電子部材同士が接合層を介して電気的に接続されている半導体装置であって、前記接合層は、Agマトリックスと、前記Agマトリックス中に分散しAgよりも硬度が高い金属Xからなる分散相とを含み、前記Agマトリックスと前記金属X分散相とは互いに金属接合し、前記Agマトリックスと前記電子部材の最表面とは互いに金属接合し、前記金属X分散相と前記電子部材の最表面とは互いに金属接合しており、前記金属X分散相は1μm以下の結晶粒を含み、前記Agマトリックスは100 nmよりも小さな結晶粒を含んでいることを特徴とする。

(もっと読む)

半導体装置

【課題】半導体チップの裏面をアイランドやダイパッドなどのチップ接合部の接合面に接合させるためにはんだ接合剤を用いても、半導体チップの損傷の発生を防止することができる半導体装置を提供する。

【解決手段】樹脂基板4の一方面5には、平面視矩形状のアイランド6と、このアイランド6の4つの各角部から延出する延出部8とが一体的に形成されている。アイランド6の表面7は、半導体チップ1の裏面10がはんだ接合剤11を介して接合される接合面であり、半導体チップ1の裏面10の面積よりも小さな面積を有している。

(もっと読む)

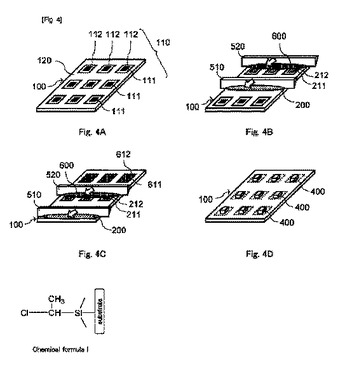

部材の配置方法

部材の配置方法は、基板と第1の液体を準備する工程と、部材及び第2の液体を含有する部材含有液を準備する工程と、親水性領域に第1の液体を配置する工程と、前記親水性領域に配置された前記第1の液体に前記部材含有液を接触させる工程と、前記第1の液体および前記第2の液体を除去することによって、前記部材を前記親水性領域に配置する工程と、を具備する。前記親水性領域は、部材配置領域と、前記部材配置領域の周辺に形成された液体捕捉領域とから構成されている。前記液体捕捉領域は、以下の化学式Iで表される表面を具備する。

(もっと読む)

(もっと読む)

接合構造

【課題】金属板に半導体素子を接合する場合など、異なる材料間の接合面に生じる熱応力を低減してクラックの発生を防止した接合構造を提供する。

【解決手段】アルミニウム板2に半導体チップ1を接合し、アルミニウム板2における半導体チップ1の四隅近傍に亜鉛体4を埋設することにより、半導体チップ1やアルミニウム板2に温度変化が発生した場合でも、亜鉛体4の熱応力によって半導体チップ1とアルミニウム板2との接合面に生じる残留応力を緩和し、繰り返し使用時には、アルミニウム板2の繰り返しの疲労を軽減し、寿命を延ばすことができる。したがって、半導体チップ1の角部、アルミニウム板2の領域2b、領域2b上の接合剤3において、クラックの発生を抑制することができる。

(もっと読む)

半導体装置

【課題】半導体装置のプリント配線基板上に半導体チップを搭載するための接着剤が流出してプリント配線基板上の接続用電極を汚染することによるボンディングワイヤ不着を防止する。

【解決手段】平板状の基材8の一面の一部に導体が形成され、導体の一部及び基材の一面の一部上にソルダーレジスト6が設けられたプリント配線基板1と、プリント配線基板の主面に接着剤11を介して搭載された半導体チップ9と、半導体チップに形成されたチップ電極10とプリント配線基板の主面に形成された接続用電極7とを接続するボンディングワイヤ12とを備え、接続用電極と半導体チップとの間には、接続用電極から近い順に、基材が露出した第1の基材露出部8aと、導体及びソルダーレジストからなる堰き止め部と、基材上に直接ソルダーレジストが形成されているソルダーレジスト凹部6cとが設けられている半導体装置とした。

(もっと読む)

位置合わせ性に優れたはんだペーストを用いた基板と被搭載物の接合方法

【課題】はんだペーストを用いて基板に対して被搭載物を同じ位置および方向となるように接合する方法を提供する。

【解決手段】メタライズ層を形成した基板におけるメタライズ層とメタライズ層を形成した正方形状を有する被搭載物4におけるメタライズ層との間にはんだペースト3を搭載または塗布したのちリフロー処理して基板と正方形状を有する被搭載物4をはんだペーストを用いた基板と正方形状を有する被搭載物を接合する際に、前記基板の表面に形成されるメタライズ層の面積が被搭載物4のメタライズ層の面積よりも小さいメタライズ層本体部分6と前記メタライズ層本体部分6の周囲から突出した少なくとも2個のはんだ誘引部メタライズ層7とからなる平面形状を有していると、リフロー処理中に正方形状の被搭載物4の対角線と前記はんだ誘引部メタライズ層7の突出方向とが一致するように回転してはんだ付けされる。

(もっと読む)

位置合わせ性に優れたはんだペーストを用いた基板と被搭載物の接合方法

【課題】はんだペーストを用いて基板に対して被搭載物を同じ位置および方向となるように接合する方法、特にAu−Sn合金はんだペーストを用いて基板に対して素子を同じ位置および方向となるように接合する方法を提供する。

【解決手段】メタライズ層を有する基板のメタライズ層とメタライズ層を有する被搭載物のメタライズ層との間にはんだペースト3を搭載または塗布したのち非酸化性雰囲気中でリフロー処理して基板と被搭載物を接合するはんだペーストを用いた基板と被搭載物の接合方法において、前記基板のメタライズ層を図1(a)のように面積が被搭載物4のメタライズ層の面積よりも小さいメタライズ層本体部分6と前記メタライズ層本体部分6の周囲から突出したはんだ誘引部7とからなる平面形状を有するようにすると、被搭載物が図1(b)の如くはんだ誘引部7の方向に揃ってはんだ付けされる。

(もっと読む)

半導体装置

【課題】はんだボールの発生がなく、チップのθ回転を含む位置ずれを低減した高精度の半導体装置を提供する。

【解決手段】マウント面121を有する実装部材120と、はんだによりマウント面121に接合された半導体チップ140と、を備え、マウント面121の半導体チップ140の周囲には、第1の領域141と、半導体チップ140を囲み、前記はんだに対する濡れ性が第1の領域41よりも低い第2の領域160と、が設けられている。

(もっと読む)

圧電デバイス

【課題】基板の配線上に絶縁膜が形成され、その上に電子部品が搭載される圧電デバイスにおいて、絶縁膜と電子部品との間に気泡が残らず安定した電子部品の密着性を確保した圧電デバイスを提供する。

【解決手段】配線31を備えた樹脂基板30と、樹脂基板30のIC配置領域39に配置されたICチップ20と、ICチップ20の上方に位置した水晶振動子と、樹脂基板20と水晶振動子との間に所定の間隔を保って水晶振動子の外部端子と樹脂基板30とを接続する複数の接続部材と、を有する水晶発振器において、樹脂基板30のIC配置領域39において、配線31の一部から分岐されて延長された複数の線状導体36が、IC配置領域39内の配線31間の隙間を埋めるようにお互いに接触せずに配置され、さらに少なくともIC配置領域39に存在する配線31および線状導体36を被覆するように絶縁膜38が形成されている。

(もっと読む)

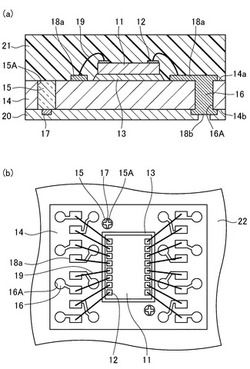

ボンディング装置及びボンディング装置における回路基板の吸着方法

【課題】ボンディング装置において、湾曲した回路基板の吸着固定と加熱とを同時に行う。

【解決手段】搬送ガイド13の間に、搬送された回路基板12を上面の基板吸着面15に吸着保持し、吸着した回路基板12を加熱するヒートブロック10を設ける。ヒートブロック10の基板吸着面15には孔19が設けられており、真空吸引ベローズ18を含む真空吸引パッド16が取りつけられ、真空吸引パッド16は真空装置に接続されている。真空吸引パッド16内の空気を真空装置に吸引しながらヒートブロック10を回路基板12に向かって上昇させて、真空吸着ベローズ18によって回路基板12を吸引して回路基板12を基板吸着面15に吸着固定すると同時に加熱する。

(もっと読む)

半導体装置の製造方法

【課題】 チップサイズの小型化を実現しつつチップのダイボンディングを可能にする半導体装置の製造方法を提供する。

【解決手段】 本発明に係るVCSELの製造方法は、100μm角以下に切断され、かつ一様に離間されたチップ12を支持するダイボンディングテープ14をサブマウント16上に載せ、その後、サブマウント16をチップ12の外形よりも大きな外形に切断し、実装用チップ30を作成する。実装用チップ30は、ダイボンダー用コレット20により吸着できる程度のサイズを有しており、コレット30に把持された実装用チップ30がダイパット32上に搬送する、ダイボンディングされる。

(もっと読む)

半導体パッケージ

【課題】センサチップへの振動や衝撃の影響を抑制すると共に、温度が変化する環境下においてもセンサチップを安定して動作させる手段を提供する。

【解決手段】有底のケース体と、ケース体に収納されるセンサチップとを備えた半導体パッケージにおいて、ケース体の底板に、センサチップより大きい凹部を設けると共に、凹部の内壁に固定される支持枠と、センサチップを貼付する取付部と、弾性を有し、取付部と支持枠とを接続する梁部とを備えた衝撃吸収部材を設ける。

(もっと読む)

回路基板およびそれを用いた電子装置並びにその製造方法

【課題】 電子素子を回路基板に搭載する際に、電子素子と回路基板とを介するろう材の溶融状態が確認できなくても、電子素子を安定して確実に搭載できる回路基板を提供することにある。

【解決手段】 表面に電子素子の搭載部2を有するとともに、搭載部2に第1のろう材からなる接合パッド4が形成され、搭載部2を除く表面に第2のろう材5が被着された標識部6を有する絶縁基板1を具備する。

(もっと読む)

半導体モジュール

【課題】

実装面積をチップサイズに近似できると共に、チップの裏面側電極を低抵抗で導出できる半導体装置を提供する。

【解決手段】

半導体チップ11の表面側に半田ボール等を形成して第1の外部接続端子14とする。半導体チップ11を基板16上に固着し、基板16に第2の外部接続端子17を形成する。第1の外部接続端子14と第2の外部接続端子17は高さがほぼ一致する。第1と第2の外部接続端子14、17を対向接着するように構成する。

(もっと読む)

1 - 16 / 16

[ Back to top ]