Fターム[5F047AB06]の内容

Fターム[5F047AB06]に分類される特許

1 - 20 / 38

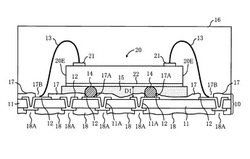

半導体装置及びその製造方法

【課題】導電箔とその保護膜が形成された絶縁基材に対して平行に半導体チップを固着し、熱膨張による応力を起因とした半導体装置の損傷の防止を図る。

【解決手段】絶縁基材11の表面上に導電箔12が配置され、導電箔12を覆って、その一部を露出する複数の第1の開口部17A、及び複数の第2の開口部17Bを有する保護膜17が配置されている。各第1の開口部17Aで露出する導電箔12の表面上に導電突起体14が配置される。表面に複数のパッド電極12を有した半導体チップ20は、その裏面が複数の導電突起体14と対向するように、ダイボンドペースト15を介して保護膜17上に固着される。各第2の開口部17Bで露出する導電箔12は、それぞれボンディングワイヤを介してパッド電極21と接続される。絶縁基材11の表面上の半導体チップ20等は、封止材16に覆われて封止される。

(もっと読む)

エレクトロニクスアセンブリを製造する方法

【課題】アンダーフィル又は接着剤によって隣接する回路素子を汚染することなく、隣接する回路素子を物理的にできる限り近づけて配置できるようにするエレクトロニクスアセンブリを製造するための方法を提供する。

【解決手段】基板12上に液体障壁30を形成することと、液体障壁の一方の側に第1の回路素子22を配置することと、液体障壁の反対側に第2の回路素子24を配置する。液体44が第1の回路素子に塗布される。第1の回路素子と第2の回路素子との間の間隔を最小にすることができるように、液体障壁を用いて、第1の回路素子に塗布された液体が第2の回路素子を汚染するのを防ぐ。

(もっと読む)

電子モジュールとその製造方法

【課題】外部振動や機械的衝撃に対して高い信頼性を確保した水晶発振器や表面弾性波デバイスを他の電子デバイスとともに搭載した電子モジュールを提供する。

【解決手段】複数の電子デバイス3a,3b、4a,4b、5a,5bの端子部を支持基板1とは反対側の面である上面に露出させて同一平面となるように配置した状態で樹脂6を用いて埋設し、各電子デバイスの露出面にある各電子部品の接続電極あるいは接続端子と接続する配線/回路パターン8を形成する。配線/回路パターン8の一部に設けた外部接続端子を半田ボール9を用いて実装機器のマザーボードに実装する。

(もっと読む)

電子装置の製造方法及び電子装置

【課題】絶縁性を確保しつつ、はんだの厚さを制御可能な電子装置の製造方法及び電子装置を提供する。

【解決手段】金属板9上にはんだ5,11を介して基板7を配置し、基板上にはんだ5を介して電子部品3,7を配置しはんだ5、11をリフロー加熱してはんだ付けする電子装置1の製造方法において、はんだ5,11の外周部に、絶縁性樹脂からなり、リフロー加熱時に溶融してはんだと密接するスペーサ21,22を配置し、リフロー加熱後に電子部品3,基板7を封止樹脂15で樹脂封止する。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】半導体パッケージ内における半導体素子の位置ずれを抑制することができる半導体装置を提供すること。

【解決手段】実施形態に係る半導体装置10は、凸部23が形成されたパッケージ基板11、導電性の接着剤25、およびパッケージ基板11上に実装された半導体素子14、を具備する。パッケージ基板11は、少なくとも2箇所に凸部23が形成された基板である。導電性の接着剤25は、凸部23を含むパッケージ基板11上に形成される。パッケージ基板11上に実装される半導体素子14は、各凸部23に係合する複数のバイアホール24を有している。さらに、半導体素子14は、少なくとも2箇所のバイアホール24が、各凸部23に接着剤25を介して係合するようにパッケージ基板11上に実装される。

(もっと読む)

半導体装置及びその製造方法

【課題】半導体装置のオン状態における素子全体にわたる抵抗成分のうち、半導体基板に起因する抵抗成分を低減することができ且つ半導体基板の裏面側からの放熱効果を向上できるようにする。

【解決手段】半導体装置は、半導体素子が形成された第1の主面と、該第1の主面の反対側の面である第2の主面とを有する半導体基板と、該半導体基板の第2の主面に固着されたリードフレーム114とを備えている。第2の主面を構成するコレクタ層8には、少なくとも1つの凹部8aが形成されている。リードフレーム114における第2の主面と固着される面には、コレクタ層8に形成された各凹部8aと嵌合する凸部114aが形成されている。

(もっと読む)

半導体装置の製造方法、半導体装置、および半導体装置の製造装置

【課題】半導体チップとダイパッドの接合に用いる接着剤が必要以上に半導体チップの外側にはみ出してしまうことを抑制する。

【解決手段】図1に示すように本実施の形態の半導体装置は、半導体チップ120と、半導体チップ120と接合させるダイパッド104を有するリードフレーム100と、半導体チップ120とダイパッド104を接合する接着剤130と、を含む。本実施の形態において、ダイパッド104は、半導体チップ120の裏面の面積より開口面積が小さい凹部108を有している。凹部108には、接着剤130が充填されていない中空部106が設けられている。

(もっと読む)

回路基板の製造方法及び回路基板

【課題】耐久信頼性及び熱特性を一定以上に確保することが可能な回路基板の製造方法を提供すること。

【解決手段】導電層を有する絶縁基板と回路素子とを備え、前記絶縁基板の前記導電層と前記回路素子とがはんだにより接合される回路基板の製造方法であって、前記はんだで構成されるはんだシートに、前記絶縁基板の前記導電層と前記回路素子との間隔を規制する規制部材を配設する配設工程(ステップST1)と、前記絶縁基板、前記規制部材が配設された前記はんだシート、及び前記回路素子を、その順番で積層する積層工程(ステップST2)と、積層されている前記絶縁基板、前記はんだシート及び前記回路素子を、還元雰囲気下において加熱して前記はんだシートを溶融することによって、前記絶縁基板と前記回路素子とを接合する接合工程(ステップST3)と、を含む回路基板の製造方法である。

(もっと読む)

回路装置およびその製造方法

【課題】後工程でのリフロー処理においてダイボンドはんだ20が溶融したときに、溶融したダイボンドはんだ20がダイパッド12とダイ11の間から流失するのを阻止し、ダイ11とダイパッド12との間にボイドが形成されるのを回避して、高い接合安定性を備えた回路装置を得る。

【解決手段】ダイパッド12に載置するダイ11の周囲を囲むようにしてダム材2を形成する。ダム材2で囲われた内側領域内の全面を満たすようにダイボンドはんだ20を充填する。それにより、リフロー工程で、ダイボンドはんだ20が溶融しても溶融したダイボンドはんだ20はダム材2で囲われた内側領域内に留まっていることができ、流失することはない。それにより、ダイ11とダイパッド12との間にボイドが形成されるのは回避される。

(もっと読む)

半導体装置

【課題】半導体チップ/絶縁基板間の接合層に熱劣化が原因で亀裂が発生するのを抑制し、併せて伝熱性を向上させて長期信頼性の向上が図れる接合構造を提供する。

【解決手段】絶縁基板の回路パターン2bの上に鉛フリー半田を適用して半導体チップ3を半田マウントした半導体装置において、半導体チップ/回路パターン間の半田接合面を半導体チップの中央部下に対応する中央面域と該中央面域を囲む外周面域とに分け、かつ回路パターンには前記中央面域に対応して台形状の凸部2b−1を形成した上で、半導体チップ/回路パターン間をリフロー半田付けする。これにより、半導体チップ3の中央部下の半田接合層5は厚さが薄く、該部における伝熱抵抗も小さくなって熱劣化,亀裂発生を抑制でき、また熱膨張係数差に起因する剪断応力が集中する外周部では厚い半田層が応力を吸収緩和し、その結果としてパワーサイクル耐性,長期信頼性が向上する。

(もっと読む)

半導体装置及びその製造方法

【課題】はみ出した接合材の量が多くてもフレームのボンディング部に接合材が到達するのを防ぐことができる半導体装置を得る。

【解決手段】フレーム10は、接合部10aとボンディング部10bを有する。半導体チップ12は、フレーム10の接合部10aに接合材20により接合されている。フレーム10のボンディング部10bと半導体チップ12は金線14により接続されている。そして、ボンディング部10bは接合部10aよりも突出している。

(もっと読む)

ウインドウ型半導体パッケージ

【課題】一種のモールド流入口に剥離現象の発生を避けるウインドウ型半導体パッケージを提供する。

【解決手段】半導体パッケージは、主に1つの基板、基板に貼り付ける一主面を有する1つのチップ、チップと基板の基板コア層とを接着する1つのダイアタッチング層、複数のボンディングワイヤ及び1つのモールド封止体を含む。基板のスロットの一端にチップ寸法を超える1つのモールド流入口を形成し、二個、または、これより多いモールド流れ障害物は、基板コア層上に付着してダイアタッチング区域の一縁部とスロットの両側縁との交差部位に位置し、更に、モールド流入口の両側に僅かに突出するためモールド流れによる衝撃はダイアタッチング層に加える応力を抵抗してモールド流入口に剥離現象の発生を避けると共に、ダイアタッチング間隙を維持することも可能である。

(もっと読む)

半導体装置及びその製造方法

【課題】機能素子の可動部分を配置した空間の気密性の低下を抑制しつつ、小型化を実現できる半導体装置とその製造方法を提供する。

【解決手段】表面10aに凹部15が形成され、その凹部15内に配置された可動部分を有する機能素子100を備える変位検出用半導体チップ10と、変位検出用半導体チップ10の表面10a上で凹部15を囲んで環状に配置されたダイアタッチ材を含む結合部20と、可動部分の変位を検出した機能素子100が出力する検出信号を処理する処理回路300を有し、空洞を形成するように凹部15の上方を覆って結合部20上に配置された信号処理用半導体チップ30とを備え、結合部20によって凹部15が気密封止されている。

(もっと読む)

積層型半導体装置の製造方法

【課題】上段側半導体素子の一部が下段側半導体素子の外周より外側に突出する積層構造において、素子間隔が狭い積層構造を実現しつつ、上段側半導体素子の載置時や接着剤の硬化処理時におけるチップシフトを抑制する。

【解決手段】配線基板2上に搭載された第1の半導体素子5上に、低回転時粘度μ0.5rpm)が10〜150Pa・sの範囲であると共に、高回転時粘度μ5rpmに対する低回転時粘度μ0.5rpmの比で表されるチキソ比(μ0.5rpm/μ5rpm)が2以上の接着剤を介して、第1の半導体素子5の外周より外側に突出した部分を備える第2の半導体素子9を配置する。第2の半導体素子9の突出部分9aと配線基板2との間の中空部に接着剤を充填しつつ、第2の半導体素子9を第1の半導体素子5上に接着する。

(もっと読む)

半導体装置、半導体モジュール、及びこれらの製造方法

【課題】半導体素子の発熱を効率良く放熱することができると共に、半導体装置の発熱を抑制することができる半導体装置、半導体モジュール、及びこれらの製造方法を提供する。

【解決手段】第1の貫通孔14が形成された半導体素子11と、前記第1の貫通孔14に対応した位置に第2の貫通孔15が形成され、半導体素子11に接する放熱板13と、第1の貫通孔14及び第2の貫通孔15を貫通する突起部17が形成され、突起部17は、絶縁層18を介し、第1の貫通孔14及び第2の貫通孔15の順に嵌合される電極板12とを有する半導体装置10、及び第1の絶縁部材51と第2の絶縁部材52とを介して半導体装置10と接する第1の冷却器53と第2の冷却器54を有する半導体モジュール50、並びにこれらの製造方法。

(もっと読む)

半導体装置とその製造方法

【課題】半導体装置の小型化・薄型化を低コストに実現し、かつ信頼性を確保した半導体装置とその製造方法を提供する。

【解決手段】半導体素子1と、有機基板2と、有機基板2に設けた突起ダムテープ3と、半導体素子1と突起ダムテープ3の間に設けた凹部4と、半導体素子1と有機基板2を接着して固定するペースト5と、半導体素子1と有機基板2を電気的に接続する金属細線6と、半導体素子1と金属細線6の領域を囲って封止する封止絶縁材料7と、有機基板2の半導体素子1を搭載していない反対面に付設する金属端子8から構成される。

(もっと読む)

半導体装置およびその製造方法

【課題】 電子素子と基板との電気的な接続の信頼性が高く、歩留まりを向上させることができる半導体装置およびその製造方法を提供する。

【解決手段】 第1および第2電極15a,15bを備える半導体チップ11と、第1および第2電極15a,15bにそれぞれ個別に臨んで設けられる第1および第2接続部17a,17bを備えるサブストレート基板12と、ろう材から成り、第1および第2電極15a,15bおよびこの第1および第2電極15a,15bに臨む第1および第2接続部17a,17bとそれぞれ接続して、半導体チップ11をサブストレート基板12に固定する第1および第2接続固定部13a,13bと、電気絶縁性を有し、サブストレート基板12の表面部うち相互に隣接する第1および第2接続固定部13a,13bの間の部分から半導体チップ11に向かって立設し、第1および第2接続固定部13a,13bの間に設けられる14とを備える。

(もっと読む)

半導体チップの実装方法

【課題】セラミック基板上の厚膜導体の上に、シリコン半導体よりなる半導体チップをはんだダイボンドにより、接続するようにした半導体チップの実装方法において、はんだ濡れ性を確保しつつ、厚膜導体のはんだ食われを極力防止する。

【解決手段】厚膜導体11の表面に、当該表面側から、活性金属よりなり厚膜導体11が溶融したはんだ30に溶け出すのを防止する溶出防止膜11a、この溶出防止膜11aよりも溶融したはんだ30に溶け出しやすく当該溶融したはんだ30に犠牲的に溶け出す犠牲膜11b、厚膜導体11よりもはんだ30の濡れ性に優れ当該濡れ性を確保する濡れ性向上膜11cを順次、積層し、その後、はんだ30を介した半導体チップ20の搭載、および、はんだ30による接続を行う。

(もっと読む)

電子部品搭載方法及び電子部品基板搭載構造体

【課題】はんだ接続部においてはんだの良好な濡れ性を確保して放熱性の低下を防止して光素子等の電子部品の特性を向上させた電子部品搭載方法を提供する。

【解決手段】電子部品1が搭載される基板4の主面側の、前記電子部品が搭載される領域の少なくとも一部に第1の導体層5を形成する工程と、該第1の導体層の少なくとも一部にはんだ6を形成する工程と、前記基板の主面側における電子部品が搭載される領域内において、前記はんだ以外の第1の導体層上あるいは前記基板の主面上に、突起物7を形成する工程と、該突起物で前記電子部品を支えた状態で前記はんだを溶融させて前記電子部品を前記基板の主面側の第1の導体層に接続して搭載する工程とを有することを特徴とする。

(もっと読む)

物理量検出装置

【課題】超音波ボンディング時のワイヤーの接合不良およびセンサの破損を防ぐとともに、耐衝撃性に優れた物理量検出装置を提供する。

【解決手段】物理量検出装置20は基板7上に搭載されたセンサ部19を備える。センサ部19は、錘部1が一対の梁部2を介して枠部3と接合し、枠部3の開口部に懸架される。また下蓋4が枠部3の下部と接合する。枠部3の上部にはパッド電極5が設けられ、基板7上に設けられた基板電極8と接続ワイヤー6を介して電気的に接続する。さらにセンサ部19は、支持部材9により下蓋4の下側から基板7上で支持される。支持部材9はセンサ部19または基板7のいずれか一方に固着された状態で、センサ部19を基板7上で支持する。支持部材9に支持されたセンサ部19は、弾性接着剤10により基板7に対して固着されている。支持部材9は弾性接着剤10より硬度の高い部材により構成される。

(もっと読む)

1 - 20 / 38

[ Back to top ]