Fターム[5F047BB05]の内容

Fターム[5F047BB05]に分類される特許

1 - 20 / 57

半導体用接着シート

【課題】先に剥離すべき剥離フィルムに接着剤層が転着したり、接着剤層の端部がめくれ上がったりする問題がなく、歩留りの向上やタクトタイムの短縮に貢献する半導体用接着シートを提供する。

【解決手段】硬化性組成物からなる接着剤層(3)の両面に、剥離フィルムA(1)、B(2)が剥離可能に貼着されてなる半導体素子を該取付部に接着するための半導体用接着シートであって、

剥離フィルムの曲げ剛性相対値(N・m=弾性率E(MPa)×(フィルム厚)3(mm3))が剥離フィルムA(1)のほうが剥離フィルムB(2)より大きく、

剥離フィルムB(2)の曲げ剛性相対値が0.2以上であり、

剥離フィルムA(1)の曲げ剛性相対値−剥離フィルムBの曲げ剛性相対値が0.5以上

である半導体用接着シート。

(もっと読む)

半導体装置の製造方法、半導体装置及び電子部品

【課題】厚さが15〜75μmの薄い半導体チップをピックアップする場合であっても、割れ、欠け等の破損を生じることなく、従来のコレットを用いてチップを速やかにピックアップすることができる、半導体装置の製造方法を提供すること。

【解決手段】半導体ウエハの一方の面に樹脂膜を形成する工程と、半導体ウエハの他方の面に、ダイボンディングフィルムを備える粘着シートを貼り合せてダイシングを行ない、ダイボンディングフィルム付き半導体チップを作製する工程と、コレットを用いてダイボンディングフィルム付き半導体チップをピックアップする工程と、ダイボンディングフィルム付き半導体チップを配線基板上にダイボンディングする工程と、を含み、半導体ウエハは、厚みが15〜75μmであり、樹脂膜は、25℃における弾性率が2〜10GPaであり、膜厚が3〜20μmである、半導体装置の製造方法。

(もっと読む)

フォームはんだ

【課題】従来のフォームはんだ製造方法は、所定量の金属粒を直接溶融はんだ中に投入してから金属粒を分散させるため、フォームはんだ中にフラックスが微量残っていた。そのため従来のフォームはんだ製造方法で得られたフォームはんだではんだ付けを行うとボイドが発生したり、部品が傾斜したりして充分な接合強度が得られなかった。

【解決手段】本発明では、熱分解可能なフラックスと高融点金属粒からなる混合物で混合母合金を作製し、さらに混合母合金を大量の溶融はんだに投入・攪拌してビレットを作製する。そして該ビレットを押出、圧延、打ち抜き工程を経てペレットやワッシャーにする。

(もっと読む)

ダイシング・ダイボンドフィルム

【課題】リフロークラックの発生を防止し信頼性に優れた半導体装置を生産性良く製造することを可能にするダイシング・ダイボンドフィルムを提供する。

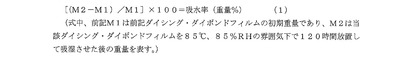

【解決手段】ダイシング・ダイボンドフィルムは、支持基材上に粘着剤層が設けられたダイシングフィルムと、前記粘着剤層上に設けられたダイボンドフィルムとを少なくとも有するダイシング・ダイボンドフィルムであって、下記式(1)により算出される吸水率が1.5重量%以下であることを特徴とする。 (もっと読む)

(もっと読む)

電子装置の製造方法及び電子装置

【課題】絶縁性を確保しつつ、はんだの厚さを制御可能な電子装置の製造方法及び電子装置を提供する。

【解決手段】金属板9上にはんだ5,11を介して基板7を配置し、基板上にはんだ5を介して電子部品3,7を配置しはんだ5、11をリフロー加熱してはんだ付けする電子装置1の製造方法において、はんだ5,11の外周部に、絶縁性樹脂からなり、リフロー加熱時に溶融してはんだと密接するスペーサ21,22を配置し、リフロー加熱後に電子部品3,基板7を封止樹脂15で樹脂封止する。

(もっと読む)

半導体装置の製造方法及び半導体装置

【課題】半導体素子と基板との接合強度のばらつきを抑制し、得られる製品の歩留まりを向上させる。

【解決手段】半導体素子1と、少なくとも表面の主元素をCuとする基板2と、前記半導体素子より小さな形状のZnAl共晶はんだチップ3’と、をそれぞれ準備する工程と、前記半導体素子と前記基板とをそれぞれの接合面が対向するように配置して、これら基板と半導体素子との間に前記ZnAl共晶はんだチップを挟む工程と、前記基板と前記半導体素子との間に挟んだ前記ZnAl共晶はんだチップに荷重31をかけながら昇温して、前記ZnAl共晶はんだチップを融解させてZnAlはんだ層3を形成する工程と、前記ZnAlはんだ層に荷重をかけながら降温する工程と、を備える。

(もっと読む)

接着シート

【課題】高接着性と低弾性を両立し得る接着シート及びそれを用いた半導体装置を提供する。

【解決手段】高分子量成分(A)及び熱硬化性成分(B)を含有する接着シートであって、上記熱硬化性成分(B)が特定の構造を有するフェノール樹脂及びフェノール誘導体の少なくとも一種であるフェノール類を含む接着シート。

(もっと読む)

半導体チップ用フィルム状接着剤、半導体加工用接着シートおよび半導体装置の製造方法

【課題】半導体ウエハや半導体チップなどの被着体に貼着された後、エキスパンド工程により、容易にチップサイズに分割できる半導体チップ用フィルム状接着剤あるいは接着剤層を有する半導体加工用接着シートを提供する。

【解決手段】半導体チップ用フィルム状接着剤1は、孔30が形成されている。また、半導体加工用接着シートは、孔30が形成された半導体チップ用フィルム状接着剤1を接着剤層とし、該接着剤層が剥離可能に基材に積層されている。

(もっと読む)

半導体装置の製造方法

【課題】接着面にボイドを生じさせずにダイボンディングできる技術を提供する。

【解決手段】吸着コレット105の底面に設けられた吸着口につながり、チップ1Cを真空吸着するための減圧力を吸着コレット105に供給する真空供給ラインを2つの系統から形成する。すなわち、チップ1Cをダイシングテープから剥離し、配線基板上の実装位置まで移送する際の吸着力となる真空を吸着コレット105に供給する配管121と、チップ1Cを配線基板上に実装する際の吸着力となる真空を吸着コレット105に供給する配管122とが吸着コレット105に接続する構造とする。吸着コレット105に供給する真空(吸着力)の強度の制御は、配管121、122のそれぞれに取り付けられたバルブ123、124の開閉によって行う。

(もっと読む)

半導体装置の製造方法とその方法で製造された半導体装置

【課題】本発明は、スクラブ動作を用いて部品を所定位置にずれなく固定できる半導体装置の製造方法と半導体装置を提供することを目的とする。

【解決手段】本願の発明に係る半導体装置の製造方法は、平板状の第1部品を吸着コレットに吸着させる工程と、平板状の第2部品の上面に接着金属を配置する工程と、該第1部品を吸着した状態で該吸着コレットを移動させ、該接着金属に該第1部品をのせる工程と、該第1部品と該吸着コレットが接した状態で、該第1部品と該第2部品の間の距離が増減する方向にのみ該吸着コレットをスクラブ動作させ、該接着金属を介して該第1部品を該第2部品に固定する固定工程と、を備えたことを特徴とする。

(もっと読む)

半導体装置の組立治具および半導体装置の組立方法

【課題】実装基板に半導体チップを半田付けする際に、組立治具と実装基板面の隙間寸法が半導体チップの厚みと半田の厚みを合わせた寸法以下にできる半導体装置の組立治具および半導体装置の組立方法を提供することである。

【解決手段】半田が溶融する温度で実装基板21が凹状に湾曲した場合でもチップコマ1の底面2aの一部が実装基板面22に常に自重で接触させることで、組立治具100と実装基板21の間の隙間寸法T1を半導体チップ31の厚さW1と溶融半田32aの厚さW2aを合わせた寸法T2以下にできる。その結果、半田溶融時に半導体チップ31が横方向にズレしてチップコマ1の開口部5からはみ出ることがなく、半導体チップ31の実装基板21への位置決めを精度よく行なうことができる。

(もっと読む)

電子部品の実装方法、および電子部品の実装構造

【課題】回路基板のダイパッドに対して、電子部品を隙間なく確実に、かつ容易に実装することが可能な電子部品の実装方法、および電子部品の実装構造を提供する。

【解決手段】半導体チップ21の接合面21aの一部分だけがハンダチップ13と接するように、ダイパッド11の一面11aに対して、半導体チップ21の接合面21aを傾斜させるように、半導体チップ21をダイパッド11に載置する(電子部品載置工程)。これによって、半導体チップ21は、例えば、四隅のうちのいずれかの角部分がハンダチップ13に乗り上げるように傾斜する。同時に、半導体チップ21は、ハンダチップ13に接している部分以外の一端(端部)が、ダイパッド11の一面11aに接するように傾斜する。

(もっと読む)

電気回路の製造装置及び製造方法並びに電気回路製造用治具

【課題】基材に半導体素子などの電気部品を半田付けする半田層中にボイドが発生することを抑制できる電気回路の製造装置及び製造方法並びに電気回路製造用治具を提供する。

【解決手段】基材(11)と電気部品(13)との間に配置される半田材(121)を一時的に溶融させることで電気部品(13)を基材(11)に半田付けする電気回路製造装置であって、電気部品(13)及び半田材(121)に重ねられたときに、電気部品(13)及び半田材(121)の側方に延びるように形成されて電気部品(13)及び半田材(121)との相対的な位置を定める位置決め部(112)と、電気部品側に凸設されて電気部品(13)の表面に当接する突起部(113)と、を有する治具(110)と、少なくとも治具(110)を加熱して治具(110)から伝導する熱によって半田材(121)を一時的に溶融させるヒーター(120)と、を備える。

(もっと読む)

ダイボンディング用ペレットと電子部品

【課題】電子部品の半導体素子と基板をダイボンディング接合するときに、従来の鉛フリーはんだのペレットを用いると、接合面に大量のボイドが発生し、放熱効果を悪くするばかりでなく、接合強度を弱くしていた。本発明は、鉛フリーはんだのペレットであるにもかかわらず、ボイドの発生が少ないペレットである。

【解決手段】Sn主成分の鉛フリーはんだ合金の表面に無色透明のSn-30〜50at%O−5〜15at%PやSn-10〜30at%In-40〜60at%O−5〜15at%Pからなる保護膜をはんだ付け加熱時に形成するペレットであり、厚さが0.05〜1mmである。

(もっと読む)

接合材料およびその製造方法、半導体装置およびその製造方法

【課題】接合信頼性を向上させた接合材料およびその接合材料を用いた半導体装置とそれらの製造方法を提供する。

【解決手段】半導体素子と、フレームあるいは基板との接合材料として、Al系層101がX系層102(X=Ge、Mg、In、Sn、Ag、Au、Ga)によって挟持され、さらにX系層102の外側がZn系層103によって挟持されたクラッド材を接合材料として用いる。このようなクラッド材を用いて接合することによって、材料の融点を下げ、半導体素子の割れを防ぐとともに、接合部のボイド率を10wt.%以下に抑えることが出来る。また、半導体素子とフレームあるいは基板との濡れ性も確保できる。したがって、接合部の高い信頼性を確保することが出来る。

(もっと読む)

回路基板の製造方法及び回路基板

【課題】耐久信頼性及び熱特性を一定以上に確保することが可能な回路基板の製造方法を提供すること。

【解決手段】導電層を有する絶縁基板と回路素子とを備え、前記絶縁基板の前記導電層と前記回路素子とがはんだにより接合される回路基板の製造方法であって、前記はんだで構成されるはんだシートに、前記絶縁基板の前記導電層と前記回路素子との間隔を規制する規制部材を配設する配設工程(ステップST1)と、前記絶縁基板、前記規制部材が配設された前記はんだシート、及び前記回路素子を、その順番で積層する積層工程(ステップST2)と、積層されている前記絶縁基板、前記はんだシート及び前記回路素子を、還元雰囲気下において加熱して前記はんだシートを溶融することによって、前記絶縁基板と前記回路素子とを接合する接合工程(ステップST3)と、を含む回路基板の製造方法である。

(もっと読む)

フリップチップ型半導体裏面用フィルム

【課題】被着体上にフリップチップ接続された半導体素子に反りが発生するのを抑制又は防止することが可能なフリップチップ型半導体裏面用フィルム、及びダイシングテープ一体型半導体裏面用フィルムを提供する。

【解決手段】フリップチップ型半導体裏面用フィルム2は、被着体上にフリップチップ接続された半導体素子の裏面を保護するためのフリップチップ型半導体裏面用フィルム2であって、少なくとも熱硬化性樹脂成分により形成され、かつ、熱可塑性樹脂成分を含まない層を少なくとも備えることを特徴とする。

(もっと読む)

ダイボンド装置及びダインボンディング方法

【課題】 接着剤塗布作業工程のタクトタイムを抑制し、ダイボンド時間を短縮するダイボンド装置を得ることを目的とする。

【解決手段】 ディスペンス1により実装される半導体部品6の部品サイズや形状に合わせた塗布形状を接着剤供給ステージ3に形成し、部品トレイ5上の半導体部品を部品吸着ヘッドで吸着し、接着剤供給ステージ3上に塗布された接着剤2の位置まで移動後、下降して半導体部品6裏面に接着剤2を転写する。その後、基板7のダイアタッチ部に、半導体部品6をダイボンドして部品実装を行う。

(もっと読む)

熱硬化型ダイボンドフィルム、ダイシング・ダイボンドフィルム、及び、半導体装置

【課題】熱硬化させた際に被着体に反りが発生することを抑制することが可能な熱硬化型ダイボンドフィルムを提供する。

【解決手段】半導体チップの被着体への固着に用いる熱硬化型ダイボンドフィルム3であって、120℃、1時間の条件で熱硬化させた後の25〜120℃の範囲での引張貯蔵弾性率の積分値が、1GPa〜50GPaである熱硬化型ダイボンドフィルム3。前記熱硬化型ダイボンドフィルム3は熱硬化樹脂としてのエポキシ樹脂及び/又はフェノール樹脂を含有するとともに、熱可塑性樹脂としてのアクリル樹脂を含有する。

(もっと読む)

半導体装置および車載用交流発電機

【課題】

環境負荷が小さく低コストで、200℃以上の高温で長時間使用しても接続信頼性を維持できる半導体素子の接続材料を提供することが課題である。

【解決手段】

半導体素子と、半導体素子の第一の面と第一の接続部材を介して接続された支持電極体と、

前記支持電極体に支持された前記半導体素子の第二の面と第二の接続部材を介して接続されたリード電極体と、を有する半導体装置であって、前記支持電極体と前記第一の接続部材の界面には、Ni系めっき層、および、Cu6Sn5化合物と(Cu、Ni)6Sn5化合物の少なくとも1つを含む金属間化合物層を有し、前記リード電極体と前記第二の接続部材の界面には、Ni系めっき層、および、Cu6Sn5化合物と(Cu、Ni)6Sn5化合物の少なくとも1つを含む金属間化合物層を有することを特徴とする半導体装置である。

(もっと読む)

1 - 20 / 57

[ Back to top ]