Fターム[5F048BA00]の内容

MOSIC、バイポーラ・MOSIC (97,815) | 基板 (9,458)

Fターム[5F048BA00]の下位に属するFターム

単層基板 (3,772)

多層基板(2層) (997)

基板中に絶縁層 (137)

結晶面・結晶軸 (355)

基板中にキャリア再結合中心を添加したもの (8)

埋め込み層 (425)

素子形成領域、能動領域がSi以外の材料 (1,343)

絶縁性基板 (1,909)

複数MOSの素子電極が同一平面でないもの (501)

Fターム[5F048BA00]に分類される特許

1 - 11 / 11

半導体装置

【課題】バルク半導体基板上に形成されるトンネルトランジスタ同士を電気的に分離することが可能な半導体装置を提供する。

【解決手段】実施形態によれば、半導体装置は、半導体基板と、前記半導体基板内に形成された第1および第2の素子分離絶縁膜とを備える。さらに、前記装置は、前記第1および第2の素子分離絶縁膜間の前記半導体基板上に、ゲート絶縁膜を介して形成されたゲート電極を備える。さらに、前記装置は、前記半導体基板内に前記ゲート電極を挟むように形成された、第1導電型の第1の主端子領域および前記第1導電型とは逆導電型の第2導電型の第2の主端子領域を備える。さらに、前記装置は、前記半導体基板内に前記第1および第2の素子分離絶縁膜に接するように形成され、前記第1および第2の主端子領域の下面よりも深い位置に上面を有する、前記第2導電型の第1の拡散層を備える。

(もっと読む)

半導体装置、半導体装置の製造方法、電子機器および電子機器の製造方法

【課題】回路特性の向上が可能な、有機トランジスタよりなる論理回路を有する半導体装置を提供する。

【解決手段】本発明に係る半導体装置は、ドライバトランジスタ(PTD)とロードトランジスタ(PTL)を有する論理回路を含む半導体装置であって、ドライバトランジスタの能動層は、第1のp型有機半導体層(5D)からなり、ロードトランジスタの能動層は、第2のp型有機半導体層(5L)からなり、ロードトランジスタの閾値電圧(VthL)はドライバトランジスタの閾値電圧(VthD)よりも高い。p型有機半導体(5D,5L)の膜厚を変えることにより、閾値を変化させる。p型有機半導体(5D,5L)の材料を変えることにより、閾値を変化させる。第1のp型有機半導体層(5D)にドナーを含ませる。第2のp型有機半導体層(5L)にアクセプターを含ませる。かかる構成により、論理回路の特性を向上させることができる。

(もっと読む)

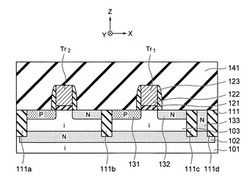

半導体装置及び電子機器

【課題】回路面積が小さい、またはトランジスタの劣化を防止するよう形成された、有機トランジスタと無機トランジスタとを備えた半導体装置を提供する。

【解決手段】本発明の一形態の半導体装置としてのCMOS回路は、(a)基板100と、(b)有機半導体層106aを含むp型有機トランジスタPTと、(c)p型有機トランジスタPTの上層に設けられた無機半導体層126aを含むn型無機トランジスタNTと、を備える。さらに、n型無機トランジスタNTのチャネル領域126は、p型有機トランジスタPTのチャネル領域106と、平面視において少なくとも部分的に重なっている。

(もっと読む)

半導体装置及びその製造方法

【課題】ホール移動度を向上し、ジャンクションリークを低減する。

【解決手段】DSB(Direct Silicon Bonded)基板は、第1の基板および第2の基板を含み得る。ここで、第2の基板は、第1の基板に比べて、45度の結晶方位ねじれ角に回転され得る。閾値電圧(Vt)に基づいて調整された厚さを備えるDSB基板を含む半導体装置および半導体装置の製造方法が開示されている。言い換えると、より厚い基板または層が高閾値電圧(HVt)に対応し、より薄い基板または層が低閾値電圧(LVt)に対応し得る。この薄膜化により、LVt装置において、さらに移動度が向上する。

(もっと読む)

半導体装置

【課題】dv/dtサージにより、支持基板と活性層との間の絶縁膜にて構成される寄生容量を充放電する変位電流が発生することを抑制し、回路の誤動作を防止する。

【解決手段】低電位基準回路部LVの下と高電位基準回路部HVの下にのみ支持基板2を残す。これにより、支持基板2のうち低電位基準回路部LVの下の部分と高電位基準回路部HVの下の部分とが絶縁部材30にて絶縁された状態となる。さらに、高電位基準回路部HVと支持基板2との間および低電位基準回路部LVと支持基板2との間の双方、もしくは、少なくとも高電位基準回路部HVと支持基板2との間を同電位にする。

(もっと読む)

半導体装置の製造方法

【課題】チャネル領域のゲート幅方向に与える応力を移動度が向上する方向に働かすとともに、ソース・ドレイン領域表面にシリサイド層を形成した際のリークを防止する。

【解決手段】半導体基板11に素子形成領域12を挟み、半導体基板11に埋め込まれるように素子分離領域13を形成する工程と、素子形成領域12上にそれを横切るようにダミーゲート52を形成する工程と、ダミーゲート52の両側の素子形成領域12にソース・ドレイン領域の接合位置が素子分離領域13の表面より深い位置にしてソース・ドレイン領域27、28を形成する工程と、半導体基板11上にダミーゲート52の表面を露出させて第1層間絶縁膜42を形成する工程と、ダミーゲート52を除去して溝29を形成する工程と、溝29内の素子分離領域13の上部を除去する工程と、溝29内の半導体基板11上にゲート絶縁膜21を介してゲート電極22を形成する工程とを備えている。

(もっと読む)

半導体装置およびその製造方法

【課題】酸化シリコン膜のエッチングに対するエッチング耐性を有する応力膜を形成することで、応力膜の上記エッチング時の膜減りを低減することを可能にする。

【解決手段】半導体基板11上にゲート電極形成溝23が形成されたサイドウォール絶縁膜21と、ゲート電極形成溝23内の半導体基板11上にゲート絶縁膜24を介して形成されたゲート電極25と、ゲート電極25の側壁にサイドウォール絶縁膜24を介して半導体基板11上に形成されていて応力を有する第1応力膜51と、第1応力膜51の外側の半導体基板11上に形成されていて第1応力膜51と同種の応力を有する第2応力膜52とを有し、第1応力膜51および第2応力膜52は酸化シリコン膜をエッチングするときのエッチング種に対するエッチング耐性を有し、第1応力膜51は第2応力膜52よりも前記エッチング種に対するエッチング耐性が強いことを特徴とする。

(もっと読む)

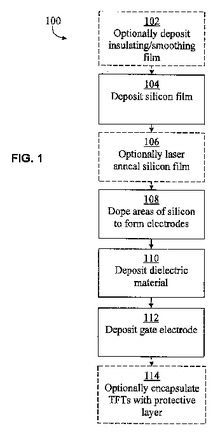

シリコン薄膜トランジスタ、並びにその製造システム及び方法

可撓性基板上に、自己整合シリコン薄膜トランジスタを製造するシステム及び方法。前記システム及び方法は、高いパフォーマンスのトランジスタを製造するために、精密さ、レゾリューション、レジストレーションが達成されるよう、レーザアニール、エッチング技術、レーザドーピングを全て低温度で行いつつ、化学気相堆積、プラズマエンハンスト気相堆積、プリント、コーティング、及び他の堆積処理といった堆積処理を組み込むとともに組み合わせている。そのようなTFTはディスプレイ、パッケージング、ラベリング等に使用できる。  (もっと読む)

(もっと読む)

高周波スイッチ

【課題】非導通MOSFETを介した高周波信号の接地への漏れを抑制し、信号伝送損失が低減された高周波スイッチを提供する。

【解決手段】第1の端子と第2の端子との間に、第1のゲート電圧の変化により同時に導通または非導通とされ、直列接続された第1及び第2のスルーのMOSFETと、前記第1の端子と第3の端子との間に、第2のゲート電圧の変化により同時に非導通または導通とされ、直列接続された第3及び第4のスルーMOSFETと、を備え、直列接続されたスルーのMOSFETのバックゲートは、2つのスルーのMOSFETの間の点と接続され、前記第1の端子は、前記第2の端子及び前記第3の端子のいずれかに相補的に接続されることを特徴とする高周波スイッチが提供される。

(もっと読む)

半導体装置

【課題】半導体装置において半導体素子間の分離を好適に達成するとともに半導体装置の小型化を図ること。

【解決手段】半導体基板1と、半導体基板1上に形成されたエピタキシャル層2と、半導体基板1とエピタキシャル層2との間に形成された埋め込み層3と、エピタキシャル層2表面から埋め込み層3に達する第1のトレンチ7と、第1のトレンチ7内に埋め込まれるとともに埋め込み層3と接続されたドレイン取出電極8bと、ドレイン取出電極8bを電極とした半導体素子と、エピタキシャル層2表面からその半導体素子を囲むように設けられた第2のトレンチ5とを備え、第2のトレンチ5内の少なくとも側壁を絶縁膜6aで被覆した。

(もっと読む)

半導体装置

【課題】電子又はホールの移動度を向上でき、接合リーク電流の発生を抑制できる半導体装置を提供する。

【解決手段】半導体装置は、第1半導体層16と、前記第1半導体層の主表面領域中に設けられた第1導電型の第1絶縁ゲート型電界効果トランジスタP1と、前記第1半導体層の裏面に設けられ、前記第1絶縁ゲート型電界効果トランジスタの動作時に、前記第1絶縁ゲート型電界効果トランジスタのチャネル領域に、チャネル長方向に沿った第1の応力を加える電歪層16Pとを具備する。

(もっと読む)

1 - 11 / 11

[ Back to top ]