Fターム[5F048BA02]の内容

MOSIC、バイポーラ・MOSIC (97,815) | 基板 (9,458) | 多層基板(2層) (997)

Fターム[5F048BA02]の下位に属するFターム

3層以上 (202)

基板と直上の層が同型 (184)

基板と直上の層が異型 (194)

Fターム[5F048BA02]に分類される特許

1 - 20 / 417

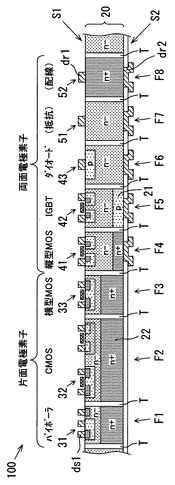

半導体装置の製造方法

【課題】能動素子または受動素子が一つの半導体基板に複数個形成されてなる半導体装置およびその製造方法であって、両面電極素子についても絶縁分離と集積化が可能であり、安価に製造することのできる半導体装置およびその製造方法を提供する。

【解決手段】半導体基板20が、当該半導体基板20を貫通する絶縁分離トレンチTに取り囲まれて、複数のフィールド領域F1〜F8に分割されてなり、複数個の能動素子31〜33,41〜43または受動素子51,52が、それぞれ異なるフィールド領域F1〜F8に分散して配置されてなり、二個以上の素子が、当該素子に通電するための一組の電極dr1,dr2が半導体基板20の両側の表面S1,S2に分散して配置されてなる、両面電極素子41〜43,51,52である半導体装置100とする。

(もっと読む)

炭化珪素半導体装置

【課題】 少ない工程数で形成でき、耐熱性に優れた温度センサを備える炭化珪素半導体装置を得る。

【解決手段】 炭化珪素基板1の活性領域ARに形成された半導体素子と、活性領域ARを取り囲むように炭化珪素基板1中に形成されたウエル領域5と、炭化珪素基板1上に配設される多結晶シリコンからなるゲート電極8と、ゲート電極8と同時に形成され、その一部を用いて形成した測温抵抗体17と、を備えることを特徴とする。

(もっと読む)

半導体デバイス

【課題】高い電流増幅率と高いアーリー電圧を両立することができ、CMOSトランジスタとともに製造する場合でもより少ない製造工程により製造することができる半導体デバイスを提供する。

【解決手段】基板P11の表面に形成された第1導電型のベースP14と、ベースの表面に形成された第2導電型のエミッタN23と、ベースの表面においてエミッタと離間して配置され、エミッタから第1の種類のキャリアを受け取るとともに、その第1の種類のキャリアをベースへ注入する、第2導電型のドープ領域N24と、ベースを挟んで、エミッタおよびドープ領域の反対側に形成された、第2導電型のコレクタN15とを備える。

(もっと読む)

半導体装置

【課題】本発明は、半導体装置に負電流が流れた場合でも、回路素子を構成する深い半導体層の電位に対して、半導体基板の電位が低くなるのを抑制して寄生素子を作動させず、半導体装置の誤動作を防止する。

【解決手段】本発明は、n型の半導体基板3と、半導体基板3の一面に形成し、接続する負荷に電力を供給する電力素子1と、n型のソース・ドレイン領域を有するMOSトランジスタ2cを少なくとも1つ含む回路素子2と、電力素子1および回路素子2に対し独立して配置したp型の半導体層4と、半導体基板3および半導体層4と接続する外部回路とを備えている。外部回路は、電源と、電源に一端を接続する抵抗素子と、抵抗素子の他端にアノード電極を接続し、カソード電極をGND接地するダイオードとを有し、抵抗素子の他端に半導体層4を接続する。

(もっと読む)

半導体装置及びその製造方法

【課題】バーティカル型のバイポーラトランジスタにおいて、エミッタ領域からベース領域にかけて存在する界面準位を安定に低減することを可能とした半導体装置とその製造方法を提供する。

【解決手段】バーティカル型のバイポーラトランジスタ10は、シリコン基板1に形成されたP型のベース領域13と、シリコン基板1に形成されてベース領域13に接するエミッタ領域15と、シリコン基板1の表面であってベース領域13とエミッタ領域15との境界部21上に形成されたシリコン酸化膜17と、シリコン酸化膜17上に形成されたポリシリコンパターン19と、を有する。シリコン酸化膜17とシリコン基板1との界面に塩素が1×1017cm−3以上の濃度で存在する。

(もっと読む)

半導体装置の製造方法

【課題】高いスループットで製造するために有利な製造方法を提供する。

【解決手段】第1領域101および第2領域102を有する半導体基板において、第1絶縁膜112、第2絶縁膜113および第3絶縁膜122を貫通する第1コンタクトホール形成工程と、第4絶縁膜120、第5絶縁膜121および第6絶縁膜122を貫通する第2コンタクトホール形成工程とを含み、前記第1,3,4,6絶縁膜は第1組成を有し、前記第2,4絶縁膜は前記第1組成とは異なる第2組成を有し、開口工程では、前記第2絶縁膜をエッチングストッパとして前記第3絶縁膜をエッチング後に、前記第2絶縁膜および前記第1絶縁膜を互いに異なるエッチング条件で第1コンタクトホールを形成し、前記第5絶縁膜をエッチングストッパとして前記第6絶縁膜をエッチング後に、前記第5,4絶縁膜を同一のエッチング条件で連続的にエッチングして、前記第2コンタクトホールを形成する。

(もっと読む)

窒化ガリウム結晶、ホモエピタキシャル窒化ガリウムを基材とするデバイス、及びその製造方法

【課題】ホモエピタキシャルLED、LD、光検出器又は電子デバイスを形成するために役立つGaN基板の形成方法の提供。

【解決手段】約104/cm2未満の転位密度を有し、傾角粒界が実質的に存在せず、酸素不純物レベルが1019cm−3未満の窒化ガリウムからなる単結晶基板上に配設された1以上のエピタキシャル半導体層を含むデバイス。かかる電子デバイスは、発光ダイオード(LED)及びレーザーダイオード(LD)用途のような照明用途、並びにGaNを基材とするトランジスター、整流器、サイリスター及びカスコードスイッチなどのデバイスの形態を有し得る。また、約104/cm2未満の転位密度を有し、傾角粒界が実質的に存在せず、酸素不純物レベルが1019cm−3未満の窒化ガリウムからなる単結晶基板を形成し、該基板上に1以上の半導体層をホモエピタキシャルに形成する方法及び電子デバイス。

(もっと読む)

半導体装置

【課題】横型DMOSの素子面積の増大を抑制し高耐圧化をはかる。

【解決手段】第1の半導体素子100Aは、第1半導体層12Aと、第2半導体層14Aと、第2半導体層に隣接する第3半導体層16Aと、第1絶縁層20Aと、第2半導体層の表面に選択的に設けられた第1ベース領域30Aと、第1ベース領域の表面に選択的に設けられた第1ソース領域32Aと、第1絶縁層の内部に設けられた第1ゲート電極40Aと、第1ベース領域の下に設けられ、第1半導体層の表面から第1ベース領域の側に延在する第1ドリフト層18Aと、第1ソース領域32Aに対向し、第1絶縁層20Aを挟んで第3半導体層16Aの表面に設けられた第1ドレイン領域34Aを有す。第1ドリフト層18Aの不純物元素の濃度は、第1半導体層12Aの不純物元素の濃度よりも低い。第1ドリフト層の不純物元素の濃度は、第2半導体層14Aの不純物元素の濃度よりも高い。

(もっと読む)

半導体装置およびその製造方法

【課題】不純物イオンの注入による悪影響を防止しつつ水平方向の耐圧を向上できる半導体装置およびその製造方法を提供する。

【解決手段】半導体装置は、素子を構成し、電流が流れる一対の不純物領域が、半導体基板の第1主面の表層に形成されたものであり、水平方向の耐圧を確保するため、フィールドプレート33を有している。これに加えて、この半導体装置は、半導体基板の表面から、素子の電流経路となる第1不純物領域37および第2不純物領域38よりも深い所定の深さおいて、少なくとも第1不純物領域および第2不純物領域の間の領域に半導体基板と同一成分の非晶質層24を有する。この非晶質層は、単結晶および多結晶よりも高抵抗の層であり、擬似的なフィールドプレートとして機能する。そして、この非晶質層は、不活性元素のイオン注入により形成される。

(もっと読む)

ダイオード、半導体装置およびMOSFET

【課題】 ダイオードにおけるスイッチング時の損失を低減することが可能な技術を開示する。

【解決手段】 本明細書で開示するダイオードは、カソード電極と、第1導電型の半導体からなるカソード領域と、低濃度の第1導電型の半導体からなるドリフト領域と、第2導電型の半導体からなるアノード領域と、金属からなるアノード電極を備えている。そのダイオードは、前記ドリフト領域と前記アノード領域の間に形成された、前記ドリフト領域よりも濃度が高い第1導電型の半導体からなるバリア領域と、前記バリア領域と前記アノード電極を接続するように形成された、前記バリア領域よりも濃度が高い第1導電型の半導体からなるピラー領域を備えている。そのダイオードでは、前記ピラー領域と前記アノード電極がショットキー接合している。

(もっと読む)

半導体装置およびその製造方法

【課題】素子特性を悪化させず、アクティブ領域を終端領域に対して、簡単な方法により電気的に独立させることができ、さらには素子サイズの小型化を図ることができる半導体装置およびその製造方法を提供すること。

【解決手段】エピタキシャル層23のアクティブ領域12と終端領域11との間に、エピタキシャル層23の表面24を形成するように、当該表面24に沿って全体にわたって形成されたチャネル層26を、ゲートトレンチ28の深さD1と同じ深さD2を有するアイソレーショントレンチ39で分断する。互いに同じ深さのゲートトレンチ28およびアイソレーショントレンチ39は、同一のエッチング工程で形成される。

(もっと読む)

トレンチポリシリコンダイオード

【課題】シリコン内にダイオード構造を位置させた半導体製造方法を提供する。

【解決手段】トレンチポリシリコンダイオードを製造する方法は、N+(P+)型基板上にN−(P−)型エピタキシャル領域を形成すること、エピタキシャル領域内にトレンチを形成すること、さらに、前記トレンチ内に絶縁層を形成し、前記トレンチをポリシリコンで充填する。さらに、P+(N+)型ドーパントをインプラントして、前記トレンチ内に前記ポリシリコンのP+(N+)型領域を、N+(P+)型ドーパントをインプラントして、前記トレンチ内に前記ポリシリコンのN+(P+)型領域を形成しトレンチ内にポリシリコンダイオードを形成することを含み、ダイオードの一部は、トレンチの上面より低い。

(もっと読む)

半導体装置の製造方法、半導体装置

【課題】SiCが用いられる半導体層中において、簡易な工程で再現性よく埋め込み絶縁層を形成する。

【解決手段】単結晶のSiC12の表面の温度を局所的に急激に上昇させ、その後で急激に冷却することによって、単結晶を局所的に非晶質化層30を形成することができる。この非晶質層30は、元の単結晶SiCの導電型や抵抗率に関わらず、高抵抗層(絶縁層)となる。このため、こうした非晶質層を埋め込み絶縁層と同様に使用することができる。このためには、(1)レーザー光を効率的に吸収する層100を局所的に半導体層の上に形成してからレーザー光を照射する、(2)レーザー光を局所的に半導体層に照射する、という2つの手段のいずれかを用いることができる。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】縦型トランジスタの特性にばらつきが生じることを抑制する。

【解決手段】半導体基板100には縦型MOSトランジスタ20が形成されている。半導体基板100の表面上には、第1層間絶縁膜300及び第1ソース配線312が形成されている。第1ソース配線312は、第1層間絶縁膜300上に形成されており、平面視で縦型MOSトランジスタ20と重なっている。第1層間絶縁膜300にはコンタクト302が埋め込まれている。コンタクト302は、縦型MOSトランジスタ20のn型ソース層140と第1ソース配線312とを接続している。そして第1ソース配線312には、複数の開口316が形成されている。

(もっと読む)

半導体装置、半導体ウエハ、及びこれらの製造方法

【課題】トランジスタ特性のバラツキが低減された半導体装置を提供する。

【解決手段】SOI基板101は、P型半導体層102の上にN型半導体層104が形成された半導体基板12、その上に形成されたBOX層106、及びBOX層上に形成されたSOI層108を有する。第1素子分離絶縁層110bは、SOI基板101に埋め込まれ、下端16がP型半導体層102に達し、第1素子領域(NFET領域30)と第2素子領域(PFET領域40)とを分離する。P型トランジスタ130bは、第1素子領域40に位置し、チャネル領域120bを有し、N型トランジスタ130aは、NFET領域30に位置し、チャネル領域120aを有する。第1バックゲートコンタクト134bは、第1素子領域40に位置する第2導電型層層104に、第2バックゲートコンタクト134aは、第2素子領域30に位置する第2導電型層104に接続される。

(もっと読む)

半導体装置、半導体装置の製造方法、電子装置、及び車両

【課題】縦型バイポーラトランジスタのSOA(安全動作領域)が狭くなることを抑制する。

【解決手段】p型ベース層150は、厚さ方向の不純物プロファイルにおいて、第1のピーク、第2のピーク、及び第3のピークを有している。第1のピークは、最も半導体基板100の表面側に位置している。第2のピークは、第1のピークよりも半導体基板100の裏面側に位置しており、第1のピークよりも高い。第3のピークは、第1のピークと第2のピークの間に位置している。

(もっと読む)

半導体装置

【課題】耐圧の向上が図られる半導体装置を提供する。

【解決手段】n-型半導体領域には、ドレイン領域となるn-型の拡散領域が形成されている。n-型の拡散領域の周囲を取囲むようにp型の拡散領域が形成されている。p型の拡散領域には、ソース領域となるn+型の拡散領域が形成されている。n-型の拡散領域の直下には、p-型の埋め込み層13が形成されている。n-型の半導体領域の領域には、高電位が印加されるn+型の拡散領域が形成され、そのn+型の拡散領域の表面上には電極が形成されている。電極とドレイン電極とは、配線20によって電気的に接続されている。配線20の直下に位置する部分に、p-埋め込み層13に達するトレンチ3aが形成されて、ポリシリコン膜81が形成されている。

(もっと読む)

半導体装置及びその製造方法

【課題】 シリコンビームを使用しかつダブルゲートを有する半導体装置のおけるプロセスばらつきによる抵抗値ばらつきを防止する。

【解決手段】 端部に凹部を有する基板1と、基板1の凹部に一部が埋め込まれた一対のゲート電極4と、基板1の表面であって一対のゲート電極4の間に形成された拡散層7を有し、ゲート電極4と拡散層7の間の電位を変化させることにより、拡散層7の抵抗値を変化させる。

(もっと読む)

半導体装置及びその製造方法

【課題】BiCMOSプロセスにより製造される半導体装置において、V−NPNトランジスタの製造工程を合理化する。また、そのトランジスタのhFEを大きな値に調整する。

【解決手段】N+型エミッタ領域14Eの下のP型ベース領域7の底部に接触してN型ベース幅制御層9が形成されている。N型ベース幅制御層9が形成されることで、N+型エミッタ領域14Eの下のP型ベース領域7が局所的に浅くなっている。また、P型ベース領域7は、P型ウエル領域6の形成工程を用いて形成し、N型ベース幅制御層9は、N型ウエル領域8の形成工程を用いて形成することにより、工程合理化を図ることができる。

(もっと読む)

半導体装置及びその製造方法

【課題】互いに絶縁分離された複数の素子を有する半導体装置の小型化と、その製造コストの低減とを実現できるようにする。

【解決手段】半導体装置は、第1の素子151、第2の素子152、第3の素子153及び第4の素子154を備えている。基板100は、基板を貫通する第1素子分離領域131により互いに分離された第1の区画101及び第2の区画102を有している。第1の区画は、第2素子分離領域132により互いに分離された第1素子領域121及び第2素子領域122を含む。第2の区画は、第3素子分離領域133により互いに分離された第3素子領域123及び第4素子領域124を含み、基板の裏面に露出した裏面拡散層を有している。第3の素子は、第3素子領域に形成され、第4の素子は、第4素子領域に形成され、第3の素子及び第4の素子は、裏面拡散層105を介在させて互いに接続されている。

(もっと読む)

1 - 20 / 417

[ Back to top ]