Fターム[5F048BB13]の内容

MOSIC、バイポーラ・MOSIC (97,815) | ゲート (19,021) | 多層(2層)ゲート (2,461) | 3層以上 (480)

Fターム[5F048BB13]に分類される特許

201 - 220 / 480

半導体装置

【課題】動作特性の劣化を抑えつつ、それぞれ適切な閾値電圧を設定された、メタルゲート電極を用いたn型およびp型のMISFETを混載する半導体装置を提供する。

【解決手段】半導体基板上に第1のゲート絶縁膜を介して形成された、第1の金属層および前記第1の金属層上の第1の導電層を含む第1のゲート電極を含むn型トランジスタと、半導体基板上に第2のゲート絶縁膜を介して形成された、前記第1の金属層よりも厚さが厚く、前記第1の金属層と構成元素の同一な材料からなる第2の金属層、および前記第2の金属層上の第2の導電層を含む第2のゲート電極を含むp型トランジスタと、を有する。

(もっと読む)

半導体装置およびその製造方法

【課題】 本発明は、周辺回路部にLV系トランジスタ領域とHV系トランジスタ領域とを有するNAND型フラッシュメモリにおいて、LV系トランジスタでの結晶欠陥の発生を抑制しつつ、HV系トランジスタでの反転リークなどの増加を抑制できるようにする。

【解決手段】 たとえば、HV系トランジスタ領域102のSTI204の形成部にゲート絶縁膜加工を施すことにより、そのSTI204の底部に、HV系トランジスタ領域102のゲート下絶縁膜11とLV系トランジスタ領域103のゲート下絶縁膜21との膜厚差に応じた深さの第2領域204Xを形成する。この第2領域204Xの分だけ、LV系トランジスタ領域103のSTI304よりも、HV系トランジスタ領域102のSTI204での埋め込み素子分離用絶縁膜の膜厚(膜量)を増加させることが可能となる。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】ゲート絶縁膜に高誘電率膜を用いたMISトランジスタのトランジスタ特性を向上する。

【解決手段】基板の主面上に形成した酸化シリコン(SiO2)膜上に、ハフニウムおよび酸素を含むベース絶縁膜を形成する。次いで、ベース絶縁膜上に、ベース絶縁膜より薄く、かつ、金属元素のみからなる金属薄膜を形成し、その金属薄膜上に、耐湿性および耐酸化性を有する保護膜を形成する。その後、保護膜を有する状態で、ベース絶縁膜に金属薄膜の金属元素をすべて拡散することによって、酸化シリコン膜上に、酸化シリコン膜より厚く、かつ、酸化シリコンより誘電率が高く、ベース絶縁膜のハフニウムおよび酸素と、金属薄膜の金属元素とを含む混合膜(高誘電率膜)を形成する。

(もっと読む)

半導体装置およびその製造方法

【課題】不揮発性メモリを有する半導体装置の特性を向上させる。

【解決手段】電荷蓄積膜MI1に対して電荷を授受することで記憶動作を行う不揮発性メモリセルNVM1を有する半導体装置であって、不揮発性メモリセルNVM1は、シリコン基板1の主面s1に形成されたpウェルpw1と、主面s1上に電荷蓄積膜MI1を隔てて形成されたメモリゲート電極MG1とを有し、更に、シリコン基板1の主面s1のうち、電荷蓄積膜MI1下に位置するメモリチャネル領域ch1aにフッ素を含んでいる。

(もっと読む)

半導体装置及びその製造方法

【課題】互いに異なる金属膜厚からなるゲート電極を有するn型及びp型MISトランジスタを備えた半導体装置において、ゲートリークによる劣化を抑制する。

【解決手段】半導体装置は、第1のMISトランジスタと第2のMISトランジスタとを備える。第1のMISトランジスタは、第1の活性領域12a上に形成された第1のゲート絶縁膜13aと、第1のゲート絶縁膜13a上に形成された第1の金属膜14a、及び、第1の金属膜14a上に形成された第1のシリコン膜17aを含む第1のゲート電極24Aとを備える。第2のMISトランジスタは、第2の活性領域12b上に形成された第2のゲート絶縁膜13bと、第2のゲート絶縁膜上に形成された第1の金属膜14b、第1の金属膜14b上に形成された第2の金属膜15b、及び、第2の金属膜15bの上に形成された第2のシリコン膜17bを含む第2のゲート電極24Bとを備えている。

(もっと読む)

半導体装置及びその製造方法

【課題】微細化しても動作特性の劣化が生じないSTI構造の半導体装置及びその製造方法を得る。

【解決手段】NMOSトランジスタのゲート電極部をNMOS仕事関数制御メタル層7及びゲート主電極5により構成する。NMOS仕事関数制御メタル層7をスパッタ法により形成され、ディボット部2dが設けられるエッジ近傍領域である領域bにおける膜厚は、他の領域である領域aにおける膜厚より薄く形成される。したがって、NMOS仕事関数制御メタル層7に関し、領域bにおける実効仕事関数が領域aにおける実効仕事関数に比べ、ミッドギャップよりに設定される。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】従来に比べて製造工程を簡易化することができ、かつ、絶縁膜が損傷を受けることを防止することができ、製造コストの低減と信頼性の向上を図ることのできる半導体装置及び半導体装置の製造方法を提供する。

【解決手段】P型半導体層11上に、下側から順に第1ゲート絶縁膜2a、第2ゲート絶縁膜2b、第1金属膜3a、第2金属膜3b、第3金属膜3cが形成されたNチャンネルMISトランジスタ21、及び、N型半導体層10上に、下側から順に第1ゲート絶縁膜2a、第2ゲート絶縁膜2b、第1金属膜3a、第3金属膜3cが形成されたPチャンネルMISトランジスタ20を具備した半導体装置。

(もっと読む)

半導体装置、及びその製造方法

【課題】 金属層と半導体層との接続抵抗の上昇を抑えた積層ゲート電極を有する半導体装置、及びその製造方法を提供する。

【解決手段】 半導体装置10は、半導体基板11に形成された第1導電型のソース領域及びドレイン領域14と、ソース領域とドレイン領域との間に形成されたチャネル領域16と、チャネル領域上に形成されたゲート絶縁膜21とを有する。半導体装置10は更に、ゲート絶縁膜上に形成された金属ゲート電極層22と、金属ゲート電極層上に形成された、第1導電型とは逆の導電型である第2導電型の半導体ゲート電極層23とを有する。

(もっと読む)

半導体装置の製造方法及び半導体装置

【課題】ゲートラストプロセスの適用に際して、トランジスタのフリンジ容量及びゲート抵抗の低減と、実効的なゲート長の短縮を実現する。

【解決手段】本発明の半導体装置の製造方法は、半導体基板1上にゲート絶縁膜2、第1のダミーゲート部3及び第2のダミーゲート部4を順に積層して形成する工程と、それらをパターン加工するとともに、第1のダミーゲート部3をゲート長方向Xで第2のダミーゲート部4よりも後退させることにより、ノッチ部6を形成する工程と、ゲート絶縁膜2、第1のダミーゲート部3及び第2のダミーゲート部4の側方に絶縁材料からなる側壁7を形成し、かつ当該絶縁材料でノッチ部6を埋め込む工程と、第1,第2のダミーゲート部3,4を除去して、当該除去部分の底部にゲート絶縁膜2及びノッチ部6を残す工程と、除去部分を導電材料で埋め込むことによりゲート電極を形成する工程とを有する。

(もっと読む)

半導体装置およびその製造方法

【課題】同じ導電型を有するトランジスタであっても、用途に応じて特性を好ましいものにする。

【解決手段】半導体装置100は、半導体基板102上に形成された同じ導電型を有する第1のトランジスタ210および第2のトランジスタ212を含む。第1のトランジスタ210は、ゲート絶縁膜としてHf含有ゲート絶縁膜106を含み、第2のトランジスタ212は、ゲート絶縁膜としてシリコン酸化膜124を含むとともにHf含有膜を含まない。

(もっと読む)

半導体装置の製造方法

【課題】 デュアルメタルゲート構造およびデュアルHigh−k構造などのデュアル仕事関数構造の形成プロセスにおける素子分離膜の削れを防止することができる半導体装置の製造方法を提供する。

【解決手段】 第2ゲート電極用金属層10Aおよび第2キャップ層9を、第1ハードマスク8の一端部を被うように形成する。これによって、第1ハードマスク8を除去する段階では、STI膜2上のゲート絶縁膜用絶縁膜5が露出しないので、第1ハードマスク8を除去するためのエッチング液でSTI膜2上のゲート絶縁膜用絶縁膜5が除去されることを防止することができる。したがって、STI膜2が削られることを防止することができる。

(もっと読む)

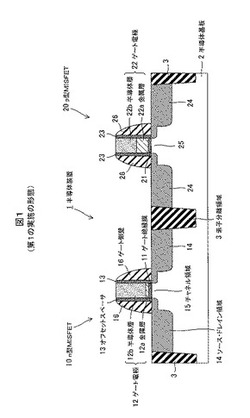

半導体装置及びその製造方法

【課題】高速動作が可能なMIPS構造を持つメタルゲートを含む半導体装置を得られるようにする。

【解決手段】半導体装置は、半導体基板1の上に形成されたゲート絶縁膜3と、該ゲート絶縁膜3の上に順次形成され、TiN膜4とポリシリコン膜5とにより構成されたゲート電極20の第2のゲート電極部20bと、半導体基板1の上にゲート電極20を覆うように形成された層間絶縁膜8とを有している。層間絶縁膜8及びポリシリコン膜5を貫通して形成されたコンタクト9は、TiN膜4と直接に接続されている。

(もっと読む)

半導体装置及びその製造方法

【課題】高誘電体材料を含むゲート絶縁膜とメタルゲート電極とを有する半導体装置の製造中にポリシリコンからなる残渣が素子分離領域上に生じる虞があり、不良の原因であった。

【解決手段】半導体基板10の第1の活性領域10a上には、第1のゲート絶縁膜13aと、第1の下層導電膜14a及び第1のシリコン膜18aを有する第1のゲート電極19aとを備えた第1導電型の第1のトランジスタが形成されており、半導体基板10の第2の活性領域10b上には、第2のゲート絶縁膜13bと、第2の下層導電膜14b及び第2のシリコン膜18bを有する第2のゲート電極19bとを備えた第2導電型の第2のトランジスタが形成されている。第1のゲート絶縁膜13aは高誘電体材料と第1の金属とを含有し、第1の下層導電膜14aは導電材料と第1の金属とを含有し、第2の下層導電膜14bは第1の下層導電膜14aと同一の導電材料を含有している。

(もっと読む)

半導体装置

【課題】ゲート金属起因の閾値変調効果が制御されたCMISFETを提供する。

【解決手段】半導体基板上に設けられたCMISFETにおいて、pMISFETのゲート電極は、第1のゲート絶縁膜上に形成された第1の金属層と、その上に形成されたIIA族及びIIIA族に属する少なくとも1つの金属元素を含む第1の上部金属層とを具備し、nMISFETのゲート電極は、第2のゲート絶縁膜上に形成された第2の金属層と、第2の金属層上に形成され、前記第1の上部金属層と実質的に同一組成の第2の上部金属層とを具備し、第1の金属層が第2の金属層よりも厚く、第1及び第2のゲート絶縁膜は前記金属元素を含み、第1のゲート絶縁膜に含まれる前記金属元素の原子密度が、第2のゲート絶縁膜に含まれる前記金属元素の原子密度よりも低い。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】製造安定性に優れた半導体装置およびその製造方法を提供する。

【解決手段】半導体装置の製造方法は、半導体基板13上にゲート絶縁膜21を設ける工程、ゲート絶縁膜21のnMOSトランジスタ形成領域を除いた領域にTa等を主成分とする第一の金属膜22を形成する工程、ゲート絶縁膜21、第一の金属膜22を覆うようにポリシリコン膜を形成する工程、ゲート絶縁膜21、ポリシリコン膜をエッチングにより選択的に除去し第一のダミーゲート電極を形成し、ゲート絶縁膜21、第一の金属膜22、ポリシリコン膜を選択的に除去し第二のダミーゲート電極を形成する。各ダミーゲート電極を、側壁絶縁膜で埋め込み、各ダミーゲートの上部のポリシリコン膜を除去し、絶縁層に凹部を形成した後、凹部内に第二の金属膜を積層し、CMOSのゲート電極とする。

(もっと読む)

半導体装置及びその製造方法

【課題】メタルゲート形成用等の金属原子が半導体基板、特にゲート絶縁膜に残存することによるゲートリーク電流の増大又はゲート電極の形成材料における仕事関数の変動を防止できるようにする。

【解決手段】まず、N型電界効果トランジスタを形成するNFET形成領域50NとP型電界効果トランジスタを形成するPFET形成領域50Pとを有する半導体基板1の上に、ゲート絶縁膜3を形成する。続いて、ゲート絶縁膜3の上に、第1のポリシリコン膜4を形成し、形成した第1のポリシリコン膜4におけるPFET形成領域に含まれる部分を除去することにより、PFET形成領域50Pからゲート絶縁膜3を露出する。その後、PFET形成領域50Pにおけるゲート絶縁膜3の上に窒化チタン膜6を形成する。

(もっと読む)

半導体装置およびその製造方法

【課題】high−k膜を含むFETにおいて、低抵抗金属として高融点金属を用いた場合のイオン注入時のゲートにおけるドーパント突き抜けの問題と、低抵抗金属のグレインサイズの下地依存に起因したPMISトランジスタとNMISトランジスタとのゲート抵抗の差を解決する。

【解決手段】high−k膜4上に形成されるゲート電極を、仕事関数金属膜5とその上部の第一の低抵抗膜6、第二の低抵抗膜7で構成したMISトランジスタにおいて、仕事関数金属膜5上の、タングステンからなる第一の低抵抗膜6のグレインサイズを前記第一の低抵抗膜6上の第二の低抵抗膜7のグレインサイズより小さくする。

(もっと読む)

半導体装置及びその製造方法

【課題】高誘電体材料を含むゲート絶縁膜とメタルゲート電極とを有する半導体装置の製造中にポリシリコンからなる残渣が素子分離領域上に生じる虞があり、不良の原因であった。

【解決手段】半導体基板10の第1の活性領域10a上には、高誘電体材料と第1の金属とを含有する第1のゲート絶縁膜13aと、下層導電膜15aと第1の導電膜18aと第1のシリコン膜19aとを有する第1のゲート電極30aとを備えた第1導電型の第1のトランジスタが形成されている。半導体基板10の第2の活性領域10b上には、高誘電体材料と第2の金属とを含有する第2のゲート絶縁膜13bと、第1の導電膜18aと同一の材料からなる第2の導電膜18bと第2のシリコン膜19bとを有する第2のゲート電極30bとを備えた第2導電型の第2のトランジスタが形成されている。

(もっと読む)

半導体装置

【課題】ゲート電極の構造が異なる2種類のトランジスタを形成する際のゲート絶縁膜の突き抜け及び基板掘れが生じにくい半導体装置を実現できるようにする。

【解決手段】半導体装置は、半導体基板11と、半導体基板11の第1の領域13に形成された第1のトランジスタ20と、第2の領域14に形成された第2のトランジスタ30とを備えている。第1のトランジスタ20は、第1のゲート絶縁膜21と、第1のゲート電極22とを有し、第2のトランジスタ30は、第2のゲート絶縁膜31と、第2のゲート電極32とを有している。第1のゲート絶縁膜21及び第2のゲート絶縁膜22は、第1の絶縁膜41と第2の絶縁膜42とを含む。第1のゲート電極22に含まれる元素と、第2のゲート電極32に含まれる元素とは少なくとも一部が異なっている。

(もっと読む)

二重仕事関数半導体デバイスおよびその製造方法

【課題】簡単化した集積機構を備えた二重仕事関数半導体デバイスおよびその製造方法を提供する。

【解決手段】二重仕事関数半導体デバイスは、第1実効仕事関数を有する第1ゲートスタック111を含む第1トランジスタと、第1実効仕事関数とは異なる第2実効仕事関数を有する第2ゲートスタック112を含む第2トランジスタとを備える。第1ゲートスタック111は、第1ゲート誘電体キャップ層104、ゲート誘電体ホスト層105、第1金属ゲート電極層106、バリア金属ゲート電極層107、第2ゲート誘電体キャップ層108、第2金属ゲート電極層109を含む。第2ゲートスタック112は、ゲート誘電体ホスト層105、第1金属ゲート電極層106、第2ゲート誘電体キャップ層108、第2金属ゲート電極層109を含む。第2金属ゲート電極層109は、第1金属ゲート電極層106と同じ金属組成からなる。

(もっと読む)

201 - 220 / 480

[ Back to top ]