Fターム[5F048BB13]の内容

MOSIC、バイポーラ・MOSIC (97,815) | ゲート (19,021) | 多層(2層)ゲート (2,461) | 3層以上 (480)

Fターム[5F048BB13]に分類される特許

461 - 480 / 480

半導体装置及びその製造方法

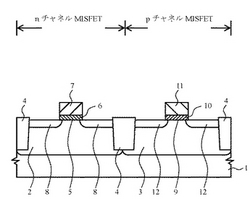

【課題】 High−k膜を用いたMISFETの電子移動度および正孔移動度を共に増加させ高性能の相補型MISFETを形成する。

【解決手段】 シリコン基板1の表面部にpウェル層2およびnウェル層3が形成され、素子分離領域4により区画されたnチャネルMISFETには、窒素添加のないnチャネル界面層5、窒素添加のないnチャネル高誘電体ゲート絶縁膜6およびnチャネルゲート電極7が形成されている。そして、n型ソース・ドレイン拡散層8が設けられている。これに対して、pチャネルMISFETでは、窒素添加のpチャネル界面層9、窒素添加のpチャネル高誘電体ゲート絶縁膜10およびpチャネルゲート電極11が形成されている。そして、p型ソース・ドレイン拡散層12が設けられている。

(もっと読む)

半導体装置及びその製造方法

【課題】微細化されたCMOS半導体装置に適したpMOSとnMOSにおいてそれぞれ適切に制御されたGe濃度分布及び形状を有するSi/SiGeゲート電極構造を備えた半導体装置を提供することである。

【解決手段】上記の課題を解決した半導体装置は、半導体基板上に形成された絶縁膜と、前記絶縁膜上に形成され、前記絶縁膜との界面近くで高いゲルマニウム濃度を有し、その反対側表面で低いゲルマニウム濃度を有する第1のゲート電極と、前記絶縁膜上に形成され、電極中でほぼ一様なゲルマニウム濃度を有し、6×1020atoms/cm3以上の濃度のn型不純物を有する第2のゲート電極とを具備する。

(もっと読む)

半導体装置およびその製造方法

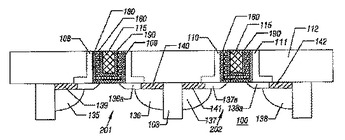

【課題】 従来のチャネル領域に不純物を注入することのみで閾値電圧を調整するよりも少ない不純物量で電界効果型トランジスタの閾値電圧を調整する。

【解決手段】 半導体装置100は、シリコン基板101と、シリコン基板101上に形成されたSiON膜113および多結晶シリコン膜106を含むP型MOSFET103を備える。多結晶シリコン膜106とSiON膜113との界面115に、Hf、Zr、Al、La、Pr、Y、Ti、TaおよびWからなる群から選択される一または二以上の金属が存在する構成とし、界面115における当該金属の濃度を5×1013atoms/cm2以上1.4×1015atoms/cm2未満とする。

(もっと読む)

金属ゲート電極半導体デバイス

高誘電率ゲート誘電体を有するNMOS及びPMOSトランジスタを含む相補型金属酸化物半導体集積回路が半導体基板上に形成される。ゲート誘電体上に金属障壁層が形成される。金属障壁層上に仕事関数設定金属層が形成され、仕事関数設定金属層上にキャップ金属層が形成される。  (もっと読む)

(もっと読む)

半導体装置及びその製造方法

【課題】 本発明の目的は、ゲート長が高精度に制御され、かつ、ショートチャネル効果を抑制する半導体装置及びその製造方法を提供することである。

【解決手段】 第1のゲート電極膜17aと、第1のゲート電極膜17aのゲート長よりも長いゲート長を具備する第2のゲート電極膜20とを有する2段型ゲート電極20aを形成することにより、ゲート長が高精度に制御される。また、エクステンション領域21は第2のゲート電極膜20をマスクにして不純物導入がされるため、ショートチャネル効果を抑制することができる。

(もっと読む)

多層ゲートスタック

プラズマによりパターン形成された窒化層を形成するために窒化層をエッチングすることからなる半導体構造体を製造する方法。窒化層は半導体の基板上にあり、フォトレジスト層は窒化層上にあり、プラズマは、少なくとも圧力10ミリトルでCF4及びCHF3のガス混合物から形成される。 (もっと読む)

半導体装置

【課題】 原子レベルで平坦な界面をもって基板上に堆積され、しかも低抵抗のシリサイド層を有する半導体装置を提供する。

【解決手段】 素子分離領域を有する半導体基板と、前記半導体基板に形成された拡散領域と、前記半導体基板上にゲート絶縁膜を介して形成されたゲート電極と、前記拡散領域上に形成されたシリサイド層(3)とを具備するMISトランジスタを含む半導体装置である。前記シリサイド層は、前記半導体基板との界面にEr、Gd、Tb、Dy、Ho、Tm、Yb、Lu、およびPtからなる群から選択される少なくとも1種の金属のシリサイドからなる界面層(5)を有することを特徴とする。

(もっと読む)

半導体装置及びその製造方法

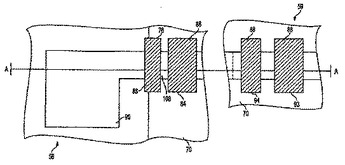

本発明は、それぞれ金属及びさらなる元素の両方を含む化合物の第1及び第2の導電材料を有するゲート領域(1D,2D)を持つNMOST1及びPMOST2を備えるCMOS装置(10)に関する。本発明によれば第1及び第2の導電材料は共に前記金属としてモリブデンとタングステンとを含む群から選択される金属を含む化合物を有し、前記第1の導電材料は前記さらなる元素として酸素を有し、前記第2の導電材料は前記さらなる元素としてカルコゲナイドを有する。本発明はこのような装置の魅力的な製造方法を提供する。  (もっと読む)

(もっと読む)

半導体装置

【課題】 低抵抗でゲート空乏化が起こらず、高温において安定であるとともに、仕事関数が制御されたゲート電極を有するCMISデバイスを提供する。

【解決手段】 素子分離領域を有する半導体基板と、前記半導体基板に形成されたソース/ドレイン領域、前記半導体基板上に形成されたゲート絶縁膜、および前記ゲート絶縁膜上に形成されたゲート電極を有するp型MISトランジスタと、前記半導体基板に形成されたソース/ドレイン領域、前記半導体基板上に形成されたゲート絶縁膜、および前記ゲート絶縁膜上に形成されたゲート電極を有するn型MISトランジスタとを具備するCMISデバイスである。前記p型MISトランジスタにおける前記ゲート電極は、少なくとも前記ゲート絶縁膜との界面に第1の金属を有し、前記n型MISトランジスタにおける前記ゲート電極は、少なくとも前記ゲート絶縁膜との界面に、前記第1の金属のホウ化物を有することを特徴とする。

(もっと読む)

半導体基板内の分離溝に隣接するコンタクト用開口の形成方法

【課題】フィールド分離マスに隣接する領域にコンタクト用開口を形成する半導体製造方法を提供する。

【解決手段】トレンチ形成・埋め込み法によって半導体基板の中にフィールド分離マスを形成し、該フィールド分離マスに隣接した基板上に基板マスキング層を形成する工程であって、前記フィールド分離マスの上面はエッチングストップキャップによって覆われ、その側壁は前記マスキング層によって覆われる工程と、前記分離マス側壁の少なくとも一部を露出するために、分離マスから分けて前記基板マスキング層を除去する工程と、露出した分離マス側壁上にエッチングストップカバーを形成する工程と、前記分離マス及び該分離マスに隣接する基板領域上に絶縁層を形成する工程と、前記分離マスエッチングストップキャップ及びカバーに対して選択的に、前記分離マスに隣接する前記絶縁層を貫通するコンタクト用開口をエッチング開口する工程とからなる、フィールド分離マスに隣接する領域にコンタクト用開口を形成する半導体製造方法。

(もっと読む)

PMOSを具備する半導体素子の形成方法

【課題】本発明はPMOSを具備する半導体素子を形成する方法を提供する。

【解決手段】前記方法によると、半導体基板の全面上にポリシリコン膜を形成する。前記ポリシリコン膜にP型不純物をドーピングする。熱処理工程を進行する。そして、前記P型不純物がドーピングされたポリシリコン膜の上部を第1厚さだけ除去する。これによって、漏洩電流を防止して、素子の速度を向上させることができるPMOSを具備する半導体素子を形成することができる。

(もっと読む)

半導体装置及びその製造方法

【課題】 低コストで歩留り良く製造でき、ゲート絶縁膜の信頼性が高く、しきい値電圧のばらつきが小さい半導体装置及びその製造方法を提供する。

【解決手段】 金属シリサイド膜4は、ゲート絶縁膜3上にアモルファスSi膜、金属膜及びSi膜5を順次形成し、熱処理によって金属膜をシリサイド化することにより得られる。金属膜の上にSi膜5を形成し、ゲート電極のゲート絶縁膜3側からのシリサイド化反応により金属シリサイド膜4を形成するため、不純物イオンがゲート電極とゲート絶縁膜3との界面に濃縮することが無い。これにより、不純物イオンのゲート絶縁膜3中又はチャネル領域への拡散を抑制し、MISFETのしきい値のばらつきを低減できる。また、ゲート絶縁膜3とゲート電極との界面における不純物の偏析を抑制し、ゲート電極の剥離を防止することができるため、ゲート絶縁膜3の信頼性が高い。

(もっと読む)

半導体装置およびその製造方法

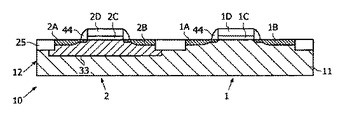

【課題】ゲルマニウムの拡散を防止する層を設けることで、シリコン・ゲルマニウム層中のゲルマニウムが必要以上に拡散するのを防止することを可能とする。

【解決手段】ゲート電極115にシリコン・ゲルマニウム層132を有するPチャネルトランジスタとゲート電極114にシリコン・ゲルマニウム層132を有するNチャネルトランジスタとを備えた半導体装置であって、前記ゲート電極は、前記シリコン・ゲルマニウム層132と、前記各シリコン・ゲルマニウム層上に形成したシリコン層133との積層構造からなり、前記各シリコン層133中にゲルマニウムの拡散を防止する拡散防止層134が形成されているものである。

(もっと読む)

高誘電率のゲート絶縁膜を有する半導体装置及びそれの製造方法

【課題】 本発明はゲート構造物として高誘電率を有する物質として、高誘電率を有する物質からなるゲート絶縁膜を含む半導体装置及びその製造方法に関する。

【解決手段】 半導体装置及びその製造方法において、基板上に形成され、ハフニウムシリコン酸化物含有固体物質を含むゲート絶縁膜パターンと前記ゲート絶縁膜パターン上に形成される第1ゲート導電膜パターンを含むゲート構造物及び前記ゲート構造物と隣接する基板の表面部位に配置されており、n型不純物がドーピングされたソース/ドレイン領域を含むことを特徴とする。

(もっと読む)

半導体装置の配線構造体及びその形成方法

【課題】 半導体装置の配線構造体およびその形成方法を提供する。

【解決手段】 この半導体装置は半導体基板100上に配置された層間絶縁膜、前記層間絶縁膜を貫通する第1コンタクト構造体181および第2コンタクト構造体182、前記層間絶縁膜上に配置されて前記第1コンタクト構造体と前記第2コンタクト構造体に連結される金属配線220を具備する。この際、前記第1コンタクト構造体は順次に積層された第1プラグおよび第2プラグ200を含み、前記第2コンタクト構造体は前記第2プラグを含む。

(もっと読む)

金属からなるゲート電極を形成するための方法

一の実施形態では、ゲート誘電体層(18)を基板(10)の上に形成し、次に第1金属層(26)を、ゲート誘電体層(18)の内、第1素子タイプが形成される予定の部分の上に選択的に堆積させる。第1金属層(26)とは異なる第2金属層(28)は、ゲート誘電体層(18)の内、第2素子タイプが形成される予定の露出部分の上に選択的に形成される。第1及び第2素子タイプの各々は異なる仕事関数を有することになる、というのは、第1及び第2素子タイプの各々が、ゲート誘電体と直接コンタクトする異なる金属を含むことになるからである。一の実施形態では、第1金属層(26)の選択的堆積は、ALDにより、かつ阻止層(24)を使用することにより行なわれ、阻止層は、第1金属層(26)を、ゲート誘電体層(18)の内、阻止層(24)によって覆われない部分の上にのみ選択的に堆積させることができるようにゲート誘電体層(18)の上に選択的に形成される。 (もっと読む)

粒状半導体材料を有する応力半導体構造

【課題】 チャネル移動度の向上を利用して性能を改善した半導体デバイス構造およびその製造方法を提供する。

【解決手段】 半導体デバイス構造を製造する方法であって、基板を設けるステップと、基板上に電極を設けるステップと、電極内に開口を有するくぼみを形成するステップと、くぼみ内に細粒半導体材料を配置するステップと、開口を覆ってくぼみ内に細粒半導体材料を閉じこめるステップと、上述のステップの結果として得られる構造をアニーリングするステップと、

を含む。

(もっと読む)

イメージャ用デュアルコンデンサ構造及びその製造方法

異なる画素内コンデンサ及び周辺コンデンサを含むCMOS及びCCD撮像装置とその製造方法を開示する。周辺回路において使用されるコンデンサと、画素自体の中で使用されるコンデンサの必要条件は異なる。2つの誘電体層を含むデュアルスタックコンデンサを提供することで、漏れが低減されると共に、静電容量を大きくすることができる。一回のマスキング工程を行って、1つの領域にはデュアル誘電体コンデンサを、そして第2の領域にはシングル誘電体コンデンサを存在させる。領域毎に異なる誘電体層が提供されるが、電極間絶縁体は両領域において単一の誘電体を含む。  (もっと読む)

(もっと読む)

集積回路のトランジスタにおける金属ゲート構造および形成方法(高性能デバイスの金属置換ゲートのための構造および方法)

【課題】 高性能デバイスの金属置換ゲートのための構造および形成方法を提供する。

【解決手段】 まず、半導体基板(240)上に設けたエッチ・ストップ層(250)上に、犠牲ゲート構造(260)を形成する。犠牲ゲート構造(300)の側壁上に、1対のスペーサ(400)を設ける。次いで、犠牲ゲート構造(300)を除去して、開口(600)を形成する。続けて、スペーサ(400)間の開口(600)内に、タングステン等の金属の第1の層(700)、窒化チタン等の拡散バリア層(800)、およびタングステン等の金属の第2の層(900)を含む金属ゲート(1000)を形成する。

(もっと読む)

半導体装置および電子機器

【課題】 本発明では剥離技術を用いることにより様々な基板上に薄膜素子を形成し、従来の技術では不可能であると考えられていた部分に薄膜素子を形成することにより、省スペース化を図ると共に耐衝撃性やフレキシビリティに優れた半導体装置を提供する。

【解決手段】 本発明では、剥離技術を用いて一旦基板から剥離させた膜厚50μm以下の素子形成層を基板上に固着することにより、様々な基板上に薄膜素子を形成することを特徴とする。例えば、可撓性基板上に固着された薄膜素子をパネルの裏面に貼り付けたり、直接パネルの裏面に固着したり、さらには、パネルに貼り付けられたFPC上に薄膜素子を固着することにより、省スペース化を図ることができる。

(もっと読む)

461 - 480 / 480

[ Back to top ]