Fターム[5F048BB13]の内容

MOSIC、バイポーラ・MOSIC (97,815) | ゲート (19,021) | 多層(2層)ゲート (2,461) | 3層以上 (480)

Fターム[5F048BB13]に分類される特許

101 - 120 / 480

半導体装置

【課題】多層配線間で形成される寄生容量を低減することを目的の一とする。

【解決手段】絶縁表面上に第1配線と、前記第1配線を覆う第1層間絶縁膜と、前記第1層間絶縁膜上の一部に接して第2層間絶縁膜と、前記第1層間絶縁膜及び前記第2層間絶縁膜上に第2配線とを有し、前記第1配線と前記第2配線とが重なっている領域には、前記第1層間絶縁膜と前記第2層間絶縁膜とが積層された半導体装置である。第1配線と第2配線間に層間絶縁膜が積層されていることで寄生容量の低減が可能となる。

(もっと読む)

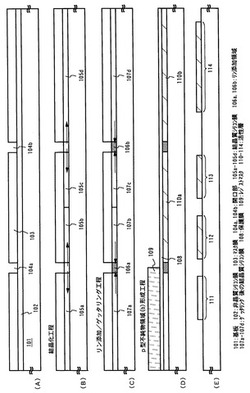

半導体装置の製造方法

【課題】メモリセル領域と高電圧トランジスタとの高濃度不純物拡散領域を同時にイオン注入で形成し、且つ高電圧トランジスタ側の方が浅くなるように形成する。

【解決手段】シリコン基板1にメモリセル領域にゲート電極MG、SGを形成し(図3(b))、周辺回路領域にゲート電極PG(図3(c))を形成する。周辺回路領域のゲート電極PGは、高電圧トランジスタについては厚い膜厚のゲート絶縁膜11が形成されている。ゲート絶縁膜11を残した状態でTEOS酸化膜9を成膜し、スペーサ加工をする。この時、スペーサ9aを形成すると共に、ゲート絶縁膜11を半分程度エッチングして11aとする。TEOS酸化膜10を形成後に高濃度不純物拡散領域1d、1eをイオン注入で深さd1、d2で形成する。高電圧トランジスタについてはゲート絶縁膜11aを介して行うので、浅く形成される。

(もっと読む)

半導体装置

【課題】待機電力の低減を実現する半導体装置の提供を、目的の一とする。

【解決手段】酸化物半導体を活性層として有するトランジスタをスイッチング素子として用い、該スイッチング素子で、集積回路を構成する回路への電源電圧の供給を制御する。具体的には、回路が動作状態のときに上記スイッチング素子により、当該回路への電源電圧の供給を行い、回路が停止状態のときに上記スイッチング素子により、当該回路への電源電圧の供給を停止する。また、電源電圧が供給される回路は、半導体を用いて形成されるトランジスタ、ダイオード、容量素子、抵抗素子、インダクタンスなどの、集積回路を構成する最小単位の半導体素子を、単数または複数有する。そして、上記半導体素子が有する半導体は、結晶性を有するシリコン(結晶性シリコン)、具体的には、微結晶シリコン、多結晶シリコン、単結晶シリコンを含む。

(もっと読む)

半導体装置の製造方法

【課題】p型MISトランジスタ及びn型MISトランジスタの特性を向上した相補型MISトランジスタを備えた半導体装置を容易に実現できるようにする。

【解決手段】半導体装置の製造方法は、p型半導体領域10A及びn型半導体領域10Bを有する半導体基板101の上に、高誘電率膜106、アルミニウムからなる第1のキャップ膜107及びハードマスク108を順次形成する。次に、第1のキャップ膜107及びハードマスク108におけるn型半導体領域10Bの上に形成された部分を除去する。その後、半導体基板101の上に、実効仕事関数を低下させる効果を有する元素を含む第2のキャップ膜109を形成する。

(もっと読む)

半導体装置及びその製造方法

【課題】デュアルメタルゲートプロセスを用いることなく、p型MISトランジスタ及びn型MISトランジスタ双方の特性を向上した半導体装置を実現できるようにする。

【解決手段】半導体装置は、p型半導体領域10Aの上に順次形成された第1の界面シリコン酸化膜105、アルミニウムを含む第1のゲート絶縁膜106A及び第1のゲート電極119Aと、n型半導体領域10Bの上に順次形成された第2の界面シリコン酸化膜105、実効仕事関数を低下させる効果を有する元素を含む第2のゲート絶縁膜106B及び第2のゲート電極119Aとを備えている。第1のゲート絶縁膜106Aの上部におけるアルミニウムの濃度は、1×1020/cm3以上である。第2のゲート絶縁膜106Bの上部におけるアルミニウムの濃度は、1×1019/cm3以下である。第1の界面シリコン酸化膜105の膜厚と第2の界面シリコン酸化膜105の膜厚との差は0.2nm以下である。

(もっと読む)

電子デバイス及びシステム、並びにその製造方法及び使用方法

幅広い電子デバイスのアレイ及びシステムにおける電力消費を低減する一式の新たな構造及び方法が提供される。これらの構造及び方法のうちの一部は、大部分が既存のバルクCMOSのプロセスフロー及び製造技術を再利用することで実現され、半導体産業及びより広いエレクトロニクス産業がコスト及びリスクを伴って代替技術へ切り替わることを回避可能にする。これらの構造及び方法のうちの一部は、深空乏化チャネル(DDC)設計に関係し、CMOSベースのデバイスが従来のバルクCMOSと比較して低減されたσVTを有することと、チャネル領域にドーパントを有するFETの閾値電圧VTがより一層正確に設定されることとを可能にする。DDC設計はまた、従来のバルクCMOSトランジスタと比較して強いボディ効果を有することができ、それにより、DDCトランジスタにおける電力消費の有意義な動的制御が可能になる。  (もっと読む)

(もっと読む)

半導体装置及びその製造方法

【課題】MIPS構造等のゲート電極と同時形成が可能であり且つ抵抗が高い抵抗素子を有する半導体装置及びその製造方法を提供する。

【解決手段】基板上に金属含有膜108及びポリシリコン膜109を順次形成する工程と、前記金属含有膜及び前記ポリシリコン膜を抵抗素子形状にパターニングする工程と、前記金属含有膜の少なくとも一部分を除去することにより、前記ポリシリコン膜の下に中空領域119を形成する工程とを備えている。

(もっと読む)

半導体装置の作製方法

【課題】基板処理の効率を高めることができ、また半導体膜の移動度を高めることができるレーザー結晶化法を用いた半導体製造装置を提供する。

【解決手段】半導体膜を成膜する成膜装置と、レーザー装置とを備えたマルチチャンバー方式の半導体製造装置であり、レーザー装置は、被処理物に対するレーザー光の照射位置を制御する第1の手段と、レーザー光を発振する第2の手段(レーザー発振装置1213)と、前記レーザー光を加工または集光する第3の手段(光学系1214)と、前記第2の手段の発振を制御し、なおかつ第3の手段によって加工されたレーザー光のビームスポットがマスクの形状のデータ(パターン情報)に従って定められる位置を覆うように前記第1の手段を制御する第4の手段とを有する。

(もっと読む)

半導体装置およびその製造方法

【課題】ゲート電極とプラグとの接続信頼性を向上することができる技術を提供する。

【解決手段】本発明では、MISFETのゲート電極G1を金属膜MF2とポリシリコン膜PF1の積層膜から構成するMIPS電極を前提とする。そして、このMIPS電極から構成されるゲート電極G1のゲート長に比べて、ゲートコンタクトホールGCNT1の開口径を大きく形成する第1特徴点と、ゲート電極G1を構成する金属膜MF2の側面に凹部CP1を形成する第2特徴点により、さらなるゲート抵抗(寄生抵抗)の低減と、ゲート電極G1とゲートプラグGPLG1との接続信頼性を向上することができる。

(もっと読む)

半導体装置及びその製造方法

【課題】n型MISトランジスタとp型MISトランジスタとで異なる閾値電圧制御用金属が高誘電率ゲート絶縁膜に添加されたトランジスタ構造において、トランジスタ特性の変動を防止できるようにする。

【解決手段】第1の活性領域1a上から素子分離領域2上を経て第2の活性領域1b上まで、ゲート絶縁膜となる高誘電率膜6が形成されている。第1の活性領域1aに隣接する部分の素子分離領域2の上部には第1の切り欠き部2aが形成されている。第2の活性領域1bに隣接する部分の素子分離領域2の上部には第2の切り欠き部2bが形成されている。第2の切り欠き部2bは第1の切り欠き部2aよりも浅く形成されている。

(もっと読む)

SOI基板の作製方法及び半導体装置の作製方法

【課題】平坦性を確保しつつ、結晶性の高い半導体膜を有する、SOI基板の作製方法を提供することを、目的の一とする。

【解決手段】分離により絶縁膜上に単結晶の半導体膜を形成した後、該半導体膜の表面に存在する自然酸化膜を除去し、半導体膜に対して第1のレーザ光の照射を行う。第1のレーザ光の照射は、希ガス雰囲気下、窒素雰囲気下または減圧雰囲気下にて、半導体膜の任意の一点におけるレーザ光のショット数を7以上、より好ましくは10以上100以下とする。そして、第1のレーザ光の照射を行った後、半導体膜に対して第2のレーザ光の照射を行う。第2のレーザ光の照射は、希ガス雰囲気下、窒素雰囲気下または減圧雰囲気下にて、半導体膜の任意の一点におけるレーザ光のショット数を0より大きく2以下とする。

(もっと読む)

半導体装置の製造方法

【課題】高誘電率ゲート絶縁膜およびメタルゲート電極を有するMISFETを備えた半導体装置の信頼性向上を図る。

【解決手段】nチャネル型MISFET用の高誘電率ゲート絶縁膜としてHfとLaとOとを主成分として含有するHf含有絶縁膜4aを形成し、pチャネル型MISFET用の高誘電率ゲート絶縁膜としてHfとAlとOとを主成分として含有するHf含有絶縁膜4bを形成する。それから、金属膜7とシリコン膜8を形成し、これらをドライエッチングでパターニングしてゲート電極GE1,GE2を形成する。その後、ゲート電極GE1,GE2で覆われない部分のHf含有絶縁膜4a,4bをウェットエッチングで除去するが、この際、フッ酸を含有しない酸性溶液でのウェット処理とアルカリ性溶液でのウェット処理とを行ってから、フッ酸を含有する酸性溶液でのウェット処理を行う。

(もっと読む)

半導体装置及びその製造方法

【課題】ナローチャネル特性の劣化を抑制する。

【解決手段】素子分離領域STIは、半導体基板100に形成されたトレンチ104内に設けられており、トレンチ104の側壁上に形成された下地絶縁膜105を有している。素子形成領域100a上にはゲート絶縁膜112が形成されており、ゲート絶縁膜112は高誘電率膜110を有している。高誘電率膜110の第1の部分110aは、素子形成領域100aにおける上面上に形成されており、高誘電率膜110の第2の部分110bは、素子形成領域における上部側面104a上に下地絶縁膜105を介して形成されている。第2の部分110bと下地絶縁膜105との間には、MISトランジスタの閾値電圧を変更する金属を含有する第1のキャップ膜106が設けられている。

(もっと読む)

半導体装置の製造方法及びそれを用いた半導体装置

【課題】MIPS構造を採るメタル膜とコンタクトプラグとの界面抵抗を低減できるようにする。

【解決手段】まず、半導体基板1の上に、ゲート絶縁膜3を形成し、形成したゲート絶縁膜3の上に、TiN膜4及びポリシリコン膜5を順次形成する。続いて、ポリシリコン膜5にTiN膜4を露出するコンタクトホール5aを形成する。続いて、ポリシリコン膜5における第1のコンタクトホール5aの少なくとも底面及び壁面上に金属膜7を形成する。

(もっと読む)

PFETチャネルSiGeを有する金属ゲート及び高k誘電体デバイス

【課題】SiGeから成るチャネルを有し、金属ゲート及び高kゲート誘電体を有するPFETを提供する。

【解決手段】Si表面上にSiGe層10をエピタキシャル成長させ、SiGe層の上に、高k誘電体及び金属をブランケット配置し、ゲートスタックを形成した後、NFET側のゲート誘電体、及びSiGe層を除去し、第2の高k誘電体53及び第2の金属52を配置する。PFETは、SiGeチヤネル10の上の高k誘電体を有するゲート誘電体、金属を有するゲート及び、シリサイドを有するソース、ドレインから成る。NFETは、第2の高k誘電体53、第二の金属52を有するゲート及び、シリサイドを有するソース、ドレインからなる。基板表面上のエピタキシャルSiGe層は、PFETのチヤネルのみに形成される。PFET及びNFETデバイス・パラメータは、各ゲート誘電体及びゲートスタックの組成によって別個に最適化することができる。

(もっと読む)

半導体デバイスおよびその製造方法

【課題】複数ゲートトランジスタの改良された構造、およびその製造プロセスの提供。

【解決手段】相補型金属酸化膜半導体(CMOS)デバイス100は、第1のパラメータを有する少なくとも2つの第1のゲート電極を備えたPMOSトランジスタと、上記第1のパラメータとは異なる第2のパラメータを有する少なくとも2つの第2のゲート電極を備えたNMOSトランジスタと、を有している。上記第1のパラメータおよび上記第2のパラメータは、上記PMOSおよびNMOSトランジスタの上記ゲート電極材料120の厚さ、またはドーパントプロファイルを含んでいる。上記少なくとも2つの第1のゲート電極および上記少なくとも2つの第2のゲート電極の上記第1および第2のパラメータは、それぞれ、上記PMOSおよびNMOSトランジスタの仕事関数を規定する。

(もっと読む)

半導体装置とその製造方法

【課題】SiGe層を用いてPチャネル型トランジスタのチャネル形成領域に圧縮応力を印加すると共に、リーク電流を低減する。

【解決手段】半導体装置120は、半導体基板100の表面部に形成されたソース領域及びドレイン領域122と、これらに挟まれたチャネル形成領域上にゲート絶縁膜101を介して形成されたゲート電極102とを含むPチャネル型トランジスタを備える。ゲート電極102の両側それぞれにおいて半導体基板100にリセスが形成され、リセスに、SiGeからなる第1エピタキシャル層111と、その上に形成され且つSiからなる第2エピタキシャル層112と、その上に形成され且つSiGeからなり、チャネル形成領域を挟む第3エピタキシャル層113とを備える。ソース領域及びドレイン領域122は、第3エピタキシャル層113中に形成され、且つ、それぞれの接合深さがいずれも第3エピタキシャル層133の深さよりも浅い。

(もっと読む)

半導体装置

【課題】 半導体装置に関し、ソース・ドレイン領域を実効的に埋込Si混晶層で構成する際の電気的特性を向上する

【解決手段】 一導電型シリコン基体と、一導電型シリコン基体上に設けたゲート絶縁膜と、ゲート絶縁膜の上に設けたゲート電極とゲート電極の両側の一導電型シリコン基体に設けた逆導電型エクステンション領域と、逆導電型エクステンション領域に接するとともに、一導電型シリコン基体に形成された凹部に埋め込まれた逆導電型Si混晶層とを備えた半導体装置であって、逆導電型Si混晶層が、第1不純物濃度Si混晶層/第2不純物濃度Si混晶層/第3不純物濃度Si混晶層を有し、第2不純物濃度を第1不純物濃度及び第3不純物濃度よりも高くする。

(もっと読む)

半導体装置及びその製造方法

【課題】高誘電体ゲート絶縁膜/メタルゲート電極のMOSトランジスタ構造において、メタルゲート電極側壁の酸化層を抑制し、トランジスタ駆動能力を改善する。

【解決手段】基板101上に、金属含有膜110を形成する工程(a)と、反応室内において金属含有膜にアンモニアラジカルを曝露する工程(b)と、反応室内に不活性ガスを供給し、工程(b)において生じたガスを排気する工程(c)と、工程(b)及び工程(c)を所定の回数繰り返した後に、大気曝露することなく、反応室内において金属含有膜110を覆うシリコン窒化膜100aを形成する工程(d)とを備える。

(もっと読む)

半導体装置及びその製造方法

【課題】MOSFETの性能をより向上する。

【解決手段】半導体装置の製造方法は、半導体基板11上に、ゲート絶縁膜材料とメタルゲート電極材料とを含む積層膜を堆積する工程と、マスク層19を用いて積層膜を加工し、半導体基板11上にゲート絶縁膜15及びメタルゲート電極16を含むゲート構造を形成する工程と、ゲート構造の側面に、絶縁物からなる側壁20を形成する工程と、側壁20をマスクとして半導体基板11に不純物を導入し、エクステンション領域21及びハロー領域22を形成する工程と、側壁20をマスクとして半導体基板11を掘り下げ、半導体基板11にリセス領域26を形成する工程と、リセス領域26にSiGe層27を形成する工程と、側壁20の側面に、絶縁物からなる側壁28を形成する工程と、マスク層19をドライエッチングする工程とを含む。

(もっと読む)

101 - 120 / 480

[ Back to top ]