Fターム[5F048BB13]の内容

MOSIC、バイポーラ・MOSIC (97,815) | ゲート (19,021) | 多層(2層)ゲート (2,461) | 3層以上 (480)

Fターム[5F048BB13]に分類される特許

141 - 160 / 480

半導体装置の製造方法および半導体装置

【課題】PチャネルMOSFETの閾値電圧の上昇を防ぎつつ、NチャネルMOSFETの閾値電圧の制御を確実に行う。

【解決手段】半導体装置1は、半導体基板10にゲート絶縁膜を形成し、NチャネルMOSFET形成領域に形成されたゲート絶縁膜に開口部を有し、かつゲート絶縁膜を覆うマスクを形成し、NチャネルMOSFET形成領域に位置するゲート絶縁膜上、およびPチャネルMOSFET形成領域に形成されたマスク上に第1の金属層を形成し、NチャネルMOSFET形成領域に形成されたゲート絶縁膜中に第1の金属層を形成する金属を熱処理により拡散させること、により製造される。

(もっと読む)

表示装置

【課題】狭額縁化が可能であり、表示特性に優れた表示装置を提供する。

【解決手段】第1の逆スタガ型薄膜トランジスタ及び第2の逆スタガ型薄膜トランジスタにより構成されるEDMOS回路を有する論理回路部を有し、第1の逆スタガ型薄膜トランジスタは、第1のゲート電極、ゲート絶縁層、第1の半導体層、第1の一対の不純物半導体層、及び第1の一対の配線を有し、第1の半導体層は、ドナーとなる不純物元素を含む微結晶半導体層と、混合領域と、非晶質半導体を含む層とが積層され、第2の逆スタガ型薄膜トランジスタは、第2のゲート電極、ゲート絶縁層、第2の半導体層、第2の一対の不純物半導体層、及び第2の一対の配線を有し、第2の半導体層は、微結晶半導体層と、非晶質半導体層とが積層されている表示装置。

(もっと読む)

SOI基板の作製方法

【課題】単結晶シリコン基板よりも大面積な基板に、均一な質を有する複数の単結晶半導体層を貼り付けたSOI基板の作製方法を提供することを課題とする。

【解決手段】熱処理において、ベース基板支持及び単結晶半導体基板保持のトレイとして、凹部の底が深く、ベース基板に貼り付けられた単結晶半導体基板と接触しないトレイを用いて、単結晶半導体基板の熱分布の均一化を図る。また、該トレイの各々の凹部の間にベース基板支持部を設けることによって、該トレイとベース基板との接触面積を低減する。以上より、単結晶半導体基板から単結晶半導体層を分離する熱処理の際、単結晶半導体基板及びベース基板の熱分布が均一になるようにする。

(もっと読む)

半導体装置及びその製造方法

【課題】pMOSトランジスタにcSiGeとeSiGeを適用し、且つゲート絶縁膜におけるダメージ発生を防止でき、素子特性の向上及びしきい値制御性の向上をはかる。

【解決手段】pMOSトランジスタのチャネル部及びソース・ドレイン領域にSiGeを用いた半導体装置において、Si基板202上の一部に形成され、pMOSトランジスタのチャネルとなる第1のSiGe層205と、第1のSiGe層205上にゲート絶縁膜206を介して形成されたゲート電極208と、pMOSトランジスタのソース・ドレイン領域に埋め込み形成され、且つチャネル側の端部が基板表面よりも深い位置でチャネル側に突出するように形成された第2のSiGe層214と、第1のSiGe層205と第2のSiGe層214とを分離するように、基板の表面部でSiGe層205,214間に挿入されたSi層222とを備えた。

(もっと読む)

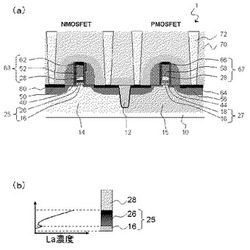

半導体装置の製造方法

【課題】

CMOSトランジスタの一方のキャップ誘電体膜に対するアニール条件を、CMOSトランジスタの他方のキャップ誘電体膜に対するアニール条件とは独立に設定する。

【解決手段】

シリコン基板に、n型ウェルおよびp型ウェルを形成し、シリコン基板上方にHfO等の第1の高誘電率絶縁膜、AlO等の第1のキャップ誘電体膜を積層し、p型ウェル上方から、少なくとも第1のキャップ誘電体膜を除去し、第1の温度で第1のアニールを行なって、第1のキャップ誘電体膜の構成元素Al等をn型ウェル上方の第1の高誘電率絶縁膜中へ拡散させ、p型ウェルおよびn型ウェル上方にHfO等の第2の高誘電率絶縁膜、LaO等の第2のキャップ誘電体膜を積層し、n型ウェル上方の第2のキャップ誘電体膜を除去し、第1の温度より低い第2の温度で、第2のアニールを行なって、第2のキャップ誘電体膜の構成元素La等をp型ウェル上方の第2の高誘電率絶縁膜中へ拡散させる。

(もっと読む)

半導体装置及びその作製方法

【課題】酸化物半導体層を用いた薄膜トランジスタにおいて、酸化物半導体層とソース電極層又はドレイン電極層との間のコンタクト抵抗を低減し、電気特性を安定させた薄膜トランジスタを提供する。また、該薄膜トランジスタの作製方法を提供する。

【解決手段】酸化物半導体層を用いた薄膜トランジスタにおいて、酸化物半導体層の上に、酸化物半導体層より導電率の高いバッファ層を形成し、該バッファ層の上にソース電極層及びドレイン電極層を形成し、酸化物半導体層とソース電極層又はドレイン電極層とがバッファ層を介して電気的に接続されるように薄膜トランジスタを形成する。また、バッファ層に逆スパッタ処理及び窒素雰囲気下での熱処理を行うことにより、酸化物半導体層より導電率の高いバッファ層を形成する。

(もっと読む)

半導体装置およびその製造方法

【課題】簡易な手順で、高誘電率ゲート絶縁膜とメタルゲート電極とのゲートスタック構造を有する相補型トランジスタの閾値を調整する。

【解決手段】相補型トランジスタの第1導電型のトランジスタ(162)の閾値電圧を変化させる第1の調整用金属を第1導電型のトランジスタ(162)および第2導電型のトランジスタ(160)に同時に添加し、第2導電型のトランジスタ(160)のメタルゲート電極(110a)上から第1の調整用金属の拡散を抑制する拡散抑制元素を添加する。

(もっと読む)

半導体装置及びその製造方法

【課題】High-k/metalゲート電極構造において各極性のFETに要求される仕事関数値を実現する。

【解決手段】第1の領域と第2の領域とを有する半導体基板101の上にゲート絶縁膜103を形成する。次に、ゲート絶縁膜103の上に第1の金属窒化膜105を堆積する。次に、第1の金属窒化膜105における第2の領域に位置する部分を除去することにより、ゲート絶縁膜103における第2の領域に位置する部分を露出させる。次に、ゲート絶縁膜103における第2の領域に位置する部分の上に、第1の金属窒化膜105と同じ金属窒化物からなる第2の金属窒化膜107を形成する。

(もっと読む)

半導体装置およびその製造方法

【課題】メタルゲート電極を有するpチャネル型電界効果トランジスタにおいて、所望するしきい値電圧を安定して得ることのできる技術を提供する。

【解決手段】半導体基板1上に形成されたHfSiON膜からなるゲート絶縁膜5h上に、Me−O−Al−O−Me結合を含むMe1−xAlxOy(0.2≦x≦0.75、0.2≦y≦1.5)組成の導電性膜を一部に有するメタルゲート電極6、またはMe−O−Al−N−Me結合を含むMe1−xAlxN1−zOz(0.2≦x≦0.75、0.1≦z≦0.9)組成の導電性膜を一部に有するメタルゲート電極6を形成する。

(もっと読む)

半導体装置およびその製造方法

【課題】基板上に抵抗素子を備える半導体装置において、シリコン抵抗素子の抵抗値の低下を防ぐ。

【解決手段】半導体装置1は、基板10上に、MIPS構造を有するMOSトランジスタとシリコン抵抗素子を備える。抵抗素子は、基板10の上に設けられた金属膜28と、金属膜28の上に設けられた絶縁膜30と、絶縁膜30の上に設けられたシリコン層37と、からなる。絶縁膜30は、シリコン酸化膜、シリコン窒化膜、HfSiON、HfO2、ZrO2、HfAlO、Al2O3から選ばれる少なくとも一つを有する。

(もっと読む)

半導体装置の製造方法

【課題】ハーフピッチサイズが32nm以下のCMISデバイスを有する半導体装置において、nチャネル型電界効果トランジスタおよびpチャネル型電界効果トランジスタのそれぞれの閾値電圧を適切に設定することのできる技術を提供する。

【解決手段】pMIS形成領域に、主としてAlが拡散した高誘電体膜5h(例えばHfO2膜)により構成されるゲート絶縁膜5ならびに下層メタルゲート電極6Dと上層メタルゲート電極6Uとの積層膜からなるメタルゲート電極6を有するpMIS100pを形成し、nMIS形成領域に、主としてLa(ランタン)が拡散した高誘電体膜5h(例えばHfO2膜)により構成されるゲート絶縁膜11ならびに上層メタルゲート電極6Uからなるメタルゲート電極12を有するnMIS100nを形成する。

(もっと読む)

半導体装置及びその製造方法

【課題】EOTの増大及びキャリア移動度の低下を抑制しつつ、半導体基板表面に形成されている酸化膜と高誘電率絶縁膜との界面に、しきい値電圧を低減する電気双極子を形成可能な金属を添加する。

【解決手段】半導体基板100上にゲート絶縁膜140を介してゲート電極150が形成されている。ゲート絶縁膜140は、酸素含有絶縁膜101と、第1の金属を含む高誘電率絶縁膜102とを有する。高誘電率絶縁膜102は、第1の金属とは異なる第2の金属をさらに含む。高誘電率絶縁膜102における第2の金属の組成比が最大になる位置は、高誘電率絶縁膜102と酸素含有絶縁膜101との界面及び高誘電率絶縁膜102とゲート電極150との界面のそれぞれから離れている。

(もっと読む)

半導体装置およびその製造方法

【課題】基板上にヒューズ素子を備える半導体装置において、ヒューズを切断しやすくし、かつヒューズ切断状態を確実に得る。

【解決手段】半導体装置1は、基板10上に、MIPS構造を有するMOSトランジスタとヒューズ素子100を備える。ヒューズ素子100は、基板10の上に設けられた金属膜28と、金属膜28の上に設けられた絶縁膜30と、絶縁膜30の上に設けられたシリコン層34と、シリコン層34の上の少なくとも一部を覆うシリサイド層73と、からなる。

(もっと読む)

復調信号生成回路および復調信号生成回路を有する半導体装置

【課題】変調度の小さい搬送波であっても、安定して動作させる復調信号生成回路を有する半導体装置を提供する。

【解決手段】半導体装置は、アンテナ回路に接続された第1の復調回路と、アンテナ回路に接続された、第1の復調回路とは逆の極性の電気信号を復調する第2の復調回路と、第1の復調回路の出力部に接続された入力部を有する第1のバイアス回路と、第2の復調回路の出力部に接続された入力部を有する第2のバイアス回路と、第1の入力部と第2の入力部を有するコンパレータと、コンパレータの出力部に接続されたアナログバッファ回路と、アナログバッファ回路の出力部に接続されたパルス検出回路を有し、第1のバイアス回路の出力部は第1の入力部に接続され、第2のバイアス回路の出力部は第2の入力部に接続され、パルス検出回路は第1のバイアス回路及び第2のバイアス回路に接続されている復調信号生成回路を有する。

(もっと読む)

半導体装置の製造方法

【課題】 トランジスタのスイッチング速度低下を防止することが可能な半導体装置の製造方法を提供する。

【解決手段】 本発明では、半導体基板100上にゲート絶縁膜104を形成する工程と、ゲート絶縁膜104上に金属膜107を形成する工程と、金属膜107上に金属シリコン化合物膜108を連続して堆積する工程と、金属シリコン化合物膜108上にシリコン膜110を形成する工程と、金属膜107、金属シリコン化合物膜108及びシリコン膜110を加工する工程と、を備える。

(もっと読む)

半導体装置の作製方法

【課題】TFTを用いた半導体装置において、TFT中の汚染不純物を低減し、信頼性のあるTFTを得ることを課題とする。

【解決手段】ガラス基板上のTFTの被膜に存在する汚染不純物を、フッ素を含有する酸性溶液を被膜表面に接触させ、酸性溶液を一定方向に流すことにより、被膜表面の汚染不純物を除去することにより、信頼性のあるTFTを得ることができる。なお、酸性溶液は、フッ酸とフッ化アンモニウムの混合比が体積比で1:50のバッファードフッ酸を用いる。

(もっと読む)

スレショルド電圧を有する電界効果トランジスタ、及びその製造方法

【課題】相異なるスレショルド電圧を有する電界効果トランジスタを提供する。

【解決手段】ドープ半導体ウエル上に、複数種のゲート・スタック(100〜600)が形成される。ドープ半導体ウエル(22、24)上に、高誘電率(high−k)ゲート誘電体(30L)が形成される。一つのデバイス領域中に金属ゲート層(42L)が形成され、他のデバイス領域(200、400、500、600)ではhigh−kゲート誘電体は露出される。該他のデバイス領域中に、相異なる厚さを有するスレショルド電圧調整酸化物層が形成される。次いで、スレショルド電圧調整酸化物層を覆って導電性ゲート材料層(72L)が形成される。電界効果トランジスタの一つの型は、high−kゲート誘電体部分を包含するゲート誘電体を包含する。電界効果トランジスタの他の型は、high−kゲート誘電体部分と、相異なる厚さを有する第一スレショルド電圧調整酸化物部分とを包含するゲート誘電体を包含する。相異なるゲート誘電体スタックと、同一のドーパント濃度を有するドープ半導体ウエルを用いることによって、相異なるスレショルド電圧を有する電界効果トランジスタが提供される。

(もっと読む)

SOI基板の作製方法

【課題】結晶性に優れた結晶質半導体層を有するSOI基板を提供する。

【解決手段】支持基板上に、バッファ層を介して単結晶半導体基板から分離させた単結晶半導体を部分的に形成する。単結晶半導体基板は、加速されたイオンの照射とそれに伴う脆化層の形成、及び熱処理により、単結晶半導体を分離する。単結晶半導体上に非単結晶半導体層を形成し、レーザビームを照射することにより、非単結晶半導体層を結晶化させて、SOI基板を作製する。

(もっと読む)

半導体装置の製造方法及び半導体装置

【課題】NチャネルMOSFETとPチャネルMOSFETを備える半導体装置において、PチャネルMOSFETの閾値電圧のばらつきを抑制し、製造歩留まりを上げる。

【解決手段】半導体基板103の上にゲート絶縁膜110A、110Bを形成した後、PチャネルMOSFET形成領域107に形成されたゲート絶縁膜110Bを第一マスク111で覆う。次に、NチャネルMOSFET形成領域106およびPチャネルMOSFET形成領域107に第一金属層112を形成し、PチャネルMOSFET形成領域107から第一金属層112および第一マスク111を除去することにより、PチャネルMOSFET形成領域107に形成されたゲート絶縁膜110Bを露出させる。その後、NチャネルMOSFET形成領域106およびPチャネルMOSFET形成領域に107ゲート電極を形成する。

(もっと読む)

半導体装置及びその製造方法

【課題】(110)面を主面とする半導体基板に形成されたp型MISトランジスタを備えた半導体装置において、p型MISトランジスタのさらなる性能向上を図る。

【解決手段】半導体装置は、(110)面を主面とする半導体基板10に形成されたp型MISトランジスタPTrを備えた半導体装置である。p型MISトランジスタPTrは、半導体基板10における第1の活性領域10a上に形成された第1のゲート絶縁膜13aと、第1のゲート絶縁膜13a上に形成され第1の金属膜14a及び第1の金属膜14a上に形成された第1のシリコン膜15aからなる第1のゲート電極14Aとを備えている。第1の金属膜14aは、膜厚が1nm以上であって且つ10nm以下である。

(もっと読む)

141 - 160 / 480

[ Back to top ]