Fターム[5F048BB13]の内容

MOSIC、バイポーラ・MOSIC (97,815) | ゲート (19,021) | 多層(2層)ゲート (2,461) | 3層以上 (480)

Fターム[5F048BB13]に分類される特許

161 - 180 / 480

半導体装置及びその製造方法

【課題】(110)面を主面とする半導体基板に形成されたp型MISトランジスタを備えた半導体装置において、p型MISトランジスタのさらなる性能向上を図る。

【解決手段】半導体装置は、(110)面を主面とする半導体基板10に形成されたp型MISトランジスタPTrを備えた半導体装置である。p型MISトランジスタPTrは、半導体基板10における第1の活性領域10a上に形成された第1のゲート絶縁膜13aと、第1のゲート絶縁膜13a上に形成され第1の金属膜14a及び第1の金属膜14a上に形成された第1のシリコン膜15aからなる第1のゲート電極14Aとを備えている。第1の金属膜14aは、膜厚が1nm以上であって且つ10nm以下である。

(もっと読む)

金属High−kFETのためのデュアル金属およびデュアル誘電体集積

【課題】本発明は、一つの実施形態において半導体デバイスを形成する方法を提供する。

【解決手段】該方法は、第一導電型領域および第二導電型領域を包含する基板を用意するステップと、基板の第一導電型領域および第二導電型領域の上のゲート誘電体とHigh−kの該ゲート誘電体上を覆う第一金属ゲート導体を包含するゲート・スタックを形成するステップと、第一金属ゲート導体の第一導電型領域中に所在する部分を除去して、第一導電型領域中に所在するゲート誘電体を露出するステップと、基板に対し窒素ベース・プラズマを印加するステップであって、窒素ベース・プラズマは、第一導電型領域中に所在するゲート誘電体を窒化し、第二導電型領域中に所在する第一金属ゲート導体を窒化する、該印加するステップと、少なくとも第一導電型領域中に所在するゲート誘電体上を覆う第二金属ゲート導体を形成するステップと、を含む。

(もっと読む)

半導体装置およびその製造方法

【課題】MIPS構造を有する電界効果トランジスタにおいて、金属ゲート電極とポリシリコンゲート電極との接触抵抗を低減することにより、AC動作を向上させる。

【解決手段】半導体装置1は、半導体基板10上に電界効果トランジスタを有する。電界効果トランジスタは、ゲート絶縁膜25、27とゲート電極63、71と、を備える。さらに、ゲート電極63、71は第1金属からなる第1電極層22と、第2金属からなる第2電極層26、34と、シリコン層からなる第3電極層62、70と、を含む積層構造である。第2金属は、シリコン層の多数キャリアに対する第1電極層22と第3電極層62、70とのバンド不連続を緩和する仕事関数を有する材料である。

(もっと読む)

半導体装置及びその製造方法

【課題】微細化に対応可能であり、不純物拡散領域上に形成したコンタクトプラグが近傍の導電材料とショートすることを防止する配線構造を有する半導体装置を提供する。

【解決手段】半導体基板内の不純物拡散領域22上に選択エピタキシャル成長法により、第1の層16aを形成する工程と、第1の層16a上に、選択エピタキシャル成長法により第2の層18を形成する工程と、第2の層18上に導電材料を充填することにより、コンタクトプラグ21を形成する工程と、を有する。

(もっと読む)

液晶表示装置

【課題】アクティブマトリクス型の液晶表示装置の画面の大面積化を可能とするゲート電極とゲート配線を提供することを第1の課題とする。

【解決手段】同一基板上に表示領域と、表示領域の周辺に設けられた駆動回路と、を有し、表示領域は、第1の薄膜トランジスタを有し、駆動回路は、第2の薄膜トランジスタを有し、第1の薄膜トランジスタと第2の薄膜トランジスタは、リンがドープされたシリコンでなるゲート電極を有し、ゲート電極は、チャネル形成領域の外側に設けられた接続部でアルミニウムまたは銅を主成分とする層とタンタル、タングステン、チタン、モリブデンから選ばれた少なくとも1種を主成分とする層とを有する配線と電気的に接続する。

(もっと読む)

半導体装置の製造方法

【課題】 閾値電圧の低い金属ゲート電極においてPMISFETの製造方法を提供する。

【解決手段】 半導体基板10上にPMISFETを作製する方法であって、半導体基板10上に絶縁膜20を形成する工程と、半導体基板10及び絶縁膜20をハロゲン化合物を含むガスにさらして、絶縁膜20上に吸着層110を形成する工程と、吸着層110上に金属を含むゲート電極40を形成して、吸着層110とゲート電極40を反応させて、吸着層110をハロゲン含有金属層にする工程とを有することを特徴とする半導体装置の製造方法。

(もっと読む)

半導体装置の製造方法

【課題】異なる積層構造を有する異なる導電型のトランジスタにおいて、ゲート電極における形状不良の抑制を図る。

【解決手段】半導体装置の製造方法は、第1導電型のMISFETを有する第1領域及び第2導電型のMISFETを有する第2領域における半導体基板1上に、ゲート絶縁膜3を形成する工程と、前記第1領域における前記ゲート絶縁膜上に、第1金属材料層4を形成する工程と、前記第1領域における前記第1金属材料層上及び前記第2領域における前記ゲート絶縁膜上に、第2金属材料層7からなる第2ゲート電極7a及び7bをそれぞれ形成する工程と、前記第1領域及び前記第2領域における前記第2ゲート電極の側面に、第1側壁絶縁膜11a及び11bをそれぞれ形成する工程と、前記第1側壁絶縁膜をマスクとして、前記第1領域における前記第1金属材料層を加工して第1ゲート電極4aを形成する工程と、を具備する。

(もっと読む)

半導体装置の製造方法

【課題】nMOSFETのソース/ドレイン領域にはSiGeを埋め込まず、pMOSFETのソース/ドレイン領域にのみSiGeを再現性よく埋め込むことが可能な製造方法を提供する。

【解決手段】第1活性領域12と交差する第1ゲート電極21、及び第2活性領域13と交差する第2ゲート電極22を形成し、第1及び第2ゲート電極を覆うように、第1キャップ膜35を形成する。第1活性領域上の第1キャップ膜35を、エッチングして除去する。半導体基板全面に、第2キャップ膜を形成37する。第2活性領域上の第2キャップ膜37を第2マスクパターンで覆い、第1活性領域上の第2キャップ膜37をエッチングして除去する。第2活性領域を第1及び第2キャップ膜で覆った状態で、第1活性領域において、ソース/ドレイン領域をエッチングすることにより、凹部を形成する。凹部内を、埋込部材で埋め込む。

(もっと読む)

半導体素子及びその製造方法

【課題】ソース・ドレイン電極及び/又はゲート電極の低抵抗化を図り、微細化・高集積化を損なうことなく、低消費電力で高速操作可能な半導体素子を提供する。

【解決手段】素子分離領域102によりシリコン基板101A表層に画成された素子領域に、チャネル領域を隔てて形成された一対のソース・ドレイン領域106と、ソース・ドレイン領域のそれぞれに導通するソース・ドレイン電極と、チャネル領域上にゲート絶縁膜103を介して形成されたゲート電極と、を備えた半導体素子において、ソース・ドレイン電極及び/又はゲート電極を、ソース・ドレイン領域表面又はゲートを構成するポリシリコン層表面に形成した第1金属膜がシリサイド化されてなるシリサイド層107bと、このシリサイド層上に無電解メッキ法により形成された第2金属膜108と、で構成する。

(もっと読む)

半導体装置の製造方法

【課題】実効酸化膜厚の極めて薄いゲート絶縁膜を有し、且つ、消費電力の少ない半導体装置を、高い歩留まりで製造することができる半導体装置の製造方法をする。

【解決手段】液体の酸化剤を用いてシリコン基板1の表面を雰囲気に露出させることなく酸化することにより、シリコン基板1の表面にシリコン酸化膜6を形成し、

シリコン酸化膜6の上にアルミニウム酸化膜7を形成し、

アルミニウム酸化膜7の上にランタン酸化膜8を形成し、

ランタン酸化膜8の上にハフニウムシリケイト膜9Aを形成し、

その後、窒素を導入して熱処理を行うことにより、ハフニウムシリケイト膜9Aを窒化させて窒化ハフニウムシリケイト膜9を形成し、

前記熱処理により、シリコン酸化膜6ないしランタン酸化膜8を、ランタンアルミニウムシリケイトとする。

(もっと読む)

半導体装置およびその作製方法

【課題】酸化物半導体層を用い、電気特性及び信頼性の優れた薄膜トランジスタを備えた半導体装置を提供することを課題の一つとする。

【解決手段】絶縁物(絶縁性酸化物、絶縁性窒化物、若しくは酸窒化シリコン、酸窒化アルミニウムなど)、代表的にはSiO2を含む酸化物半導体ターゲットを用いて成膜を行い、酸化物半導体層の膜厚方向におけるSi元素濃度が、ゲート電極に近い側からゲート電極に遠い側に増加する濃度勾配を有する半導体装置を実現する。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】デュアルゲート電極構造のMOSトランジスタにおいて、閾値電圧シフト及びばらつきを抑えることができる半導体装置及びその製造方法を提供すること。

【解決手段】半導体基板上にP型MOSトランジスタ及びN型MOSトランジスタを備える半導体装置において、P型MOSトランジスタ及びN型MOSトランジスタは、それぞれチャネル極性と同極のポリゲート電極を備えたデュアルゲート構造のMOSトランジスタであって、デュアルゲート型MOSトランジスタのポリゲート電極が、ゲルマニウムからなる第1のポリゲート電極層と、ゲルマニウムとシリコンとが混在した第2のポリゲート電極層と、シリコンからなる第3のポリゲート電極層と、を順次備えた積層構造を有している。

(もっと読む)

半導体装置

【課題】ソース・ドレイン領域のエクステンション領域の不純物濃度プロファイルが急峻なp型トランジスタを有する半導体装置を提供する。

【解決手段】本発明の一態様に係る半導体装置1aは、半導体基板2上に形成された結晶層13と、結晶層13上にゲート絶縁膜14を介して形成されたゲート電極15と、半導体基板2と結晶層13との間に形成された、ゲート電極15の下方の領域において第1の不純物を含むC含有Si系結晶からなる不純物拡散抑制層12と、半導体基板2、不純物拡散抑制層12、および結晶層13内のゲート電極15の両側に形成され、結晶層13内にエクステンション領域を有する、p導電型を有する第2の不純物を含むp型ソース・ドレイン領域17と、を有し、C含有Si系結晶は第2の不純物の拡散を抑制する機能を有し、第1の不純物は、C含有Si系結晶内の固定電荷の発生を抑制する機能を有する。

(もっと読む)

スレッショルド調節半導体合金を堆積させるのに先立ちパターニング不均一性を低減することによる前記半導体合金の厚みばらつきの低減

【解決手段】

シリコン/ゲルマニウム合金のようなスレッショルド調節半導体合金を堆積させるための選択的エピタキシャル成長プロセスにおける成長速度は、選択的エピタキシャル成長プロセスを実行するのに先立ちプラズマ支援エッチングプロセスを実行することによって、高められ得る。例えば、プラズマ支援エッチンプロセスに基いてマスク層がパターニングされてよく、それにより後続の成長プロセスの間に優れたデバイストポグラフィを同時にもたらすことができる。従って、スレッショルド調節材質を高い厚み均一性で堆積させることができ、全体的なスレッショルドばらつきを低減することができる。

(もっと読む)

半導体装置の製造方法及び半導体装置

【課題】n型MOSトランジスタ、p型MOSトランジスタにおいて共通のゲート絶縁膜構造及びゲート電極材料を用いながら、各々のトランジスタのしきい値電圧を適正な値へ設定し、且つゲート絶縁膜における酸素欠損に伴う移動度の低下を抑制する。

【解決手段】メタルゲート電極及び高誘電率ゲート絶縁膜を用いた半導体装置の製造方法であって、n型半導体領域200及びp型半導体領域300上にそれぞれ、シリコン酸化物からなる第1のゲート絶縁膜、La,Al,Oを含む第2のゲート絶縁膜、Hfを含む第3のゲート絶縁膜を積層し、その上に金属膜からなるゲート電極を形成し、次いでp型半導体領域300上の、第1のゲート絶縁膜,第2のゲート絶縁膜,第3のゲート絶縁膜,及びゲート電極の積層構造を、水素拡散防止膜350で被覆した後、水素雰囲気で熱処理を施す。

(もっと読む)

半導体装置及びその製造方法

【課題】メタルゲート電極を有するMIS型トランジスタと高抵抗素子とを容易に集積化でき、製造工程数の増加と歩留まりの低下を抑制できる半導体装置及びその製造方法を提供する。

【解決手段】基板100の素子領域にシリコン膜118と金属膜103の積層構造からなるMIS型トランジスタのゲート電極、及び素子分離領域上に前記シリコン膜と前記金属膜の積層構造からなる高抵抗素子を形成する。そして、前記ゲート電極の側壁に耐酸化性の絶縁膜110を形成し、前記高抵抗素子の前記金属膜103を酸化する。

(もっと読む)

半導体装置及びその作製方法

【課題】大型の半導体装置で、高速に動作する半導体装置を提供することを目的する。

【解決手段】単結晶の半導体層を有するトップゲート型のトランジスタと、アモルファス

シリコン(またはマイクロクリスタルシリコン)の半導体層を有するボトムゲート型のト

ランジスタとを同一基板に形成する。そして、各々のトランジスタが有するゲート電極を

同じレイヤーで形成し、ソース及びドレイン電極も同じレイヤーで形成する。このように

して、製造工程を削減する。つまり、ボトムゲート型のトランジスタの製造工程に、少し

だけ工程を追加するだけで、2つのタイプのトランジスタを製造することが出来る。

(もっと読む)

半導体装置及びその製造方法

【課題】 ゲート絶縁膜とゲート電極の間の領域に導入するハフニウムを、pMOSFE

TとnMOSFETで、適した面密度とすることで、CMOSFETの性能向上を図る。

【解決手段】

シリコン基板2上にpMOSFET10とnMOSFET30を備えるCMOSFET

1において、pMOSFET10は、シリコン基板2上に形成されたゲート絶縁膜12と

、ゲート絶縁膜12上に形成されたハフニウム層14と、ハフニウム層14上に形成され

たゲート電極13とを備える。nMOSFET30は、シリコン基板2上に形成されたゲ

ート絶縁膜32と、ゲート絶縁膜32上に形成されたハフニウム層34と、ハフニウム層

34上に形成されたゲート電極33とを備える。ハフニウム層34の面密度は、ハフニウ

ム層14の面密度より低い。

(もっと読む)

半導体装置およびその製造方法

【課題】キャップ膜としてのランタン酸化膜の膜厚の増加を抑えつつ、閾値電圧の低減化を図れる、窒化チタン膜を含むメタルゲート電極/Hfを含有するゲート絶縁膜のゲートスタック構造を有するMOSFETを備えた半導体装置を適用すること。

【解決手段】P型半導体領域105を含む半導体基板101と、P型半導体領域101に形成されたNチャネルMOSFETとを具備してなり、前記NチャネルMOSトランジスタは、半導体基板101上に形成され、ハフニウムを含有するゲート絶縁膜108と、ゲート絶縁膜109上に形成され、膜厚が所定値以下のランタン酸化膜109と、ランタン酸化膜109上に形成され、N/Ti原子数比が1未満の窒化チタン膜110を含むゲート電極とを具備してなることを特徴とする。

(もっと読む)

半導体装置及びその製造方法

【課題】炭素含有シリコン領域を有するn型MISトランジスタを備えた半導体装置において、チャネル領域のゲート長方向に印加される引っ張り応力の大きさを、効果的に増大させる。

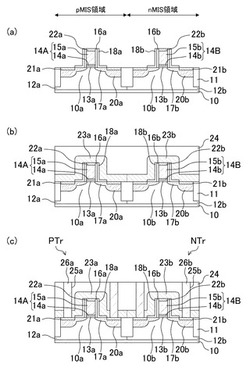

【解決手段】少なくともn型MISトランジスタNTrを有する半導体装置において、n型MISトランジスタnTrは、半導体基板10における第1の半導体領域10a上に形成された第1のゲート絶縁膜13aと、第1のゲート絶縁膜13a上に形成された第1のゲート電極14aと、第1のゲート電極14aの側面上に形成された第1のサイドウォール18Aと、第1のサイドウォール18Aの外側方に形成された炭素含有シリコン領域27とを備え、炭素含有シリコン領域27の上面高さは、第1の半導体領域10aにおける第1のゲート絶縁膜13aの下に位置する領域の上面高さよりも高い。

(もっと読む)

161 - 180 / 480

[ Back to top ]