Fターム[5F048BB13]の内容

MOSIC、バイポーラ・MOSIC (97,815) | ゲート (19,021) | 多層(2層)ゲート (2,461) | 3層以上 (480)

Fターム[5F048BB13]に分類される特許

1 - 20 / 480

半導体装置及びその製造方法

半導体装置及びその製造方法

【課題】所望の領域に容易に第1の膜を形成して半導体装置の不良を低減する。また、スループットが向上して、製造コストの低減を図る。

【解決手段】半導体装置の製造方法では、半導体基板の第1及び第2の領域上に第1の膜を形成した後、第1の膜上にフォトレジストパターンを形成する。フォトレジストパターンをマスクに用いた第1の膜のエッチングにより、第2の領域上の第1の膜を除去すると共に第2の領域上を覆うように被覆膜を形成する。半導体基板に熱処理を行うことにより、被覆膜を除去すると共にフォトレジストパターンに焼き締め処理を行う。この後、フォトレジストパターンを除去する。

(もっと読む)

半導体装置

【課題】作製工程が簡略化され、容量素子の面積が縮小化された昇圧回路を有する半導体

装置を提供することを課題とする。

【解決手段】直列に接続され、第1の入力端子部から出力端子部へ整流作用を示す複数の

整流素子と、第2の入力端子部に接続され、互いに反転する信号が入力される第1の配線

及び第2の配線と、それぞれ第1の電極、絶縁膜及び第2の電極を有し、昇圧された電位

を保持する複数の容量素子とから構成される昇圧回路を有し、複数の容量素子は、第1の

電極及び第2の電極が導電膜で設けられた容量素子と、少なくとも第2の電極が半導体膜

で設けられた容量素子とを有し、複数の容量素子において少なくとも1段目の容量素子を

第1の電極及び第2の電極が導電膜で設けられた容量素子とする。

(もっと読む)

半導体装置及びその製造方法

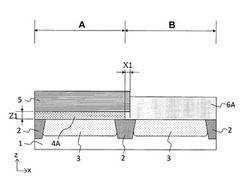

【課題】個別の工程で形成されることで分離して配置された電極どうしを断線することなく接続できる半導体装置及びその製造方法を提供する。

【解決手段】半導体基板の主面に第1の絶縁膜を介して形成された第1の電極と、半導体基板の主面に第2の絶縁膜を介して形成された第2の電極との間に補償膜を埋設する。第1の電極及び第2の電極上には、第1の電極の上面及び第2の電極の上面と接触する、第1の電極の上面から補償膜の上面を経由して第2の電極の上面まで到達する配線を形成する。

(もっと読む)

半導体装置

【課題】半導体素子が有する寄生容量や寄生インダクタンスによる電力の損失を抑えるこ

とが出来る、整流回路の提供を課題とする。

【解決手段】入力された交流電圧の振幅に従い、前段の回路と該整流回路の間におけるイ

ンピーダンスを整合または不整合にする。入力される交流電圧が規定の振幅以下である場

合は、インピーダンスを整合にし、該交流電圧をそのまま整流回路に印加する。逆に入力

される交流電圧が規定の振幅よりも大きい場合は、インピーダンスを不整合にし、反射に

より該交流電圧の振幅を小さくしてから整流回路に印加する。

(もっと読む)

半導体装置の製造方法

【課題】半導体装置の信頼性を向上させることができる技術を提供する。特に、ゲート電極をメタル材料で構成する電界効果トランジスタを有する半導体装置において、安定した動作特性を得ることのできる技術を提供する。

【解決手段】レジストパターン12をマスクとしたドライエッチングにより、ゲート電極13nまたはゲート電極13pを形成した後、酸素および水素を含むプラズマ雰囲気中においてアッシング処理を施すことにより、レジストパターン12を除去し、ゲート電極13nまたはゲート電極13pの側面に付着した反応生成物14を酸化する。その後、洗浄処理を施して、反応生成物14を除去する。

(もっと読む)

半導体装置

【課題】安定した電気特性を有する薄膜トランジスタを有する電位保持機能の高い固体撮

像素子を提供する。

【解決手段】酸化物半導体層を用いて薄膜トランジスタのオフ電流を1×10−13A以

下とし、該薄膜トランジスタを固体撮像素子のリセットトランジスタ及び転送トランジス

タの両方に用いることで信号電荷蓄積部の電位が一定に保たれ、ダイナミックレンジを向

上させることができる。また、周辺回路に相補型金属酸化物半導体素子が作製可能なシリ

コン半導体を用いることで高速かつ低消費電力の半導体装置を作製することができる。

(もっと読む)

半導体装置

【課題】配線間の寄生容量を削減可能にした半導体装置を提供する。

【解決手段】X方向に配列する複数のトランジスタについて、夫々が、対応するダミーゲートDG1,DG2を挟む複数のソース拡散層S1,S2に接続する第2及び第3の金属配線M12,M13は、2つのS1,2つのS2に夫々接続する複数の第1のビアV1の両方を含む第1の幅L1と、V1を含まず、L1よりも短い第2の幅L2と、を有する。ドレイン拡散層D1に接続する第1の金属配線M11と、M12との間、並びにM11及びM13の間の夫々は、L1に対応する第1のギャップSP1と、L2に対応する、L1よりも大きな第2のギャップSP2と、を有する。好ましくは、M11〜M13の夫々と第2のビアV2を介して接続される第4〜第6の金属配線M24〜M26の夫々は、L1よりも短い第3の幅L3を有する。

(もっと読む)

半導体装置の製造方法

【課題】所定の安定した特性を有するN−MISFETとP−MISFETとを備えた半導体装置を容易に実現できるようにする。

【解決手段】半導体装置の製造方法は、半導体基板101の上に高誘電体膜121と、第1の膜122と、犠牲導電膜123と、第2の膜124とを順次形成した後、第2の膜124におけるN−MISFET形成領域101Nに形成された部分を第1の薬液を用いて選択的に除去する。この後、第2の膜124に含まれる第2の金属元素を犠牲導電膜124におけるP−MISFET形成領域101Pに形成された部分に拡散させる。続いて、犠牲導電膜124及び第1の膜122におけるN−MISFET形成領域101Nに形成された部分を、それぞれ第2の薬液及び第3の薬液を用いて選択的に除去する。第3の膜125を形成した後、第3の膜125に含まれる第3の金属元素を高誘電体膜121中に拡散させる。

(もっと読む)

半導体装置

【課題】微細化しても高いオン電流を得ることができるトランジスタを用いた、半導体装置。

【解決手段】トランジスタが、絶縁表面上の一対の第1導電膜と、一対の第1導電膜上の半導体膜と、一対の第1導電膜にそれぞれ接続されている一対の第2導電膜と、半導体膜上の絶縁膜と、絶縁膜上において、半導体膜と重なる位置に設けられた第3導電膜とを有する。また、半導体膜上における第3導電膜の端部と、一対の第2導電膜が設けられた領域とは、離隔している。

(もっと読む)

半導体装置及びその製造方法

【課題】ゲート電極膜に注入したイオンがチャネル領域に達してMISFETの電気特性に影響を与えていた。

【解決手段】半導体基板の主面上にゲート絶縁膜を介して形成されるとともに、第1導電型となる不純物を含んだシリコンを主体とする第1ゲート電極膜と、前記第1ゲート電極膜上に形成されるとともに、酸素及び窒素のうち一方又は両方を含んだシリコンを主体とする介在層と、前記第1ゲート電極膜上に前記介在層を介して形成されるとともに、前記第1導電型となる不純物を含んだシリコンを主体とする第2ゲート電極膜と、を含む電界効果トランジスタを有する。

(もっと読む)

半導体装置およびその製造方法

【課題】半導体基板に形成されたプレーナ型トランジスタと3次元トランジスタを含む半導体装置の形成プロセスを簡略化できるようにする。

【解決手段】半導体基板に形成されたプレーナ型トランジスタと3次元トランジスタを含む半導体装置であり、前記プレーナ型トランジスタ、前記3次元トランジスタはともに高誘電率材料によるゲート絶縁膜を有し、前記プレーナ型トランジスタは、前記ゲート絶縁膜上に、下側が第1のメタル材料(A)、上側が第2のメタル材料(B)からなるゲート電極を有し、前記3次元トランジスタは埋め込みゲート電極を有し、該埋め込みゲート電極の下側のほうに前記第1のメタル材料(A)と同一の材料が、該埋め込みゲート電極の上側のほうに前記第2のメタル材料(B)と同一の材料がそれぞれ使用されている。

(もっと読む)

半導体装置

【課題】残渣による配線間のショートの発生を防ぐ。

【解決手段】本発明の半導体装置は、高誘電率材料を含む第1のゲート絶縁膜4と第1のゲート絶縁膜4上に形成された第1のメタルゲート電極5とを備える第1のトランジスタが形成される半導体基板上の第1の領域と、高誘電率材料を含む第2のゲート絶縁膜4と第2のゲート絶縁膜上に形成された第2のメタルゲート電極12とを備え、第1のトランジスタとは閾値電圧の異なる第2のトランジスタが形成される半導体基板上の第1の領域に並ぶ第2の領域と、電位の異なる第1および第2の配線と、を有し、第1の領域と第2の領域との境界が、第1および第2の配線の少なくとも一方としか重ならない。

(もっと読む)

半導体装置

【課題】異なる特性の半導体素子を一体に有しつつ、高集積化が実現可能な、新たな構成の半導体装置を提供することを目的の一とする。

【解決手段】第1の半導体材料が用いられた第1のチャネル形成領域と、第1のゲート電極と、を含む第1のトランジスタと、第1のゲート電極と一体に設けられた第2のソース電極および第2のドレイン電極の一方と、第2の半導体材料が用いられ、第2のソース電極および第2のドレイン電極と電気的に接続された第2のチャネル形成領域と、を含む第2のトランジスタと、を備えた半導体装置である。

(もっと読む)

半導体装置及びその製造方法

【課題】higher-k材料であるチタン酸化膜の半導体基板との界面を安定化でき、さらなる微細化に対応できるゲート構造を実現できるようにする。

【解決手段】半導体装置は、半導体基板1の上に形成されたゲート絶縁膜と、該ゲート絶縁膜の上に形成されたゲート電極とを備えている。ゲート絶縁膜は、アナターゼ型酸化チタンを主成分とする高誘電率絶縁膜5であり、ゲート電極は、第1の金属膜6又は第2の金属膜8を含む導電膜から構成されている。

(もっと読む)

半導体装置及びその製造方法

【課題】多結晶シリコン膜との接触に起因するショットキー抵抗を低減する。

【解決手段】半導体装置は、トランジスタを備える。トランジスタは、第1の活性領域の表面の一部を覆い二酸化シリコンよりも高い誘電率を有する第1の絶縁材料からなる第1のゲート絶縁膜と、第1のゲート絶縁膜上に形成された第1の金属材料からなる第1の金属ゲート電極と、第1の金属ゲート電極上に形成されたp型導電型の第1の多結晶シリコン膜を有する。

(もっと読む)

半導体装置とその製造方法

【課題】 チャンネルドーピングあるいは複雑なゲート電極パターン化の必要性なしに、複数のトランジスタが多閾値電圧を有する半導体装置を提供する。

【解決手段】 半導体装置及びその製造方法において、第1トランジスタは、第1材料で形成された下層と第2材料で形成された上層とを含むゲートスタックを有する。第2トランジスタは、第3材料で形成された下層と第2材料で形成された上層とを含むゲートスタックを有する。第3トランジスタは、第1材料で形成された下層と第4材料で形成された上層とを含むゲートスタックを有する。第4トランジスタは、第3材料で形成された下層と第4材料で形成された上層とを含むゲートスタックを有する。第1材料乃至前記第4材料の仕事関数は互いに異なる。第1トランジスタ乃至第4トランジスタは、互いに異なる閾値電圧を有する。

(もっと読む)

半導体装置

【課題】高速動作が可能であり、且つ消費電力の低減が可能な半導体装置を提供する。

【解決手段】酸化物半導体を有するトランジスタを備える半導体装置において、ゲート電圧が負のときの電流が小さいトランジスタの酸化物半導体膜と、電界効果移動度が高くオン電流が大きいトランジスタの酸化物半導体膜において、酸素濃度が異なる。代表的には、ゲート電圧が負のときの電流が小さいトランジスタの酸化物半導体膜と比較して、電界効果移動度が高くオン電流が大きいトランジスタの酸化物半導体膜の酸素濃度が低い。

(もっと読む)

低ノイズ及び高性能のLSI素子、レイアウト及びその製造方法

【課題】低ノイズ及び高性能のLSI素子、レイアウト及びその製造方法を提供する。

【解決手段】NMOS素子及びPMOS素子が何れもアナログ及びデジタルモードのような相異なるモードで動作される半導体素子において、これら素子の要求される動作モードによって特定素子にストレスエンジニアリングを選択的に適用する。フォトレジスト160をデジタル回路領域のPMOSトランジスタのみを覆うように形成し、Ge、Siなどのイオン162をストレスコントロール膜150に注入する。デジタル回路領域のPMOSトランジスタを除くあらゆる領域でストレスコントロール膜150はストレス解除膜またはストレス緩和膜152に変換され、デジタル回路領域のPMOSトランジスタのチャネル104bだけに圧縮応力が印加される状態が残る。

(もっと読む)

半導体装置及びその製造方法

【課題】ゲートラストプロセスの工程数を削減しつつ、所望の信頼性及び特性が得られるメタルゲート電極を備えたMISFETを実現できるようにする。

【解決手段】各ゲート溝の少なくとも底面上にゲート絶縁膜112及び保護膜113が順次形成されている。一方のゲート溝内の保護膜113の上には第1の金属含有膜114a及び第2の金属含有膜114bが順次形成されており、他方のゲート溝内の保護膜113の上には第2の金属含有膜114bが形成されている。一方のゲート溝内の保護膜113の厚さと比べて、他方のゲート溝内の保護膜113の厚さは薄い。

(もっと読む)

1 - 20 / 480

[ Back to top ]