Fターム[5F048BB15]の内容

MOSIC、バイポーラ・MOSIC (97,815) | ゲート (19,021) | 閾値制御 (2,521) | 閾値電圧が異なる複数MOS (1,778)

Fターム[5F048BB15]の下位に属するFターム

絶縁膜厚が異なるもの (781)

絶縁材料が異なるもの (340)

注入量、注入物質が異なるもの (323)

Fターム[5F048BB15]に分類される特許

1 - 20 / 334

半導体装置及びその製造方法

半導体装置の製造方法

半導体集積回路装置および半導体集積回路装置の製造方法

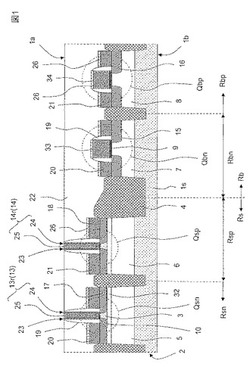

【課題】ハイブリッド基板構造を有する半導体集積回路装置においては、SOI−MISFETとバルク−MISFETの混在する結果、ゲートファースト方式で両方のMISFETを作製した場合、それぞれでゲート材料に合った構造設計が必要である。バルク−MISFETはこれまでに多くの知見があり、ゲート材料変更に伴う構造変更は開発コストの増大を招くことになるため、可能な限りバルク−MISFETの構造を維持したい。また従来のゲートラスト方式でゲート電極材料の変更を行う場合は、プロセスの複雑化や製造コスト増大などの問題を招く恐れがある。

【解決手段】本願発明は、半導体基板のデバイス面上にSOI構造とバルク構造が混在するハイブリッド基板構造を有する半導体集積回路装置において、前記デバイス面を基準とするSOI型MISFETのゲート電極の高さを、バルク型MISFETのゲート電極の高さよりも高くしたものである。

(もっと読む)

半導体装置の作製方法

【課題】半導体装置の製造コストを低減することを課題の一とする。半導体装置の開口率

を向上することを課題の一とする。半導体装置の表示部を高精細化することを課題の一と

する。高速駆動が可能な半導体装置を提供することを課題の一とする。

【解決手段】同一基板上に駆動回路部と表示部とを有し、当該駆動回路部は、ソース電極

及びドレイン電極が金属によって構成され、且つチャネル層が酸化物半導体によって構成

された駆動回路用TFTと、金属によって構成された駆動回路用配線とを有すればよい。

また、当該表示部はソース電極及びドレイン電極が酸化物導電体によって構成され、且つ

半導体層が酸化物半導体によって構成された画素用TFTと、酸化物導電体によって構成

された表示部用配線とを有すればよい。

(もっと読む)

半導体装置の製造方法

【課題】閾値電圧ばらつきを改善した半導体装置の製造方法を提供する。

【解決手段】SOI基板を用いた半導体装置の製造方法において、活性層基板を酸化して埋め込み酸化膜4bを生成する工程と、支持基板3表面に、MOSトランジスタ1の閾値電圧を決定するためのチャネルドープ10を行う工程と、支持基板3と活性層基板5とを前記埋め込み酸化膜を介して貼り合せる工程と、活性層基板を部分的に除去し埋め込み酸化膜4aを露出させる工程と、埋め込み酸化膜4a上にゲート電極6aを形成する工程と、を含む半導体装置の製造方法とする。

(もっと読む)

半導体装置およびその製造方法

【課題】半導体基板に形成されたプレーナ型トランジスタと3次元トランジスタを含む半導体装置の形成プロセスを簡略化できるようにする。

【解決手段】半導体基板に形成されたプレーナ型トランジスタと3次元トランジスタを含む半導体装置であり、前記プレーナ型トランジスタ、前記3次元トランジスタはともに高誘電率材料によるゲート絶縁膜を有し、前記プレーナ型トランジスタは、前記ゲート絶縁膜上に、下側が第1のメタル材料(A)、上側が第2のメタル材料(B)からなるゲート電極を有し、前記3次元トランジスタは埋め込みゲート電極を有し、該埋め込みゲート電極の下側のほうに前記第1のメタル材料(A)と同一の材料が、該埋め込みゲート電極の上側のほうに前記第2のメタル材料(B)と同一の材料がそれぞれ使用されている。

(もっと読む)

半導体装置及びその製造方法

【課題】多結晶シリコン膜との接触に起因するショットキー抵抗を低減する。

【解決手段】半導体装置は、トランジスタを備える。トランジスタは、第1の活性領域の表面の一部を覆い二酸化シリコンよりも高い誘電率を有する第1の絶縁材料からなる第1のゲート絶縁膜と、第1のゲート絶縁膜上に形成された第1の金属材料からなる第1の金属ゲート電極と、第1の金属ゲート電極上に形成されたp型導電型の第1の多結晶シリコン膜を有する。

(もっと読む)

半導体装置とその製造方法

【課題】 チャンネルドーピングあるいは複雑なゲート電極パターン化の必要性なしに、複数のトランジスタが多閾値電圧を有する半導体装置を提供する。

【解決手段】 半導体装置及びその製造方法において、第1トランジスタは、第1材料で形成された下層と第2材料で形成された上層とを含むゲートスタックを有する。第2トランジスタは、第3材料で形成された下層と第2材料で形成された上層とを含むゲートスタックを有する。第3トランジスタは、第1材料で形成された下層と第4材料で形成された上層とを含むゲートスタックを有する。第4トランジスタは、第3材料で形成された下層と第4材料で形成された上層とを含むゲートスタックを有する。第1材料乃至前記第4材料の仕事関数は互いに異なる。第1トランジスタ乃至第4トランジスタは、互いに異なる閾値電圧を有する。

(もっと読む)

半導体装置

【課題】高速動作が可能であり、且つ消費電力の低減が可能な半導体装置を提供する。

【解決手段】酸化物半導体を有するトランジスタを備える半導体装置において、ゲート電圧が負のときの電流が小さいトランジスタの酸化物半導体膜と、電界効果移動度が高くオン電流が大きいトランジスタの酸化物半導体膜において、酸素濃度が異なる。代表的には、ゲート電圧が負のときの電流が小さいトランジスタの酸化物半導体膜と比較して、電界効果移動度が高くオン電流が大きいトランジスタの酸化物半導体膜の酸素濃度が低い。

(もっと読む)

半導体装置の作製方法

【課題】複数のトランジスタが高集積化された素子の少なくとも一のトランジスタに、作製工程数を増加させることなくバックゲートを設ける半導体装置を提供する。

【解決手段】複数のトランジスタが上下に積層されて設けられた素子において、少なくとも上部のトランジスタ102は、半導体特性を示す金属酸化物により設けられ、下部のトランジスタ100が有するゲート電極層を上部のトランジスタのチャネル形成領域と重畳するように配して、ゲート電極層と同一の層の一部を上部のトランジスタ102のバックゲートBGとして機能させる。下部のトランジスタ100は、絶縁層で覆われた状態で平坦化処理が施され、ゲート電極が露出され、上部のトランジスタ102のソース電極及びドレイン電極となる層に接続されている。

(もっと読む)

集積回路における選択されたトランジスタの性能向上のための注入

【課題】マスクセットのすべてまたはいくつかを交換することなく、トランジスタ特性をより所望の特性に変更することを可能にすること。

【解決手段】第1注入が基板に実行されて、複数のトランジスタが形成されるウェルが形成される。形成される複数のトランジスタの第1サブセットの各トランジスタが所定幅制限を満たす幅を有し、第2サブセットのトランジスタの各々が所定幅制限を満たさない幅を有する。第2注入は,第2サブセットのトランジスタが形成されるウェルの領域ではなく、第1サブセットのトランジスタが形成されるウェルの領域において実行される。トランジスタが形成され、第1サブセットのトランジスタの各々のチャネル領域は、第2注入を受け入れた基板の一部分に形成され、第2サブセットのトランジスタの各々のチャネル領域は、第2注入を受け入れなかった基板の一部分に形成される。

(もっと読む)

ネスト化複合スイッチ

【課題】高いスイッチング速度及び低いオン状態抵抗を有し、電圧降伏耐性を強化したネスト化複合スイッチを提供する。

【解決手段】ネスト化複合スイッチ240は、複合スイッチに結合されたノーマリオン・プライマリ・トランジスタを含む。複合スイッチは、中間型トランジスタ222とカスコード接続された低電圧(LV)トランジスタ224を含み、中間型トランジスタは、LVトランジスタよりは大きく、ノーマリオン・プライマリ・トランジスタよりは小さい降伏電圧を有する。1つの実現では、ノーマリオン・プライマリ・トランジスタはIII-V族トランジスタとすることができ、LVトランジスタはIV族LVトランジスタとすることができる。

(もっと読む)

半導体集積回路

【課題】SOI型の半導体集積回路において電源遮断時の低消費電力及び電源供給時の動作性能向上に資することができる電源遮断制御を可能にする。

【解決手段】本発明に係る半導体集積回路は、第1電源スイッチと、前記第1電源スイッチに直列接続される論理回路を有する。前記論理回路は、順序回路(FF1,FF2)及び組み合わせ回路(LOG1,LOG2)を含み、前記第1電源スイッチと前記組み合わせ回路との間に第2電源スイッチが接続される。第1モードにおいて前記第1電源スイッチをオフ状態に制御し、前記順序回路及び前記組み合わせ回路を非通電状態にし、第2モードにおいて前記第1電源スイッチをオン状態に維持し且つ前記第2電源スイッチをオフ状態に制御し、前記順序回路を通電状態、前記組み合わせ回路を非通電状態にする電源スイッチ制御回路を有する。

(もっと読む)

半導体装置

【課題】表示装置の高精細化に伴い、画素数が増加し、ゲート線数、及び信号線数が増加

する。ゲート線数、及び信号線数が増加すると、それらを駆動するための駆動回路を有す

るICチップをボンディング等により実装することが困難となり、製造コストが増大する

という問題がある。

【解決手段】同一基板上に画素部と、画素部を駆動する駆動回路とを有し、駆動回路の少

なくとも一部の回路を、酸化物半導体を用いた逆スタガ型薄膜トランジスタで構成する。

同一基板上に画素部に加え、駆動回路を設けることによって製造コストを低減する。

(もっと読む)

記憶装置及び信号処理回路

【課題】電源の供給を停止しても、記憶している論理状態が消えない記憶装置を提供する。また、該記憶装置を用いることで、電源供給停止により消費電力を抑えることができる信号処理回路を提供する。

【解決手段】第1乃至第4のノードを有する論理回路と、第1のノード、第2のノード、及び第3のノードと接続された第1の制御回路と、第1のノード、第2のノード、及び第4のノードと接続された第2の制御回路と、第1のノード、第1の制御回路、及び第2の制御回路に接続された第1の記憶回路と、第2のノード、第1の制御回路、及び第2の制御回路に接続された第2の記憶回路と、を有する記憶装置である。

(もっと読む)

記憶装置及び信号処理回路

【課題】電源の供給を停止しても、記憶している論理状態が消えない記憶装置を提供する。また、該記憶装置を用いることで、電源供給停止により消費電力を抑えることができる信号処理回路を提供する。

【解決手段】第1及び第2のノードを有する論理回路と、第1のノードに接続された第1の記憶回路と、第2のノードに接続された第2の記憶回路と、第1のノード、第2のノード、第1の記憶回路、及び第2の記憶回路に接続されたプリチャージ回路と、を有し、読み出しの際に、プリチャージ回路は、プリチャージ電位を第1のノード及び第2のノードに出力し、第1の記憶回路及び第2の記憶回路は、チャネルが酸化物半導体膜に形成されるトランジスタを含む記憶装置である。

(もっと読む)

半導体装置及びその製造方法

【課題】素子分離領域を縮小化しつつ、第1のMISトランジスタの閾値電圧を、第2のMISトランジスタの閾値電圧に比べて低くする。

【解決手段】半導体装置は、第1のMISトランジスタTrlと第2のMISトランジスタTrhとを備えている。第1のMISトランジスタTrlは、第1の活性領域1aにおける第1導電型の第1のエクステンション領域8Aの下に形成された第2導電型の第1のポケット領域9Aと、第1の活性領域1aにおける第1のポケット領域9Aの下に形成された拡散抑制不純物を含む第1の拡散抑制領域7Aとを備えている。第2のMISトランジスタTrhは、第2の活性領域に1bおける第1導電型の第2のエクステンション領域8Bの下に形成された第2導電型の第2のポケット領域9Bとを備えている。第1のポケット領域9Aの拡散深さは、第2のポケット領域9Bの拡散深さに比べて浅い。

(もっと読む)

半導体装置

【課題】待機電力を十分に低減した新たな半導体装置を提供することを目的の一とする。

【解決手段】第1の電源端子と、第2の電源端子と、酸化物半導体材料を用いたスイッチ

ングトランジスタと、集積回路と、を有し、前記第1の電源端子と、前記スイッチングト

ランジスタのソース端子またはドレイン端子の一方は電気的に接続し、前記スイッチング

トランジスタのソース端子またはドレイン端子の他方と、前記集積回路の端子の一は電気

的に接続し、前記集積回路の端子の他の一と、前記第2の電源端子は電気的に接続した半

導体装置である。

(もっと読む)

半導体装置及びその製造方法

【課題】下地絶縁膜の膜厚精度の向上とトランジスタ特性の変動抑制との両立が図られたMISトランジスタを備えた半導体装置、及びその製造方法を提供する。

【解決手段】半導体装置は、半導体基板100における活性領域103a上に形成されたゲート絶縁膜108aと、ゲート絶縁膜108a上に形成されたゲート電極111aとを有するMISトランジスタ170を備えている。ゲート絶縁膜108aは、活性領域103a上に形成された板状の下層ゲート絶縁膜210aと、下層ゲート絶縁膜210a上に形成された断面形状が凹状の上層ゲート絶縁膜211aとを有する。下層ゲート絶縁膜210aは、活性領域103a上に形成された下地絶縁膜104aと、第1の高誘電率絶縁膜106aとで構成され、上層ゲート絶縁膜211aは、第1の高誘電率絶縁膜106a上に形成された第2の高誘電率絶縁膜107aで構成される。

(もっと読む)

半導体装置

【課題】抵抗素子を有する半導体装置に関し、集積度を低下することなく低消費電力化と高い回路精度とを実現しうる半導体装置を提供する。

【解決手段】半導体材料により形成された複数の抵抗素子と、複数の抵抗素子の近傍に配置された加熱用抵抗素子と、対向する2つの接続ノード間に加熱用抵抗素子が接続され、対向する他の2つの接続ノード間に電源線が接続された抵抗ブリッジ回路とを有する。

(もっと読む)

1 - 20 / 334

[ Back to top ]