Fターム[5F048BC00]の内容

MOSIC、バイポーラ・MOSIC (97,815) | ソース・ドレイン (8,322)

Fターム[5F048BC00]の下位に属するFターム

形状 (1,394)

非対称構造 (1,107)

追加領域の形成 (3,324)

ソース・ドレイン下に絶縁層 (58)

裏面電極取り出し (325)

材料 (764)

複数MOSの相互のS・D領域が異なるもの (1,340)

Fターム[5F048BC00]に分類される特許

1 - 10 / 10

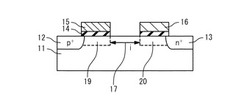

半導体装置及び半導体装置の製造方法

【課題】消費電力が低減された、半導体装置及び半導体装置の製造方法を提供する。

【解決手段】第1電圧が印加される第1導電型領域12と、前記第1導電型領域から離れた位置に設けられ、前記第1導電型とは逆の導電型の第2電圧が印加される第2導電型領域13と、前記第1導電型領域と前記第2導電型領域との間を占めるように配置された、ウェル層11と、オン状態であるときに、前記ウェル層に含まれる第1領域に反転層を形成させる、第1ゲート電極15及び第2領域に反転層を形成させる、第2ゲート電極16とを具備する。前記第1領域と前記第2領域との間の間隔は、前記第1ゲート電極及び前記第2ゲート電極がオン状態である場合に、前記第1電圧と前記第2電圧との差によってインパクトイオン化現象が発生し、前記第1ゲート電極及び前記第2ゲート電極の少なくとも一方がオフ状態である場合に、インパクトイオン化現象が発生しないように設定される。

(もっと読む)

半導体装置および半導体の製造方法。

【課題】Geを含む半導体領域に形成されたソース/ドレイン不純物層を備えるMISFETの、接合リーク電流を低減する半導体装置およびその製造方法を提供する。

【解決手段】半導体基板100中に形成されたチャネル領域104と、チャネル領域104表面に形成されたゲート絶縁膜106と、ゲート絶縁膜106上に形成されたゲート電極108と、チャネル領域104の両側に形成されたソース/ドレイン不純物層112を具備するMISFETを有し、ソース/ドレイン不純物層112の少なくとも一部が、半導体基板100中の、Geを含有する半導体領域に形成され、ソース/ドレイン不純物層112の接合深さよりも深い半導体領域に、S、Se、Teから選択される少なくとも一種の元素が含有されることを特徴とする半導体装置およびその製造方法。

(もっと読む)

半導体装置

【課題】トランジスタのサイズによらない普遍的な引っ張り歪みをnチャネル型MOSトランジスタに印加できる半導体装置を提供する。

【解決手段】nチャネル型MOSトランジスタのゲート絶縁膜として、高誘電率絶縁膜を使用し、この高誘電率絶縁膜を半導体基板上に界面層を介さず直接形成することにより、チャネル領域に引張り歪を与える。チャネル領域に圧縮歪を有するpチャネル型MOSトランジスタと組み合わせることにより、相補型の高性能半導体装置を構成できる。

(もっと読む)

半導体装置およびその製造方法

【課題】半導体装置の微細化が進行しても、素子分離絶縁膜の応力がチャネルに与える影響を抑え、集積回路の設計において半導体特性をパラメタライズすることができる半導体装置を得ること。

【解決手段】半導体基板10上に所定のパターンで形成された素子分離絶縁膜11と、素子分離絶縁膜11で区画される半導体基板10表面の所定の位置に形成されるゲート絶縁膜22,32とゲート電極23,33とを含むゲート構造21,31と、ゲート構造21,31の線幅方向両側の半導体基板10表面に形成されるソース/ドレイン領域25,35と、を備え、ゲート構造21,31と素子分離絶縁膜11との間の半導体基板10表面は、ヤング率が半導体基板10よりも小さい材料からなる。

(もっと読む)

半導体装置の製造方法

【課題】ニッケルシリサイドの耐熱性を向上させることが可能な半導体装置の製造方法を提供する。

【解決手段】ゲート領域2、ソース領域4及びドレイン領域5が形成された半導体基板1上にニッケル(またはニッケル合金)6を形成し(図1(A))、第1アニール工程でダイニッケルシリサイド7を形成し(図1(B))、プラズマ処理工程では水素イオンを含有するプラズマにより、水素イオンをダイニッケルシリサイド7またはダイニッケルシリサイド7の下部のゲート領域2、ソース領域4及びドレイン領域5に注入し、第2アニール工程でダイニッケルシリサイド7をニッケルシリサイド8に相変態させる(図1(C))。

(もっと読む)

半導体装置

【課題】 レベルシフトトランジスタの発熱によって半導体装置が過熱されることを防止できる半導体装置を提供する。

【解決手段】 半導体装置は、低電位回路領域10と高電位回路領域30の双方から絶縁分離されている分離領域20を有している。分離領域20内に形成されている複数個の第1トランジスタTr1は、低電位回路領域10と高電位回路領域30のうちの一方の回路領域から他方の回路領域に伝達する信号であって、ハイとロウの間で変化する信号の立ち上がりタイミングでオンする。分離領域20内に形成されている複数個の第2トランジスタTr2は、上記信号の立ち下がりタイミングでオンする。第1トランジスタTr1と非導通領域と第2トランジスタTr2と非導通領域の順序が繰り返されるパターンで、分離領域20内に複数個の第1トランジスタTr1と複数個の第2トランジスタTr2が配置されている。

(もっと読む)

半導体装置

【課題】短チャネル効果を防止しつつチャネル長の短い微細な半導体装置を実現する。

【解決手段】チャネル形成領域103に対してチャネル方向(電界方向)と平行に線状パターン形状を有する不純物領域104を形成する。この不純物領域104がドレイン側空乏層の広がりを抑え、かつ、狭チャネル効果を起こして短チャネル効果を防止する。また、チャネル形成領域103において、不純物領域104はエネルギー的にキャリアの移動経路を一方向に規定し、キャリア同士の不規則な衝突による散乱を抑制する。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】Finに応力を印加することによってN型MISおよびP型MISの両方のキャリア移動度を向上させることができるFin型FETを提供する。

【解決手段】半導体装置の製造方法は、半導体材料から成る複数のFin11、12を絶縁層10上に形成し、複数のFinの側面にゲート絶縁膜25を形成し、複数のFinのうちN型FETに用いられる第1のFin11の側面を該側面に対して垂直方向から圧縮し、かつ、P型FETに用いられる第2のFin12の側面を該側面に対して垂直方向へ引張するように、ゲート絶縁膜上にゲート電極31、32を形成することを具備する。

(もっと読む)

MOS型電界効果トランジスタ及びその製造方法

【課題】ソース・ドレイン間リーク電流を低減し、スタンバイ時の消費電力を削減することで、回路の高速性を損なわず、消費電力を低減できるMOS型電界効果トランジスタの製造方法を提供することを課題とする。

【解決手段】半導体基板1上にゲート絶縁膜を介してゲート電極4を形成する工程と、前記ゲート電極4の側壁にゲート電極サイドウォール6を形成する工程と、前記ゲート電極サイドウォール6の両側にソース・ドレイン2、3を形成する工程とを有するMOS型電界効果トランジスタの製造方法であって、前記ソース・ドレイン2、3のpn接合領域に重なる絶縁体7を形成する工程を有することを特徴とする。

(もっと読む)

半導体装置

【課題】同一半導体基板上に形成されたpMOSトランジスタ及びnMOSトランジスタにおける移動度を向上させることができる半導体装置を提供する。

【解決手段】面方位(001)のn型ウェル領域13には、ソース領域14及びドレイン領域15が離隔して形成されている。ソース領域14とドレイン領域15との間のn型ウェル領域13上にはゲート絶縁膜16が形成され、ゲート絶縁膜16上にはゲート電極17が形成されている。ソース領域14とドレイン領域15との間のn型ウェル領域13に形成されるチャネル領域のチャネル長方向は、n型ウェル領域13の方位<100>に設定され、チャネル長方向には引っ張り応力が発生している。

(もっと読む)

1 - 10 / 10

[ Back to top ]