Fターム[5F048BC01]の内容

MOSIC、バイポーラ・MOSIC (97,815) | ソース・ドレイン (8,322) | 形状 (1,394)

Fターム[5F048BC01]の下位に属するFターム

分割ドレイン(ソース) (356)

Fターム[5F048BC01]に分類される特許

1 - 20 / 1,038

半導体装置およびその製造方法

固体撮像装置及びその製造方法

【課題】フォトダイオードに蓄積された電荷をより正確に読み出す。

【解決手段】固体撮像装置は、半導体基板11と、半導体基板11内に設けられ、第1導電型の半導体層を有するフォトダイオード16と、フォトダイオード16上に設けられ、上部又は全体が第2導電型の半導体層からなるシールド層27と、半導体基板11に設けられ、フォトダイオード16に蓄積された電荷を浮遊拡散層に転送する転送トランジスタ20とを含む。シールド層27の上面は、半導体基板11の上面より高い。

(もっと読む)

半導体装置

【課題】ゲート絶縁膜近傍の酸化物半導体膜に含まれる不純物元素濃度を低減する。また、ゲート絶縁膜近傍の酸化物半導体膜の結晶性を向上させる。また、当該酸化物半導体膜を用いることにより、安定した電気特性を有する半導体装置を提供する。

【解決手段】下地絶縁膜と、下地絶縁膜上に形成された酸化物半導体膜と、酸化物半導体膜上に形成されたソース電極、及びドレイン電極と、酸化物半導体膜、ソース電極、及びドレイン電極上に形成されたシリコン酸化物を含むゲート絶縁膜と、ゲート絶縁膜と接し、少なくとも前記酸化物半導体膜と重畳する領域に設けられたゲート電極と、を有し、酸化物半導体膜は、ゲート絶縁膜との界面から酸化物半導体膜に向けてシリコン濃度が1.0原子%以下の濃度である領域を有し、少なくとも領域内に、結晶部を含む半導体装置である。

(もっと読む)

横方向に可変の仕事関数を有するゲート電極を含む半導体構造体

【課題】 横方向に可変の仕事関数を有するゲート電極を含む半導体構造体を提供する。

【解決手段】 CMOS構造体などの半導体構造体が、横方向に可変の仕事関数を有するゲート電極を含む。横方向に可変の仕事関数を有するゲート電極は、角度傾斜イオン注入法又は逐次積層法を用いて形成することができる。横方向に可変の仕事関数を有するゲート電極は、非ドープ・チャネルの電界効果トランジスタ・デバイスに向上した電気的性能をもたらす。

(もっと読む)

半導体装置およびその製造方法

【課題】隣接するSOI領域とバルクシリコン領域とが短絡することを防止する。

【解決手段】一つの活性領域内にSOI領域およびバルクシリコン領域が隣接する半導体装置において、それぞれの領域の境界にダミーゲート電極8を形成することにより、BOX膜4上のSOI膜5の端部のひさし状の部分の下部の窪みにポリシリコン膜などの残渣が残ることを防ぐ。また、前記ダミーゲート電極8を形成することにより、それぞれの領域に形成されたシリサイド層14同士が接触することを防ぐ。

(もっと読む)

半導体装置、および、その製造方法、固体撮像装置

【課題】ショートチャネル特性などを向上する。

【解決手段】n型FET111Nの半導体活性層111Cの上面に、バックゲート絶縁膜401を介してバックゲート電極121を金属材料で形成する。ここでは、バックゲート電極121,221について、半導体活性層111Cの上面においてゲート電極111Gおよび一対のソース・ドレイン領域111A,111Bに対応する部分を被覆するように、バックゲート電極121を形成する。

(もっと読む)

半導体装置

【課題】IGBT終端部でのリカバリ破壊を防ぎ、ダイオードのスナップバックを抑制することができる半導体装置を提供する。

【解決手段】N−型のドリフト層30の上に形成されたP型のチャネル層31を含む半導体基板32のうちチャネル層31側の一面33とは反対側の他面34側に、P++型のコレクタ層53とN++型のカソード層54とが同じ階層に形成されている。そして、P++型のコレクタ層53がトレンチ35の延設方向における表面IGBT専用領域10および表面ダイオード専用領域20の周辺部25にそれぞれ設けられていることによりN++型のカソード層54は四角形状にレイアウトされている。また、P++型のコレクタ層53がエミッタ領域39の終端部39aから距離aを半径とする円形状に設けられていることにより当該四角形状の角部が窪んだ形状にレイアウトされている。

(もっと読む)

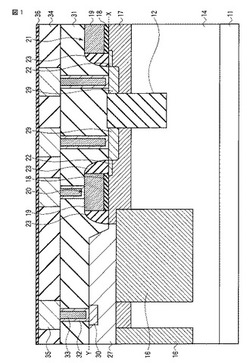

半導体集積回路装置および半導体集積回路装置の製造方法

【課題】ハイブリッド基板構造を有する半導体集積回路装置においては、SOI−MISFETとバルク−MISFETの混在する結果、ゲートファースト方式で両方のMISFETを作製した場合、それぞれでゲート材料に合った構造設計が必要である。バルク−MISFETはこれまでに多くの知見があり、ゲート材料変更に伴う構造変更は開発コストの増大を招くことになるため、可能な限りバルク−MISFETの構造を維持したい。また従来のゲートラスト方式でゲート電極材料の変更を行う場合は、プロセスの複雑化や製造コスト増大などの問題を招く恐れがある。

【解決手段】本願発明は、半導体基板のデバイス面上にSOI構造とバルク構造が混在するハイブリッド基板構造を有する半導体集積回路装置において、前記デバイス面を基準とするSOI型MISFETのゲート電極の高さを、バルク型MISFETのゲート電極の高さよりも高くしたものである。

(もっと読む)

半導体装置

【課題】 ゲート長方向に対し水平に複数本のトレンチを形成することにより単位面積当たりのゲート幅を増大させる高駆動能力横型MOSにおいて、素子面積を増加させずに更に駆動能力を向上させる。

【解決手段】 半導体基板表面から一定の深さに設けられた高抵抗第一導電型半導体のウェル領域と、前記ウェル領域の表面から途中の深さまで達する複数本のトレンチと、前記トレンチが形成する凹凸部の表面に設けられたゲート絶縁膜と、前記トレンチ内部に埋め込まれたゲート電極と前記トレンチ両端付近を除く前記凹凸部領域において前記トレンチ内部に埋め込まれたゲート電極と接触して基板表面に設けられたゲート電極膜と、前記ゲート電極膜と接触して前記トレンチ両端付近のトレンチ内部に半導体基板表面より深い位置に表面が位置するように埋め込まれたゲート電極膜と、前記ゲート電極膜と接触していない半導体面から前記ウェル領域の深さより浅く設けられた2つの低抵抗第二導電型半導体層であるソース領域とドレイン領域を有する半導体装置とした。

(もっと読む)

トンネルトランジスタ、トランジスタを含む論理ゲート、論理ゲートを使用するスタティックランダムアクセスメモリ、およびトンネルトランジスタの製造方法

【課題】第1、第2ゲートを有するトンネルトランジスタで、第1、第2のゲート間の電圧の差がより小さい場合にしようできるトンネルトランジスタを提供する。

【解決手段】ドレイン2、ソース4およびドレイン2とソース4との間で電流を制御するための少なくとも第1ゲート6とを含み、第1および第2のゲート誘電体材料7、11の第1側9、13が、それぞれ第1および第2の半導体部分14、15に実質的に沿って、実質的に接続して配置されたトンネルトランジスタ1。

(もっと読む)

半導体装置

【課題】微細化しても高いオン電流を得ることができるトランジスタを用いた、半導体装置。

【解決手段】トランジスタが、絶縁表面上の一対の第1導電膜と、一対の第1導電膜上の半導体膜と、一対の第1導電膜にそれぞれ接続されている一対の第2導電膜と、半導体膜上の絶縁膜と、絶縁膜上において、半導体膜と重なる位置に設けられた第3導電膜とを有する。また、半導体膜上における第3導電膜の端部と、一対の第2導電膜が設けられた領域とは、離隔している。

(もっと読む)

半導体装置およびその製造方法

【課題】高耐圧MOSFETの耐圧を向上させる。

【解決手段】MOSFETのドレイン領域を構成するLDD層6内に、LDD層6よりも不純物濃度層が低いN−−層11を形成して、チャネル領域側のドレイン領域端部の不純物濃度を低下させる。また、ソース領域側のLDD層7をLDD層6よりも浅い接合深さで、且つLDD層6よりも低い不純物濃度で形成する。これにより、オン状態およびオフ状態のいずれの状態においてもドレイン領域の電界を緩和し、インパクトイオンおよびパンチスルーの発生を防ぐ。

(もっと読む)

半導体装置およびその製造方法

【課題】FinFETの隣接するフィン同士のショートを回避しつつ、エピタキシャル層の表面積を広く確保する。

【解決手段】実施形態によれば、半導体装置は、半導体基板と、前記半導体基板の表面に形成され、(110)面である側面を有するフィンとを備える。さらに、前記装置は、前記フィンの側面に形成されたゲート絶縁膜と、前記フィンの側面および上面に、前記ゲート絶縁膜を介して形成されたゲート電極とを備える。さらに、前記装置は、前記フィンの側面に、フィン高さ方向に沿って順に形成された複数のエピタキシャル層を備える。

(もっと読む)

半導体装置およびその製造方法

【課題】論理素子のnチャネルMOSトランジスタに十分な膜厚の引張応力膜を形成し、メモリ素子がゲート電極間の層間絶縁膜の埋込不良を生じない製造方法の提供。

【解決手段】論理素子は、第1及び第2のnチャネルMOSトランジスタを含み、第1のゲート高さGH1及び第1のゲート長を有するゲート電極を有し、ゲート電極は第1の間隔Dを有し、メモリ素子は、第3および第4のnチャネルMOSトランジスタを含み、ゲート高さGH2および第2のゲート長を有するゲート電極を含み、論理素子及びメモリ素子は第1の引張応力膜64で覆われ、論理素子は、さらに第2の引張応力膜65で覆われ、論理素子及びメモリ素子のゲート間に形成された引張応力膜の最小距離は各々第1の距離LL及び第1の距離LMで隔てられ、第1のアスペクト比(GH1/LL)と、第2のアスペクト比(GH2/LM)とは略等しい。

(もっと読む)

半導体装置

【課題】消費電力が小さく抑えられ、出力される電位の振幅が小さくなるのを防ぐことができる、単極性のトランジスタを用いた半導体装置。

【解決手段】第1電位を有する第1配線、第2電位を有する第2配線、及び第3電位を有する第3配線と、極性が同じである第1トランジスタ及び第2トランジスタと、第1トランジスタ及び第2トランジスタのゲートに第1電位を与えるか、第1トランジスタ及び第2トランジスタのゲートに第3電位を与えるかを選択し、なおかつ、第1トランジスタ及び第2トランジスタのドレイン端子に、1電位を与えるか否かを選択する複数の第3トランジスタと、を有し、第1トランジスタのソース端子は、第2配線に接続され、第2トランジスタのソース端子は、第3配線に接続されている半導体装置。

(もっと読む)

半導体装置の製造方法

【課題】一定のドレイン電圧及びゲート電圧に対して得られるドレイン電流を増大することの出来る半導体装置の製造方法を提供する。

【解決手段】チャンネル領域と、ソース領域及びドレイン領域と、前記ソース領域及びドレイン領域にそれぞれ電気的に接続する合計二つの第1の電極と、前記チャンネル領域上にゲート絶縁膜を介して設けられた第2の電極とを備えた半導体装置の製造に際し、前記ゲート絶縁膜を、酸素の含有量を1ppb以下にした水素添加超純水にIPAを添加した洗浄液を用いて、酸素含有量1ppb以下の窒素雰囲気でしかも遮光した状態で表面の洗浄を行ない、かつ等方性酸化または窒化で形成することにより、前記チャンネル領域と前記ゲート絶縁膜との界面の平坦度を、前記ソース領域から前記ドレイン領域に向かう方向での長さ2nmにおけるピーク・トゥ・バレイ値が0.3nm以下となるようにするとともに、前記第1の電極から前記チャンネル領域までの抵抗率を4Ω・μm以下とした。

(もっと読む)

半導体装置

【課題】大規模な変更を必要とせず開発上の負荷が小さい半導体装置を提供する。

【解決手段】High SideのIGBTにおける比(コレクタコンタクト面積/コレクタ活性面積)および比(p+領域上コンタクト面積/p+領域面積)の少なくともいずれかが、Low SideのIGBTにおける上記比よりも高い。

(もっと読む)

半導体装置

【課題】抵抗値が制御されることができる抵抗素子を有する半導体装置を提供する。

【解決手段】半導体装置は、半導体基板101と、絶縁膜14bと、半導体素子と、抵抗素子4tとを有する。絶縁膜14bは半導体基板101の少なくとも一部を被覆している。半導体素子は、半導体基板101の一部からなるチャネル領域と、電極とを有する。抵抗素子4tは、電極を流れる電流に対する抵抗となるように電極と電気的に接続され、かつ絶縁膜14bを介して半導体基板101上に設けられている。抵抗素子4tは半導体領域を含む。半導体基板101と抵抗素子4tとの間の電位差により半導体領域に空乏層が生じる。

(もっと読む)

半導体装置およびその製造方法

【課題】不純物イオンの注入による悪影響を防止しつつ水平方向の耐圧を向上できる半導体装置およびその製造方法を提供する。

【解決手段】半導体装置は、素子を構成し、電流が流れる一対の不純物領域が、半導体基板の第1主面の表層に形成されたものであり、水平方向の耐圧を確保するため、フィールドプレート33を有している。これに加えて、この半導体装置は、半導体基板の表面から、素子の電流経路となる第1不純物領域37および第2不純物領域38よりも深い所定の深さおいて、少なくとも第1不純物領域および第2不純物領域の間の領域に半導体基板と同一成分の非晶質層24を有する。この非晶質層は、単結晶および多結晶よりも高抵抗の層であり、擬似的なフィールドプレートとして機能する。そして、この非晶質層は、不活性元素のイオン注入により形成される。

(もっと読む)

窒化物半導体装置

【課題】スイッチングノイズ発生を抑制できるノーマリオフ形の窒化物半導体装置の提供。

【解決手段】本発明の実施形態の窒化物半導体装置は、AlxGa1−xN(0≦x<1)からなる第1の半導体層4と、AlyGa1−yN(0<y≦1、x<y)からなる第2の半導体層5と、導電性基板2と、第1の電極6と、第2の電極8と、制御電極7と、を備える。第2の半導体層は第1の半導体層に直接接合する。第1の半導体層は、導電性基板に電気的に接続される。第1の電極及び第2の電極は、第2の半導体層の表面に電気的に接続される。制御電極は、第1の電極と第2の電極との間の第2の半導体層の前記表面上に設けられる。第1の電極は、Si−MOSFET102のドレイン電極8aに電気的に接続される。制御電極は、前記MOSFETのソース電極6aに電気的に接続される。導電性基板は、前記MOSFETのゲート電極7aに電気的に接続される。

(もっと読む)

1 - 20 / 1,038

[ Back to top ]