Fターム[5F048BF06]の内容

MOSIC、バイポーラ・MOSIC (97,815) | 配線・電極・コンタクト (11,486) | 材料 (4,535) | シリサイド (1,808)

Fターム[5F048BF06]に分類される特許

121 - 140 / 1,808

半導体装置

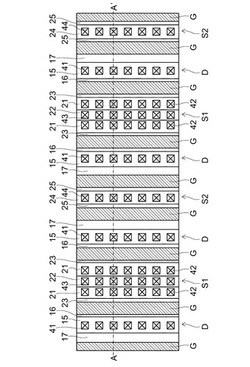

【課題】低オン抵抗且つ高アバランシェ耐量の半導体装置を提供する。

【解決手段】本発明の半導体装置は、第2導電型の第1のソースコンタクト領域21と第1導電型のバックゲートコンタクト領域22とを有する第1のソース部S1と、第2導電型の第2のソースコンタクト領域24を有し、第1導電型のバックゲートコンタクト領域を有さない第2のソース部S2と、第2導電型のドレインコンタクト領域15と、第1のソースコンタクト領域21側に形成された第2導電型の第1のドリフト領域16と、第2のソースコンタクト領域24側に形成された第2導電型の第2のドリフト領域17とを有するドレイン部Dと、を備え、第2のドリフト領域17の方が第1のドリフト領域16よりもチャネル長方向の長さが長い。

(もっと読む)

半導体装置およびその製造方法

【課題】ゲート絶縁膜をHigh−k材料で構成し、ゲート電極をメタル材料で構成するHK/MGトランジスタと、抵抗素子とを同一基板に有する半導体装置において、安定したHK/MGトランジスタの動作特性を得ることのできる技術を提供する。

【解決手段】TiN膜と多結晶Si膜との積層膜からなるHK/MGトランジスタのゲート電極を形成し、同様に、TiN膜と多結晶Si膜との積層膜からなる抵抗素子を形成した後、抵抗素子の側壁に形成したオフセットサイドウォール9aおよびサイドウォール9の一部を除去し、そのオフセットサイドウォール9aおよびサイドウォール9が除去された箇所から薬液を浸入させることによりTiN膜を除去して空洞18を形成し、多結晶Si膜のみからなる抵抗部RESを形成する。

(もっと読む)

半導体集積回路装置

【課題】I/O用バルク部とコアロジック用SOI部が混載されたバルク&SOIハイブリッド型CMISデバイスでは、閾値電圧制御の最適化のため多数のゲートスタックを用いる必要があり、プロセス及び構造が複雑になるという問題がある。

【解決手段】本願発明は、High−kゲート絶縁膜およびメタルゲート電極を有するSOI型半導体CMISFET集積回路装置において、いずれかのバックゲート半導体領域に不純物を導入することにより、対応する部分のMISFETの閾値電圧を調整するものである。

(もっと読む)

半導体集積回路装置

【課題】I/O用バルク部とコアロジック用SOI部が混載されたバルク&SOIハイブリッド型CMISデバイスでは、閾値電圧制御の最適化のため多数のゲートスタックを用いる必要があり、プロセス及び構造が複雑になるという問題がある。

【解決手段】本願発明は、High−kゲート絶縁膜およびメタルゲート電極を有するSOI型半導体CMISFET集積回路装置において、いずれかのバックゲート半導体領域に不純物を導入することにより、対応する部分のMISFETの閾値電圧を調整するものである。

(もっと読む)

半導体装置の製造方法

【課題】n型FET及びp型FET(電界効果トランジスター)のうち、一方のFETの電流駆動能力の低下を抑制し、他方のFETの電流駆動能力の向上を図る。

【解決手段】n型FET及びp型FETを覆うように、第1の膜を形成する工程と、その後、p型(n型)FET上の前記第1の膜に対して、イオン注入法によって選択的に不純物を打ち込む工程とを有し、n型(p型)FETのチャネル形成領域には、n型(p型)FET上の前記第1の膜によって、主として、n型(p型)FETのゲート電極のゲート長方向に引張(圧縮)応力が発生しており、不純物を打ち込む工程によって、前記p型(n型)FETのチャネル形成領域に発生する引張(圧縮)応力は、n型(p型)FETのチャネル形成領域に発生する引張(圧縮)応力よりも小さくなっている。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】より良い製造工程で良好な特性の半導体装置を製造する技術を提供する。

【解決手段】導電性膜上に第1領域1Asを覆い、第1領域と隣接する第2領域1Adを開口したマスク膜を形成し、導電性膜中に不純物イオンを注入し、導電性膜を選択的に除去することにより、第1領域と第2領域との境界を含む領域にゲート電極GE1を形成する。その後、熱処理を施し、ゲート電極の側壁に側壁酸化膜7を形成し、ゲート電極の第2領域側の端部の下方に位置する半導体基板中にドレイン領域を形成し、ゲート電極の第1領域側の端部の下方に位置する半導体基板中にソース領域を形成する。かかる工程によれば、ドレイン領域側のバーズビーク部7dを大きくし、ソース領域側のバーズビーク部を小さくできる。よって、GIDLが緩和され、オフリーク電流を減少させ、また、オン電流を増加させることができる。

(もっと読む)

半導体装置の製造方法

【課題】トランジスタのチャネル部に印加される応力を増加させて、電流増加効果を高めることを可能とする。

【解決手段】半導体基板上にダミーゲートを形成した後、該ダミーゲートの側壁に側壁絶縁膜を形成し、該ダミーゲートの両側の前記半導体基板にソース・ドレイン領域を形成する工程と、前記ダミーゲートおよび前記ソース・ドレイン領域の上に応力印加膜を形成する工程と、前記ダミーゲートの上の領域に形成された前記応力印加膜と前記ダミーゲートを除去して溝を形成する工程と、前記溝内の前記半導体基板上にゲート絶縁膜を介してゲート電極を形成する工程と、を備えた半導体装置の製造方法。

(もっと読む)

半導体装置およびその製造方法

【課題】微細化しても高い性能を実現可能な半導体装置を提供する。

【解決手段】実施の形態の半導体装置は、半導体基板と、半導体基板上に形成されたゲート絶縁膜と、ゲート絶縁膜上に形成されたゲート電極と、ゲート電極の両側に形成された第1のゲート側壁と、半導体基板上に形成され、ゲート電極との間に第1のゲート側壁を挟むソース・ドレイン半導体層と、を備える。さらに、ゲート電極の両側に、第1のゲート側壁上およびソース・ドレイン半導体層上に形成され、第1のゲート側壁との境界がゲート電極の側面で終端し、第1のゲート側壁よりもヤング率が小さく、かつ、低誘電率の第2のゲート側壁、を備える。

(もっと読む)

半導体装置およびその製造方法

【課題】ゲート絶縁膜をHigh−k材料で構成し、ゲート電極をメタル材料で構成するHK/MGトランジスタを有する半導体装置において、安定した動作特性を得ることのできる技術を提供する。

【解決手段】素子分離部2で囲まれた活性領域14に位置し、後の工程でコア用nMISのゲートGが形成される領域Ga1のみに、Nch用ゲートスタック構造NGを構成する積層膜を形成し、上記領域Ga1以外の領域NGa1には、Pch用ゲートスタック構造PGを構成する積層膜を形成する。これにより、コア用nMISのゲートGが形成される領域Ga1へ素子分離部2から引き寄せられる酸素原子の供給量を減少させる。

(もっと読む)

赤外線センサの製造方法

【課題】赤外線センサにおけるMOSトランジスタのしきい値のばらつきを小さくすることが可能な赤外線センサの製造方法を提供する。

【解決手段】半導体基板1の一表面側にシリコン酸化膜31とシリコン窒化膜32との積層膜を形成してから、シリコン窒化膜32のうち熱型赤外線検出部3の形成予定領域A1に対応する部分を残してMOSトランジスタ4の形成予定領域A2に対応する部分をドライエッチングにより除去する。その後、半導体基板1の一表面側に第1のイオン注入を行ってウェル領域41を形成してから、MOSトランジスタ4のしきい値電圧を制御するための第2のイオン注入を行う。ウェル領域を形成する工程では、シリコン酸化膜31のうちMOSトランジスタ4の形成予定領域A2に形成されている部分(シリコン酸化膜51)の一部をウェットエッチングにより除去してから、シリコン酸化膜31をマスクとして第1のイオン注入を行う。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】基板表面にシリサイド膜が形成された半導体装置において、ゲート電極パターンの粗密に関わらず、コンタクトの深さの差を緩和する。

【解決手段】半導体装置100は、活性領域(104)に、表面にシリコン酸化膜122aが選択的に形成されたシリサイド膜120aを形成する工程と、その上に、シリコン酸化膜120aとの間でエッチング選択比を有するライナー絶縁膜124を形成する工程と、その上に、ライナー絶縁膜124との間でエッチング選択比を有する絶縁膜(126)を形成する工程と、絶縁膜(126)、ライナー絶縁膜124、およびシリコン酸化膜122aを貫通してシリサイド膜120aに達する第1のコンタクトホール144を形成する工程と、により製造される。

(もっと読む)

半導体装置およびその製造方法

【課題】サリサイドプロセスにより金属シリサイド層を形成した半導体装置の信頼性を向上させる。

【解決手段】部分反応方式のサリサイドプロセスによりゲート電極8a、8b、n+型半導体領域9bおよびp+型半導体領域10bの表面に金属シリサイド層41を形成する。金属シリサイド層41を形成する際の第1の熱処理では、熱伝導型アニール装置を用いて半導体ウエハを熱処理し、第2の熱処理では、マイクロ波アニール装置を用いて半導体ウエハを熱処理することにより、第2の熱処理を低温化し、金属シリサイド層41の異常成長を防ぐ。これにより金属シリサイド層41の接合リーク電流を低減する。

(もっと読む)

半導体装置の製造方法及び半導体装置

【課題】同一基板上にゲート絶縁膜が厚いMOSトランジスタと薄いMOSトランジスタとを有する半導体装置の新規な製造方法を提供する。

【解決手段】半導体装置の製造方法は、半導体基板の第1活性領域上に第1ゲート絶縁膜を、第2活性領域上にそれより薄い第2の膜厚の第2ゲート絶縁膜を酸化シリコンを含む材料で形成する工程と、第1及び第2ゲート絶縁膜を覆うポリシリコン膜をパターニングして第1及び第2ゲート絶縁膜上それぞれに第1及び第2ゲート電極を形成する工程と、第1及び第2ゲート電極を覆う絶縁膜を異方性エッチングして第1及び第2ゲート電極の側面にサイドウォール絶縁膜を残す工程と、第1ゲート電極側面上のサイドウォール絶縁膜を除去する工程と、第1ゲート電極の側面上のサイドウォール絶縁膜が除去された半導体基板を酸化雰囲気中で熱処理する工程とを有する。

(もっと読む)

半導体装置の製造方法

【課題】半導体装置の性能を向上させる。

【解決手段】半導体基板1の主面にゲート絶縁膜用の界面層3、Al含有膜4、Hf含有膜5、Al含有膜6及びマスク層7を形成してから、nチャネル型MISFET形成予定領域であるnMIS形成領域1Aのマスク層7とAl含有膜6を選択的に除去する。それから、nMIS形成領域1AのHf含有膜5上とpチャネル型MISFET形成予定領域であるpMIS形成領域1Bのマスク層7上に希土類含有膜8を形成し、熱処理を行って、nMIS形成領域1AのHf含有膜5を希土類含有膜8と反応させ、pMIS形成領域1BのHf含有膜5をAl含有膜4,6と反応させる。その後、未反応の希土類含有膜8とマスク層7を除去してから、メタルゲート電極を形成する。

(もっと読む)

パワー半導体デバイスおよびその製造方法

【課題】改善されたパワーデバイスに加えてそれらの製造方法,パッケージ化の実施例を提供する。1実施例としては、シールドされたゲートトレンチMOSFETにおいて、多くの電荷調整技術と寄生容量を低減する他の技術とを組み合わせて、改善された電圧性能,速いスイッチング速度および低いオン抵抗を有するパワーデバイスを提供する。

【解決手段】シールドポリ311の上にゲートポリ310を含み、垂直方向電荷制御のために、ゲートトレンチ302より深い位置にある非ゲートトレンチを含み、電荷制御トレンチ301は、トレンチの最上部でソース金属に接続する導電材料の単層を有し得るが、独立してバイアスがかけられ、多重に積み重ねられたポリ電極313を使用する。また、デュアルゲート構造を用いることによってゲートとドレインとの間の容量Cgdを低減する。

(もっと読む)

半導体装置及びその製造方法

【課題】構造が簡単なトランジスタにより、サステイン耐圧を改善し且つサステイン耐圧のばらつきの抑制及びトランジスタ形成後のドレイン抵抗及び接合プロファイルの調整が可能な、自由度が高い半導体装置を実現できるようにする。

【解決手段】半導体装置は、p型ウェル102に形成され、互いに並行に延びると共に、ゲート長方向の幅が比較的に大きい第1ゲート電極125と、ゲート長方向の幅が比較的に小さい第2ゲート電極126と、p型ウェル102における第1ゲート電極125及び第2ゲート電極126同士の間に形成されたLDD低濃度領域135と、該p型ウェル102における第1ゲート電極125及び第2ゲート電極126のそれぞれの外側に形成されたLDD中濃度領域134とを有している。LDD低濃度領域135の不純物濃度は、LDD中濃度領域134の不純物濃度よりも低い。

(もっと読む)

半導体装置およびその製造方法

【課題】溝型の素子間分離部により囲まれた活性領域に形成される電界効果トランジスタにおいて、所望する動作特性を得ることのできる技術を提供する。

【解決手段】素子分離部SIOを、溝型素子分離膜6L,6Sと、溝型素子分離膜6L,6Sの上面に形成されたシリコン膜またはシリコン酸化膜からなる厚さ10〜20nmの拡散防止膜20と、拡散防止膜20の上面に形成された厚さ0.5〜2nmのシリコン酸化膜21L,21Sとから構成し、拡散防止膜20の組成をSiOx(0≦x<2)とし、溝型素子分離膜6L,6Sおよびシリコン酸化膜21L,21Sの組成をSiO2とする。

(もっと読む)

埋没ジャンクションを有する垂直型トランジスタ及びその形成方法

【課題】ドーパントの濃度をより高く確保しつつも、ドーパントが拡散されるジャンクション深さを制御することができ、改善された接触抵抗を実現し、チャネル領域との離隔間隔を減らしてチャネルのしきい電圧(Vt)を改善できる埋没ジャンクションを有する垂直型トランジスタ及びその形成方法を提供すること。

【解決手段】半導体基板に第1の側面に反対される第2の側面を有して突出した壁体)を形成し、壁体の第1の側面の一部を選択的に開口する開口部を有する片側コンタクトマスクを形成した後、開口部に露出した第1の側面部分に互いに拡散度が異なる不純物を拡散させて第1の不純物層及び該第1の不純物層を覆う第2の不純物層を形成することを特徴とする。

(もっと読む)

半導体装置及びその製造方法

【課題】トランジスタの耐圧を向上し得る半導体装置及びその製造方法を提供することにある。

【解決手段】半導体基板10内に形成された第1導電型の第1の不純物領域32、46と、半導体基板内に形成され、第1の不純物領域に隣接する第2導電型の第2の不純物領域34、48と、第2の不純物領域内に形成された第1導電型のソース領域30a、44aと、第1の不純物領域内に形成された第1導電型のドレイン領域30b、44bと、ソース領域とドレイン領域との間における第1の不純物領域内に、第2の不純物領域から離間して埋め込まれた、二酸化シリコンより比誘電率が高い絶縁層14と、ソース領域とドレイン領域との間における第1の不純物領域上、第2の不純物領域上及び絶縁層上に、ゲート絶縁膜22を介して形成されたゲート電極24a、24bとを有している。

(もっと読む)

半導体装置

【課題】ホールド電圧を変化させずに、トリガー電圧のみを調節することができるようにする。

【解決手段】本実施形態における保護素子10は、低濃度コレクタ層102、シンカー層110、高濃度コレクタ層112、エミッタ層130、高濃度ベース層122、ベース層120、第1導電型層140、及び第2導電型層150を有している。第2導電型層150は低濃度コレクタ層102に形成されており、ベース層120と第1導電型層140の間に位置している。第2導電型層150は低濃度コレクタ層102よりも不純物濃度が高い。

(もっと読む)

121 - 140 / 1,808

[ Back to top ]