Fターム[5F048BF06]の内容

MOSIC、バイポーラ・MOSIC (97,815) | 配線・電極・コンタクト (11,486) | 材料 (4,535) | シリサイド (1,808)

Fターム[5F048BF06]に分類される特許

141 - 160 / 1,808

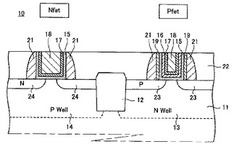

半導体装置及び半導体装置の製造方法

【課題】微細構造を有する半導体装置において、ゲート長の最適化が可能な半導体装置を提供する。

【解決手段】基体上に形成された高誘電率材料からなるゲート絶縁膜15と、ゲート絶縁膜15上に形成されたメタルゲート電極と、メタルゲート電極の側壁に形成されたサイドウォールスペーサ21とを備える半導体装置10を構成する。そして、第1導電型のトランジスタ及び第2導電型のトランジスタのいずれか一方にメタルゲート電極側壁とサイドウォールスペーサ21内壁との間に形成されたオフセットスペーサ19が形成される。或いは、第1導電型のトランジスタと第2導電型のトランジスタとに、厚さの異なるオフセットスペーサ19が形成される。

(もっと読む)

埋め込みゲートを有する半導体装置及びその製造方法

【課題】埋め込みゲートトランジスタのSCEに対する免疫性を向上させると同時に、分岐点での重なりを増加させる方法及び構造の提供。

【解決手段】基板102は第1活性領域104と第2活性領域106とを有し、浅溝分離(STI)領域108によって分離される。バッファ層112は応力緩和層として機能しハードマスク層114が形成される。基板102の表面に分離領域108を部分的に網羅するように凹部118を設ける。ゲート誘電体120が凹部118に形成された後第一ドーパントインプラント122により、ドープ済みチャンネル領域124が形成される。インプラントはハードマスク114を貫通しないので、凹部118の下に形成されたドープ済みチャンネル領域124中のドーパント濃度は最も高くなる。ドープ済みチャンネル領域124はトランジスタのオン・オフを切り替える閾値電圧を変調する。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】半導体装置の特性を向上させる。

【解決手段】本発明の半導体装置は、面方位が(110)のシリコン基板1と、pMIS領域1Bに形成されたpチャネル型電界効果トランジスタを有する。このpチャネル型電界効果トランジスタは、ゲート絶縁膜3を介して配置されたゲート電極GE2と、ゲート電極の両側のシリコン基板1中に設けられた溝g2の内部に配置され、Siより格子定数が大きいSiGeよりなるソース・ドレイン領域と、を有する。上記溝g2は、ゲート電極側に位置する側壁部において、面方位が(100)の第1の斜面と、第1の斜面と交差する面方位が(100)の第2の斜面と、を有する。上記構成によれば、基板の表面(110)面と(100)面とのなす角は45°となり、比較的鋭角に第1斜面が形成されるため、効果的にpチャネル型のMISFETのチャネル領域に圧縮歪みを印加することができる。

(もっと読む)

半導体装置の製造方法

【課題】フラッシュメモリセルと低電圧動作トランジスタや高電圧動作トランジスタを集積化し、異種トランジスタを混載する半導体装置の製造法を提供する。

【解決手段】半導体装置の製造方法は、(a)トンネル絶縁膜、Fゲート電極膜、電極間絶縁膜を堆積したFゲート電極構造を形成し(b)ゲート絶縁膜を形成し(c)導電膜、エッチストッパ膜を堆積し(d)エッチストッパ膜、導電膜をエッチングした積層ゲート電極構造を形成し(e)積層ゲート電極構造の側壁上に第1絶縁膜を形成し(f)積層ゲート電極側壁上に第1サイドウォールスペーサ層を形成し(g)エッチストッパ層を除去し(h)他の領域の導電層から、ゲート電極構造を形成し(i)積層ゲート電極構造、ゲート電極構造側壁上に第2サイドウォールスペーサを形成し(j)希弗酸水溶液で半導体基板表面を露出し(k)半導体基板表面にシリサイド層を形成する。

(もっと読む)

電子装置及び電子装置の作製方法

【課題】信頼性及び色再現性の高い電子装置を提供する。

【解決手段】単結晶半導体基板11上にスイッチング用FET201及び電流制御用FET202を形成し、電流制御用FET202にEL素子203が電気的に接続された画素構造とする。電流制御用FET202は画素間での特性ばらつきが極めて小さく、色再現性の高い画像を得ることができる。電流制御用FET202にホットキャリア対策を施すことで信頼性の高い電子装置が得られる。

(もっと読む)

半導体装置及びその製造方法

【課題】素子分離領域のエッチングを生じさせることなく、基板上にサイドウォール幅が異なる複数のトランジスタを精度良く形成できるようにする。

【解決手段】

半導体装置の製造方法において、まず第1のゲート電極134及び第2のゲート電極144を覆うように、第1の絶縁膜151及び第2の絶縁膜152を順次形成する。この後、第2の絶縁膜152における第1の領域103の上に形成された部分を除去する。この後、基板101の上に第3の絶縁膜153を形成する。この後、第2の絶縁膜152及び第3の絶縁膜153を選択的に除去することにより、第1のゲート電極134の側面上に第3の絶縁膜153からなる第1の外側サイドウォール136を形成し、第2のゲート電極144の側面上に第2の絶縁膜152及び第3の絶縁膜153からなる第2の外側サイドウォール146を形成する。

(もっと読む)

半導体装置および携帯電話機

【課題】アンテナスイッチのコスト削減を図る観点から、特に、アンテナスイッチをシリコン基板上に形成された電界効果トランジスタから構成する場合であっても、アンテナスイッチで発生する高調波歪みをできるだけ低減できる技術を提供する。

【解決手段】RXスルートランジスタ群TH(RX)は、互いに直列に接続されたMISFETQ1〜Q5において、それぞれのMISFETのボディ領域と、隣接するMISFETのソース領域あるいはドレイン領域とを、それぞれ、ダイオード(整流素子)を介して接続する。そして、特に、nチャネル型MISFETの場合、MISFETのボディ領域から隣接するMISFETのソース領域あるいはドレイン領域へ向う向きが順方向となるようにダイオードを接続する。

(もっと読む)

半導体装置の製造方法

【課題】トランジスタのチャネル不純物の拡散を抑制し、高性能・高信頼性を実現しうる半導体装置の製造方法を提供する。

【解決手段】半導体基板第1及び第2の領域に非晶質化のためのイオン注入を行い、第1の領域及び第2の領域に第1の不純物及び第2の不純物をそれぞれイオン注入し、注入した不純物を活性化して第1の不純物層及び第2の不純物層を形成し、不純物層を形成した半導体基板上に半導体層をエピタキシャル成長し、第1及び第2の領域上にゲート絶縁膜を成長し、第1及び第2のゲート絶縁膜上に第1及び第2のゲート電極をそれぞれ形成する。

(もっと読む)

半導体装置の製造方法

【課題】高性能・高信頼性を実現しうる半導体装置の製造方法を提供する。

【解決手段】半導体基板にアライメントマークとなる溝を形成し、アライメントマークに位置合わせして素子分離領域となる領域を露出し素子領域となる領域を覆うマスク膜を形成し、マスク膜をマスクとして半導体基板を異方性エッチングし、半導体基板の素子分離領域となる領域に素子分離溝を形成し、素子分離溝を絶縁膜で埋め込み素子分離絶縁膜を形成する半導体装置の製造方法において、溝を形成する工程では、マスク膜の厚さに相当する深さよりも浅い溝を形成する。

(もっと読む)

半導体装置及びその製造方法

【課題】低廉なプロセスにて高性能・高信頼性を実現しうる半導体装置及びその製造方法を提供する。

【解決手段】第1の領域に形成された第1の不純物層及び第1のエピタキシャル半導体層と、第1のエピタキシャル半導体層上にゲート絶縁膜を介して形成された第1のゲート電極と、第1の領域に形成された第1のソース/ドレイン領域とを有する第1のトランジスタと、第2の領域に形成された第2の不純物層及び第1のエピタキシャル半導体層よりも薄い第2のエピタキシャル半導体層と、第2のエピタキシャル半導体層上にゲート絶縁膜を介して形成された第2のゲート電極と、第2の領域に形成された第2のソース/ドレイン領域とを有する第2のトランジスタとを有する。

(もっと読む)

半導体装置及びその製造方法

【課題】低電圧トランジスタ及び高電圧トランジスタの双方の要求を満たし、高性能・高信頼性を実現しうる半導体装置及びその製造方法を提供する。

【解決手段】ボロン又はリンを含む第1の不純物層と、第1の不純物層上に形成された第1のエピタキシャル層と、第1のエピタキシャル層上に第1のゲート絶縁膜を介して形成された第1のゲート電極と、第1のソース/ドレイン領域とを有する第1のトランジスタと、ボロン及び炭素又は砒素を含む第2の不純物層と、第2の不純物層上に形成された第2のエピタキシャル層と、第2のエピタキシャル層上に、第1のゲート絶縁膜よりも薄い第2のゲート絶縁膜を介して形成された第2のゲート電極と、第2のソース/ドレイン領域とを有する第2のトランジスタとを有する。

(もっと読む)

半導体装置及びその製造方法

【課題】第1,第2のゲート電極の実効ゲート長が短くなることを防止する。

【解決手段】第1のMISトランジスタnTr1は、第1のゲート電極18aにおけるゲート幅方向の側面上に形成された第1のオフセットサイドウォール22aと、第1のゲート電極におけるゲート長方向の側面及びゲート幅方向の側面上に第1のオフセットサイドウォールを介して形成された第2のオフセットサイドウォール24aと、第1のエクステンション領域26aとを備えている。第2のMISトランジスタnTr2は、第2のゲート電極18bにおけるゲート長方向の側面及びゲート幅方向の側面上に形成された第3のオフセットサイドウォール22bと、第2のゲート電極におけるゲート長方向の側面及びゲート幅方向の側面上に第3のオフセットサイドウォールを介して形成された第4のオフセットサイドウォール24bと、第2のエクステンション領域23bとを備えている。

(もっと読む)

半導体装置の製造方法

【課題】Geをチャネル材料に用いても、素子特性の劣化を抑制することを可能にする。

【解決手段】Geを含むp型半導体領域上にゲート絶縁膜を形成する工程と、前記ゲート絶縁膜上にゲート電極を形成する工程と、前記半導体領域の、前記ゲート電極の両側に位置する第1および第2領域に、有機金属錯体および酸化剤を交互に供給して金属酸化物を堆積する工程と、前記金属酸化物の上に金属膜を堆積する工程と、熱処理を行うことにより、前記半導体領域および前記金属酸化物と、前記金属膜とを反応させて前記第1および第2領域に金属半導体化合物層を形成するとともに前記金属半導体化合物層と前記半導体領域との界面に金属偏析層を形成する工程と、を備えている。

(もっと読む)

半導体装置の製造方法

【課題】平坦なNiPtシリサイド層を形成する。

【解決手段】CVD法を用いて、シリコン層26(ゲート),29(ソース・ドレイン)上にPt層を形成する。次いで、CVD法を用いて、Pt層上にNi層を、Pt層より厚く形成する。次いで、シリコン層26,29、Pt層、及びNi層を熱処理することにより、NiPtシリサイド33を形成する。Pt層の平均膜厚が0.5nm以上2nm以下であるのが好ましい。またシリコン層は、例えばMISFETのソース・ドレインである。

(もっと読む)

半導体装置

【課題】プロセスを簡素化し低コスト化を実現するとともに、さらに、システムを簡素化しノイズ対策を可能にするMEMSレゾネータ及びMEMSレゾネータの製造方法を提供する。

【解決手段】MEMSレゾネータの製造方法は、基板10上に形成された半導体デバイスとMEMS構造体部4とを有するMEMSレゾネータ2の製造方法であって、半導体デバイスは、上部電極30と下部電極26とを有するONOキャパシタ部6と、CMOS回路部8と、を含み、ONOキャパシタ部6の下部電極26を、第1シリコン層26を用いて、形成する。MEMS構造体部4の下部構造体16とONOキャパシタ部6の上部電極30とを、第2シリコン層52を用いて、形成する。及び、MEMS構造体部4の上部構造体18とCMOS回路部8のゲート電極34とを、第3シリコン層54を用いて、形成する。

(もっと読む)

半導体装置及びその製造方法

【課題】ゲート絶縁膜にhigh−k膜を使用したMIS構造の半導体装置において、互いに異なる仕事関数を有する複数の同一導電型トランジスタを設けることを可能にする。

【解決手段】同じ導電型の第1のMISトランジスタ及び第2のMISトランジスタが同じ半導体基板50上に設けられている。第1のMISトランジスタにおけるゲート絶縁膜52aの界面層2Aの厚さは、第2のMISトランジスタにおけるゲート絶縁膜52bの界面層2bの厚さよりも厚い。

(もっと読む)

半導体装置

【課題】本発明は、接続不良を抑制したコンタクト形成方法を備える半導体装置を提供するものである。

【解決手段】半導体装置は、配線層を備える第1の回路領域と、第1の回路領域の上に形成された絶縁膜と、絶縁膜の上に形成され、シリサイド膜を備える第2の回路領域と、配線層上に設けられ、配線層と電気的に接続された下部コンタクトと、下部コンタクト上に設けられ、下部コンタクトと前記シリサイド膜とを電気的に接続する上部コンタクトとを有する。

(もっと読む)

半導体装置の製造方法

【課題】 チャネル領域に応力を印加するよう作用する階段状のソース/ドレイン・エピタキシャル領域を、製造プロセスを有意に複雑あるいは冗長とすることなく形成する。

【解決手段】 ゲート電極をマスクとしてドーパントを注入し、半導体基板内にドーパント注入領域を形成する(S2)。サイドウォールの形成(S3)後、ゲート電極及びサイドウォールをマスクとして半導体基板内に第1のリセスを形成する(S4)。このとき、第1のリセスの内壁の一部からドーパント注入領域が露出される。その後、上記ドーパント注入領域を選択エッチングにより除去し、第1のリセスに連通し且つ第1のリセスより浅い第2のリセスを形成する(S5)。それにより、階段状のリセスが形成される。そして、第1のリセス及び第2のリセス内に、チャネル領域へのストレッサとして作用する半導体材料を成長させてソース/ドレイン領域を形成する(S6)。

(もっと読む)

半導体装置およびその製造方法

【課題】動作マージンの向上に対して有利な半導体装置およびその製造方法を提供する。

【解決手段】実施形態によれば、半導体装置は、半導体基板上に、互いのゲート電極が接続されて配置される第1トランジスタ(P2)と、前記第1トランジスタと異なる導電型を有する第2トランジスタ(N4)とを具備し、前記第1トランジスタのゲート電極は、第1不純物と前記第1不純物の拡散を抑制する第2不純物とを含有し、前記第1不純物の濃度ピーク(PE1)は、前記第2不純物の濃度ピーク(PE2)よりも浅い位置に形成されている。

(もっと読む)

半導体装置およびその製造方法

【課題】ゲート絶縁膜にハフニウムを含む絶縁膜を使用したMISFETを有する半導体装置において、MISFETの信頼性向上を図ることができる技術を提供する。

【解決手段】本発明では、nチャネル型コア用トランジスタQ1のゲート絶縁膜と、pチャネル型コア用トランジスタQ2のゲート絶縁膜の構成を相違させている。具体的に、nチャネル型コア用トランジスタQ1では、ゲート絶縁膜に酸化シリコン膜SO1とHfZrSiON膜HK1の積層膜を使用している。一方、pチャネル型コア用トランジスタQ2では、ゲート絶縁膜に酸化シリコン膜SO1とHfSiON膜HK2の積層膜を使用している。

(もっと読む)

141 - 160 / 1,808

[ Back to top ]