Fターム[5F048BG00]の内容

MOSIC、バイポーラ・MOSIC (97,815) | 絶縁体分離 (5,896)

Fターム[5F048BG00]の下位に属するFターム

材料 (562)

素子領域側面・底面を絶縁物で分離するもの (666)

素子領域側面のみを絶縁物で分離するもの (4,648)

Fターム[5F048BG00]に分類される特許

1 - 20 / 20

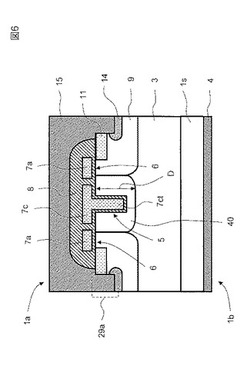

半導体装置

【課題】たとえばDC−DCコンバータ等の電源または電力変換機器のスイッチング等に使用されるパワーMOSFET等の絶縁ゲートを有するパワー系能動素子は、スイッチングの高速化に伴い、ゲート容量を極力小さくする必要がある。このためには、チャネルとならない部分のゲート電極を取り去り、スプリットゲートとする手法が有効とされている。しかし、Nチャネル型パワーMOSFETを例に取り説明すると、その反作用として、チャネルを形成するP型ボディ領域の端部に電界が集中するため、パンチスルー耐圧が低下する等の問題が発生する。

【解決手段】本願の一つの発明は、プレーナ−バーティカル型パワーMOSFET等の絶縁ゲートを有するパワー系能動素子を有する半導体装置に於いて、各アクティブセル内のスプリットゲート間にトレンチ内に延在するフィールドプレート、すなわち、トレンチフィールドプレートを設けたものである。

(もっと読む)

半導体素子およびその駆動方法

【課題】双方向で電流の流れを制御(ON/OFF制御)することができる半導体素子を提供すること。

【解決手段】チャネル層8と障壁層10が積層された半導体へテロ接合と、前記半導体へテロ接合の上方に設けられたゲート12と、前記ゲートの両側に設けられた第1および第2のソースドレイン端子14a,14bと、前記第1のソースドレイン端子と前記ゲートの間に設けられた第1のフィールプレート16aと、前記第2のソースドレイン端子と前記ゲートの間に設けられた第2のフィールドプレート16bとを有すること。

(もっと読む)

半導体装置

【課題】オン抵抗の低減を実現できる、高耐圧のLDMOSトランジスタを有する半導体装置を提供する。

【解決手段】半導体基板上に配置された第2導電型の第1半導体領域と、第1半導体領域の上面の一部に埋め込まれた第1導電型の第2半導体領域と、第2半導体領域の上面の一部に埋め込まれた第2導電型のソース領域と、第2半導体領域と離間して第1半導体領域の上面の一部に埋め込まれた第2の導電型のドレイン領域と、ソース領域とドレイン領域間で第2半導体領域上に配置されたゲート電極と、第2半導体領域とドレイン領域間で第1半導体領域上に配置された絶縁膜と、絶縁膜上に配置されてゲート電極とドレイン領域間の電圧を分圧する分圧素子と、分圧素子とドレイン領域との間に接続された電荷移動制限素子とを備える。

(もっと読む)

半導体装置およびその製造方法

【課題】本発明は、セルの有効面積を増やし、アンバランス動作等を抑制可能な半導体装置およびその製造方法を提供することを目的とする。

【解決手段】本発明にかかる半導体装置は、第1層間絶縁膜8に覆われない上面を介して、ゲート電極20と接続された、第1ゲート配線5と、第1ゲート配線5の、上面の一部を除く領域を覆って、第1層間絶縁膜8上に形成された、第2層間絶縁膜80と、第2層間絶縁膜80に覆われない上面を介して、第1ゲート配線5と接続された、第2ゲート配線16とを備え、平面視において、第2ゲート配線16の幅は、第1ゲート配線5の幅よりも広い。

(もっと読む)

半導体製造方法および半導体装置

【課題】ウェーハテスト後のウェーハ状態において所望の回路を印刷処理により容易に形成することが可能な半導体製造方法および半導体装置を提供することを課題する。

【解決手段】本発明に係る半導体製造方法は、ウェーハの被描画パターン形成領域に所定の深さを有する溝部を形成する工程、ウェーハに対してトリミング要否の検査を行う工程、前記ウェーハにおけるトリミング必要なウェーハの前記溝部に導電性溶剤を射出し描画パターンを描画する工程、描画パターンを描画した後、脱気および低温アニールする工程、脱気および低温アニールした成膜後、当該成膜表面を平坦化する工程、および平坦化した後、高温アニールする工程、を有する。

(もっと読む)

半導体装置とその製造方法、及び半導体装置の設計プログラム

【課題】半導体装置において、所望の数のトランジスタをハンドリングすること。

【解決手段】半導体装置は、半導体基板内に形成された第1導電型の第1から第4の拡散層と、半導体基板内に形成された第2導電型の第5から第8の拡散層と、第1と第2の拡散層の間及び第5と第6の拡散層の間の上方に形成された第1の電極と、第3と第4の拡散層の間及び第7と第8の拡散層の間の上方に形成された第2の電極と、第6の拡散層と第7の拡散層との間の上方に形成された絶縁膜及び第3の電極を備える。第3の電極は、第1電位に接続されている。

(もっと読む)

横型ダイオードを有する半導体装置

【課題】ホール注入を抑制して逆回復耐量の向上を図りつつ、アバランシェ耐量の向上を図ることができる横型ダイオードを有する半導体装置を提供する。

【解決手段】アノード電極11がp-型低不純物濃度領域7に対してショットキー接触もしくはオーミック接触させられ、かつ、p+型高不純物濃度領域8にオーミック接触させられるようにする。また、p-型低不純物濃度領域7およびp+型高不純物濃度領域8よりもカソード電極10から離れる側にp+型アノード拡張領域9を備える。このように、アノード電極11がp-型低不純物濃度領域7に対して電気的に接続されるようにすれば、電子注入が少なくなることで、同じ量の電流を流してもホール注入を少なくでき、逆回復電荷Qrrを低減して逆回復耐量を向上することが可能となる。また、p+型アノード拡張領域9を備えことで、アバランシェ耐量を向上させることも可能となる。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】SiGe等の半導体膜が形成された領域と、酸化シリコン膜から成るゲート絶縁膜が形成された領域とが同一基板上に形成される際に、ゲート絶縁膜を精度良く形成する。

【解決手段】基板10を熱酸化することにより、第1素子領域101及び第2素子領域201に、第1ゲート絶縁膜110及び第2ゲート絶縁膜210を形成し、かつ第3素子領域301及び第4素子領域401それぞれに位置する基板10に熱酸化膜を形成する。次いで、第4素子領域401に位置する熱酸化膜を除去する。次いで、第4素子領域401に位置する基板10上に半導体膜414を成膜する。次いで、第3素子領域301に位置する熱酸化膜を除去する。次いで、第4素子領域401に位置する半導体膜414上、及び第3素子領域301に位置する基板10上に第3ゲート絶縁膜310及び第4ゲート絶縁膜410を形成する。

(もっと読む)

半導体装置

【課題】起動回路と周辺回路とを併せて集積化し得る半導体装置を提供する。

【解決手段】領域411においては、素子分離領域により規定されるドレイン領域121にボディ領域が形成され、ボディ領域にN型のソース領域が形成される。ドレイン領域121とN型のソース領域との間に第1のゲート電極20が配置される。素子分離領域は開口部133が形成されたループ状部と、開口部133を介してドレイン領域121に接続された延在領域122を規定する部分とを備える。延在領域122に、N型のソース引出領域が形成される。内部回路412においては、ドレイン領域121にP型のボディ領域が形成され、P型のボディ領域にN型のソース領域が形成され、ドレイン領域121とN型のソース領域との間に第2のゲート電極331が形成される。

(もっと読む)

半導体装置

【課題】pMOSのゲート幅をnMOSのゲート幅の二倍としたSGTを用いた高集積で高速な少なくとも2段以上のCMOSインバータ結合回路からなる半導体装置を提供する。

【解決手段】本発明に係る半導体装置は、2段以上のCMOSインバータを結合したCMOSインバータ結合回路からなり、第一のCMOSインバータは、1行1列目と2行1列目のpMOS SGTと、1行2列目のnMOS SGTで構成され、第二のCMOSインバータは、1行3列目と2行3列目のpMOS SGTと、2行2列目のnMOS SGTで構成され、1行1列目と2行1列目のSGTのドレイン拡散層と、1行2列目のSGTのドレイン拡散層とを島状半導体下部層で接続するように配線された出力端子と、1行3列目と、2行3列目のSGTのゲートと、2行2列目のSGTのゲートとを接続するように配線された入力端子とを接続する。

(もっと読む)

記録素子駆動回路および記録素子駆動回路のレイアウト方法

【課題】 パワーMOSトランジスタアレイをドライバに用いたBJヒータボードにおいて、電源配線による電圧降下を同時オンヒータ数に寄らず一定なものとするために、パワーMOSトランジスタアレイの隣接するソースを電気的に分離する。

【解決手段】 MOSトランジスタのポリシリコンゲートを、分離したいMOSのソース部分に配置する。そのポリシリコンゲートを基板電位に固定することで、隣接するMOSトランジスタのソースを電気的に分離する。

(もっと読む)

半導体装置及びその製造方法

【課題】

高耐圧素子の高耐圧特性を確保しつつ、高耐圧素子と低耐圧素子とが良好な特性を有する半導体装置を提供する。

【解決手段】

高耐圧素子と低耐圧素子とを有する半導体装置が、高耐圧素子が形成された高耐圧素子領域と、低耐圧素子が形成された低耐圧素子領域とが規定された半導体基板と、高耐圧素子領域に設けられた第1LOCOS分離構造と、低耐圧素子領域に設けられた第2LOCOS分離構造とを含む。第1LOCOS分離構造は、半導体基板の表面に形成されたLOCOS酸化膜と、その上に形成されたCVD酸化膜からなり、第2LOCOS分離構造は、LOCOS酸化膜からなる。

(もっと読む)

半導体装置

【課題】共通の半導体基板の上に複数の半導体素子を形成すると寄生トランジスタが形成される。

【解決手段】寄生トランジスタの動作を抑制することができる複合半導体装置は、p型の第1の半導体領域7の上にn型の第2の半導体領域8と環状に形成された第3、第4及び第5の半導体領域9,11,12を有する。最も内側に配置されたn+型の第5の半導体領域12の内側に抵抗膜3が配置されている。この抵抗膜3はドレイン電極18と接続導体30との間に接続されている。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】 しきい値制御性を向上させつつ、絶縁体上に配置された電界効果型トランジスタ下にフィールドプレート電極を形成する。

【解決手段】 半導体基板1上には絶縁層2が形成され、絶縁層2には、単結晶半導体層3a、3bが積層され、単結晶半導体層3a、3b上には、メサ分離された単結晶半導体層5a、5bが絶縁層4を介してそれぞれ積層され、単結晶半導体層5a、5bには、Pチャンネル電界効果型トランジスタおよびNチャンネル電界効果型トランジスタを形成するとともに、単結晶半導体層3a、3bをフールドプレートとして機能させるとともに、不純物の極性または濃度が互いに異なるように構成する。

(もっと読む)

半導体装置とその製造方法、及び半導体装置の設計プログラム

【課題】オン電流の特性を向上させること

【解決手段】本発明に係る半導体装置1は、基板8上に形成された複数のPMOSトランジスタと、基板8上に形成された複数のNMOSトランジスタとを備える。複数のPMOSトランジスタは、基板8中に形成される素子分離構造20によって、互いに電気的に分離される。一方、複数のNMOSトランジスタは、互いに隣接して連続的に形成される。また、複数のNMOSトランジスタのうち少なくとも一組の隣接するNMOSトランジスタの間の領域において、基板8上にゲート構造30が形成される。このゲート構造30が接地されることによって、NMOSトランジスタに関する素子分離は実現される。

(もっと読む)

半導体装置およびその製造方法

【課題】 拡散層上にシリサイド膜を形成する時に、素子形成領域の面積増加なしに、素子分離膜と拡散層の境界部における接合リーク電流を低減する。

【解決手段】 シリコン基板101上に、多数の素子形成領域に区画する素子分離領域として、溝型の素子分離105が形成されている。この素子分離105の表面は素子形成領域のシリコン基板101の表面よりも低く、両者間には所定の高低差を有する段差部が形成されている。上記素子分離105により画成された素子形成領域には、拡散層領域111、その上部にシリサイドで構成された拡散層電極113bが形成されている。拡散層電極は、拡散層領域における境界端部上面を含み、溝型素子分離領域における境界端部上面を含まないように形成されることにより、素子分離と分離されている。素子分離105と素子形成領域との段差部側面には、段差部サイドウォール106が形成されている。

(もっと読む)

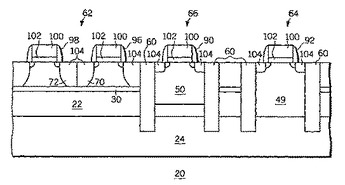

集積回路およびその製造方法

集積回路およびその製造方法が提供されている。集積回路(20)は、その結晶方位が<100>である第1領域(64、66)とその結晶方位が<110>である第2領域(66、64)を有するバルクシリコン基板(24)を含む。シリコンオンインシュレータの層(62)はバルクシリコン基板の一部を覆う。少なくとも1つの電界効果トランジスタ(96、98)はシリコンオンインシュレータの層(62)上に形成され、少なくとも1つのPチャネル電界効果トランジスタ(90、92)はその結晶方位が<110>である第2領域(66、64)に形成され、少なくとも1つのNチャネル電界効果トランジスタ(90、92)はその結晶方位が<100>である第1領域(64、66)に形成される。  (もっと読む)

(もっと読む)

半導体装置およびその製造方法

【課題】駆動能力が高く、かつ高集積化に適した半導体装置を提供する。

【解決手段】シリコン基板1上にシリコン酸化膜よりなる絶縁層3を介在して高抵抗n型ベース層5が形成されている。この高抵抗n型ベース層にはp−chMOSトランジスタ30が形成されている。このp−chMOSトランジスタ30は、溝6によるトレンチ分離により他の素子から電気的に分離されている。このp−chMOSトランジスタ30のp+ソース層9は、p+ドレイン層11の周囲を、たとえば楕円の平面形状で取囲むように形成されている。

(もっと読む)

半導体装置およびその製造方法

【課題】高耐圧トランジスタの特性を確保しながら低耐圧トランジスタの微細化ができる半導体装置および製造方法を提供する。

【解決手段】第1トランジスタ形成領域が、選択的に残されて第1素子分離絶縁膜2で分離され、第2トランジスタ形成領域が、選択的に酸化されて形成された第2素子分離絶縁膜3で分離され、第1素子分離絶縁膜2で分離された領域に、第1チャネル形成領域、第1ソースドレイン領域(12,13,14)、第1の膜厚の第1ゲート絶縁膜16および第1ゲート電極17を有する第1トランジスタTr1が構成され、第2素子分離絶縁膜3で分離された領域に、第2チャネル形成領域、第2ソースドレイン領域(32,41)、第1の膜厚より薄い第2の膜厚の第2ゲート絶縁膜(33,42)、第2ゲート電極(34,43)を有する第2トランジスタ(Tr3,Tr4)が構成されている。

(もっと読む)

半導体装置

【課題】フィールド反転の発生を防止し、微細化に有利な半導体装置を提供する。

【解決手段】半導体装置は、半導体基板21の主表面上にマトリクス状に設けられ、それぞれがゲート電極TGと、前記ゲート電極上に設けられたゲート電極コンタクト26と、ゲート幅方向に隣接する前記ゲート電極コンタクト上に設けられゲート幅方向の前記ゲート電極を電気的に接続する配線層27とを備えた複数の高耐圧系絶縁ゲート型電界効果トランジスタTRと、ゲート長方向およびゲート幅方向において隣接する前記トランジスタ間の素子分離領域STI上に設けられ、前記トランジスタの電流経路がオンとなるためにゲートに印加される電位と異なる導電型の電位または基準電位を前記素子分離領域に印加するシールド用ゲート31とを具備している。

(もっと読む)

1 - 20 / 20

[ Back to top ]