Fターム[5F048BG05]の内容

MOSIC、バイポーラ・MOSIC (97,815) | 絶縁体分離 (5,896) | 素子領域側面・底面を絶縁物で分離するもの (666)

Fターム[5F048BG05]の下位に属するFターム

複数MOS(CMOS)で一部のみ (116)

複数MOS(CMOS)ですべて (452)

Fターム[5F048BG05]に分類される特許

1 - 20 / 98

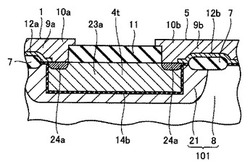

半導体装置

【課題】抵抗値が制御されることができる抵抗素子を有する半導体装置を提供する。

【解決手段】半導体装置は、半導体基板101と、絶縁膜14bと、半導体素子と、抵抗素子4tとを有する。絶縁膜14bは半導体基板101の少なくとも一部を被覆している。半導体素子は、半導体基板101の一部からなるチャネル領域と、電極とを有する。抵抗素子4tは、電極を流れる電流に対する抵抗となるように電極と電気的に接続され、かつ絶縁膜14bを介して半導体基板101上に設けられている。抵抗素子4tは半導体領域を含む。半導体基板101と抵抗素子4tとの間の電位差により半導体領域に空乏層が生じる。

(もっと読む)

半導体装置

【課題】高集積なCMOS SRAMを提供する。

【解決手段】第1の第1導電型半導体137と、第1の第1導電型半導体とは極性が異なる第1の第2導電型半導体104と、第1の第1導電型半導体と第1の第2導電型半導体との間に配置される第1の絶縁物112が一体となり基板に対して垂直に延びる1本の第1の柱と、

第1の第1導電型半導体の上に配置される第1の第2導電型高濃度半導体182と、第1の第1導電型半導体の下に配置される第2の第2導電型高濃度半導体141と、第1の第2導電型半導体の上に配置される第1の第1導電型高濃度半導体186と、第1の第2導電型半導体の下に配置される第2の第1導電型高濃度半導体143と、第1の柱を取り囲む第1のゲート絶縁物176と、第1のゲート絶縁物を取り囲む第1のゲート導電体167と、を有するインバータ501を用いてSRAMを構成する。

(もっと読む)

EL表示装置

【課題】開口率を向上することができるEL表示装置である。

【解決手段】薄膜トランジスタと、容量と、発光素子と、発光素子へ電流を供給することができる機能を有する配線と有するEL表示装置である。発光素子は、陰極と、陽極と、陰極と陽極との間に設けられたEL材料とを有し、容量は、第2の領域と、第2の領域上に第1の絶縁膜を介して設けられる第3の領域とを有する。第1の絶縁膜は、薄膜トランジスタのゲート絶縁膜となり、さらに容量の絶縁膜となることができる。

(もっと読む)

半導体装置の製造方法、半導体装置

【課題】SiCが用いられる半導体層中において、簡易な工程で再現性よく埋め込み絶縁層を形成する。

【解決手段】単結晶のSiC12の表面の温度を局所的に急激に上昇させ、その後で急激に冷却することによって、単結晶を局所的に非晶質化層30を形成することができる。この非晶質層30は、元の単結晶SiCの導電型や抵抗率に関わらず、高抵抗層(絶縁層)となる。このため、こうした非晶質層を埋め込み絶縁層と同様に使用することができる。このためには、(1)レーザー光を効率的に吸収する層100を局所的に半導体層の上に形成してからレーザー光を照射する、(2)レーザー光を局所的に半導体層に照射する、という2つの手段のいずれかを用いることができる。

(もっと読む)

半導体装置

【課題】高い開口率を有し、安定した電気特性を有する薄膜トランジスタを有する、信頼

性のよい表示装置を作製し、提供することを課題の一とする。

【解決手段】同一基板上に駆動回路部と、表示部(画素部ともいう)とを有し、当該駆動

回路部は、ソース電極及びドレイン電極が金属によって構成され且つチャネル層が酸化物

半導体によって構成された駆動回路用薄膜トランジスタと、金属によって構成された駆動

回路用配線とを有し、当該表示部は、ソース電極層及びドレイン電極層が酸化物導電体に

よって構成され且つ半導体層が酸化物半導体によって構成された画素用薄膜トランジスタ

と、酸化物導電体によって構成された表示部用配線とを有する。

(もっと読む)

半導体装置の製造方法、半導体装置、SOI基板の製造方法およびSOI基板

【課題】SOI基板のチャージ蓄積による不良を抑制する。

【解決手段】まず、シード基板100の一面に、シード基板100の表面と同一面を形成するように、開口部220を有する絶縁層200を形成する(絶縁層形成工程)。次いで、シード基板100の一面に接するように、支持基板300を貼り合せる(貼り合せ工程)。次いで、シード基板100または支持基板300の一方を薄板化することにより、当該薄板化基板からなる半導体層120を形成する(半導体層形成工程)。以上の工程により、SOI基板を準備する。次いで、半導体層120に半導体素子60を形成する(半導体素子形成工程)。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】配線層中の配線をゲート電極として使用し、かつ拡散防止膜と同一層にゲート絶縁膜を有している半導体素子を有する半導体装置において、拡散防止膜の機能を損なうことなく、半導体素子のオン抵抗を低くする。

【解決手段】第1配線層150を構成する絶縁層の表層には、第1配線154及びゲート電極210が埋め込まれている。第1配線層150と第2配線層170の間には、拡散防止膜160が形成されている。ゲート絶縁膜230は、拡散防止膜160のうちゲート電極210と重なる領域及びその周囲の上面に凹部を形成し、この部分を薄くすることにより、形成されている。

(もっと読む)

半導体基板およびその製造方法、その半導体基板を用いた半導体装置

【課題】実施形態は、異なる種類の半導体素子のそれぞれに適合した厚さを有する半導体層が1つの絶縁膜上に設けられた半導体基板およびその製造方法、その半導体基板を用いた半導体装置を提供する。

【解決手段】実施形態に係る半導体基板10は、第1絶縁層5と、前記第1絶縁層の上に設けられた半導体層7とを有する半導体基板であって、前記半導体層の中に選択的に設けられ、前記半導体層の表面に平行に延在し、その延在方向の長さが前記第1絶縁層よりも短い第2絶縁層13と、前記半導体層の表面から前記第1絶縁膜に至る深さに延設され、前記半導体層の前記第2絶縁層を含む部分と、前記半導体層の残りの部分と、を電気的に分離する第3絶縁層15と、を備える。

(もっと読む)

半導体基板または半導体装置の製造方法

【課題】平板状空洞を形成する際におけるホール半径Rと、ホールとホールの最短距離Sのプロセスマージンを広げ、信頼性の高い半導体装置の製造方法を提供すること。

【解決手段】半導体基板1の表面にホール4を複数形成し、非酸化性雰囲気のアニール処理により、該半導体基板1の表面を半導体の表面マイグレーションを利用して平坦化し、基板内部に平板状空洞6を形成する際に、前記ホール4の開口部が閉じる前に半導体のソースガスを供給する。

(もっと読む)

電界効果トランジスタ

【課題】急峻なS値特性を有するとともに、ソース/ドレイン領域が同じ導電型となる対称構造を有する電界効果トランジスタを提供する。

【解決手段】本実施形態による電界効果トランジスタは、半導体層と、前記半導体層に離間して設けられたソース領域およびドレイン領域と、前記ソース領域と前記ドレイン領域との間の前記半導体層上に設けられたゲート絶縁膜と、前記ゲート絶縁膜上に設けられたゲート電極と、前記ソース領域および前記ドレイン領域側の前記ゲート電極の少なくとも一方の側面に設けられた高誘電体のゲート側壁と、を備え、前記ソース領域および前記ドレイン領域は前記ゲート電極の対応する側面から離れている。

(もっと読む)

半導体装置及びその製造方法

【課題】電子及び正孔の移動度を向上させたSOI構造のCMOSの提供

【解決手段】Si基板1上にシリコン窒化膜2及びシリコン酸化膜3を介して貼り合わせられ、島状に絶縁分離されたGe層8(第2の半導体層)が設けられ、このGe層8に高濃度のソースドレイン領域(14、15)が形成されたPチャネルのMISFETと、Si基板1上にシリコン窒化膜2及び一部に空孔5を有するシリコン酸化膜3を介して、空孔5直上の歪みSi層7を挟み、左右にSiGe層6を有する構造からなるエピタキシャル半導体層(第1の半導体層)が島状に絶縁分離されて設けられ、歪みSi層7には概略チャネル領域が形成され、SiGe層6には概略高濃度及び低濃度のソースドレイン領域(10、11、12,13)が形成されたNチャネルのMISFETとから構成したCMOS。

(もっと読む)

半導体装置およびその製造方法

【課題】 本発明は、より寄生容量の少ない素子の実現が可能な素子分離構造を有する半導体装置およびその製造方法を提供することにある。

【解決手段】 SOI基板上に形成される半導体装置は、素子分離領域に形成される素子分離溝(空洞)17と、半導体層11と支持基板13の間に介在する埋め込み絶縁層の一部に素子分離溝(空洞)17に接する空洞領域20を有する。

【効果】寄生容量を低減でき、また、素子の耐圧を高めることができる。

(もっと読む)

半導体基板の製造方法及び半導体装置の製造方法

【課題】信頼性の高いLocalSOI構造を有する基板を低コストで作製する。

【解決手段】第1の半導体からなる基板10上に、結晶成長により第2の半導体からなる層及び前記第1の半導体からなる層12を順次形成する半導体層形成工程と、前記第2の半導体からなる層をエッチングにより除去し開口領域13を形成する開口領域形成工程と、前記開口領域に、窒化物膜、炭化物膜又は酸化物膜を含む材料により形成される酸化遅延膜14を前記開口領域の入口における膜厚が所定の膜厚となるように成膜する酸化遅延膜成膜工程と、前記第1の半導体からなる基板及び前記第1の半導体からなる層の前記第1の半導体の一部を熱酸化することにより、前記開口領域に熱酸化膜15を形成する熱酸化工程とを有することを特徴とする、Local SOI半導体基板の製造方法。

(もっと読む)

半導体基板の作製方法

【課題】半導体基板の欠陥を低減する。また、歩留まり高く欠陥の少ない半導体基板を作製する。また、歩留まり高く半導体装置を作製する。

【解決手段】支持基板に酸化絶縁層を介して半導体層を設け、該半導体層の端部における、支持基板及び酸化絶縁層の密着性を高めた後、半導体層の表面の絶縁層を除去し、半導体層にレーザ光を照射して、平坦化された半導体層を得る。半導体層の端部において、支持基板及び酸化絶縁層の密着性を高めるために、半導体層の表面から、レーザ光を照射する。

(もっと読む)

半導体装置及び駆動方法

【課題】絶縁層上に形成された部分空乏型のトランジスターにおいて、ヒストリー効果を低減し、なおかつ高いON/OFF比、及び急峻なサブスレッショルド特性を実現する。

【解決手段】絶縁層上の半導体層に形成された第1導電型のソース領域、第1導電型のドレイン領域、及び、第2導電型のボディ領域と、第1ゲート絶縁膜と、第1ゲート電極と、を含む部分空乏型の第1トランジスターと、絶縁層上の半導体層に形成された第2導電型のソース領域、第2導電型のドレイン領域、及び、第1導電型のボディ領域と、第2ゲート絶縁膜と、第2ゲート電極と、を含む第2トランジスターと、を具備し、第1トランジスターの第2導電型のボディ領域は、第2トランジスターの第2導電型のソース領域及び第2導電型のドレイン領域の内の一方に接続されている。

(もっと読む)

半導体装置及びその製造方法

【課題】 MOSトランジスタの製造工程を削減し、さらには寄生MOSの敷居値電圧が低下するのを抑制する。

【解決手段】 本発明の半導体装置の製造方法は、ゲート電極形成後にウェル拡散層とは逆導電型のチャネル形成用の不純物をイオン注入する製造方法において、フィールド酸化膜30にチャネル形成用の不純物をイオン注入しない製造方法である。従って、本発明の半導体装置は、フィールド酸化膜30にチャネル形成用の不純物がイオン注入されていない構造となる。

(もっと読む)

半導体装置

【目的】高耐圧NMOSFETなどのレベルシフト素子から素子分離溝越しに隣接した高電位浮遊領域への高電位配線を、高耐圧NMOSFETの耐圧低下や層間絶縁膜の破壊および素子分離溝の分離耐圧劣化を招くことなく、形成できる半導体装置を提供する。

【解決手段】高電位配線9の直下にnドレインバッファ層10と接してp-拡散層11とこれに接するp+拡散層12を形成することで、高電位配線9が横切る絶縁膜44aの電界強度を低下できる。絶縁膜44aの電界強度を低下させることで、高耐圧NMOSFET20の耐圧低下や層間絶縁膜5の破壊および素子分離溝(トレンチ4a)の分離耐圧劣化を防止できる。

(もっと読む)

半導体装置、半導体基板、及び半導体基板の処理方法

【課題】表面が(111)面以外であるシリコン層と、表面が(0001)面である窒化物半導体層とを基板に設け、かつシリコンと窒化物半導体の線膨張係数の違いに起因した応力を小さくする。

【解決手段】まずSOI(Silicon On Insulator)基板を準備する。SOI基板は、表面が(111)面であるシリコン基板100上に絶縁層120及びシリコン層200を積層した基板である。シリコン層200は、表面が(111)面以外の面方位である。次いで、絶縁層120及びシリコン層200に、底面にシリコン基板100が露出している開口部201を形成する。次いで、開口部201内にIII族の窒化物半導体層300を形成する。

(もっと読む)

半導体デバイス及びその形成方法

【課題】応力ライナによるコンタクト形成の問題が起きない、相補型金属酸化膜半導体(CMOS)デバイスの製造方法を提供する。

【解決手段】シリコン基板層上の二酸化シリコン層102と、凹んだソース/ドレイン・トレンチを有する相補型金属酸化膜半導体(CMOS)デバイスを準備し、凹んだソース/ドレイン・トレンチ内に窒化物応力ライナ104を堆積し、その上に酸化物層106を堆積する。CMOSデバイスをハンドリング・ウェハ上に置きシリコン基板層を除去し二酸化シリコン層102をエッチングしてソース/ドレイン領域170の一部に当接する開口部を形成しコンタクト180を形成する。

(もっと読む)

半導体装置の駆動方法、表示装置の駆動方法、及び電子機器の駆動方法

【課題】表示装置において、表示素子に電流を供給するトランジスタの特性が画素ごとに

ばらつくことによって生ずる輝度ムラが、表示装置の画質向上の足かせとなっていた。

【解決手段】ソース信号線より画素に入力される映像信号は、表示素子に電流を供給する

ためのトランジスタをダイオード接続とし、当該ダイオード接続されたトランジスタのゲ

ートに所望の電位が印加される。ここで、ダイオード接続したトランジスタにおいて、そ

のソース・ドレイン間には、トランジスタのしきい値電圧に応じた電位差を取得する。そ

の結果、駆動用トランジスタのゲート電極には、映像信号にしきい値電圧に応じた電位差

のオフセットをかけた電位を印加することができる。

(もっと読む)

1 - 20 / 98

[ Back to top ]